# HybridSA: GPU Acceleration of Multi-pattern Regex Matching using Bit Parallelism

ALEXIS LE GLAUNEC, Rice University, USA

LINKUN KONG, Rice University, USA

KONSTANTINOS MAMOURAS, Rice University, USA

Multi-pattern matching is widely used in modern software for applications requiring high throughput such as protein search, network traffic inspection, virus or spam detection. Graphics Processor Units (GPUs) excel at executing massively parallel workloads. Regular expression (regex) matching is typically performed by simulating the execution of deterministic finite automata (DFAs) or nondeterministic finite automata (NFAs). The natural implementations of these automata simulation algorithms on GPUs are highly inefficient because they give rise to irregular memory access patterns.

This paper presents HybridSA, a heterogeneous CPU-GPU parallel engine for multi-pattern matching. HybridSA uses bit parallelism to efficiently simulate NFAs on GPUs, thus reducing the number of memory accesses and increasing the throughput. Our bit-parallel algorithms extend the classical shift-and algorithm for string matching to a large class of regular expressions and reduce automata simulation to a small number of bitwise operations. We have developed a compiler to translate regular expressions into bit masks, perform optimizations, and choose the best algorithms to run on the GPU. The majority of the regular expressions are accelerated on the GPU, while the patterns that exhibit random memory accesses are executed on the CPU in parallel. We evaluate HybridSA against state-of-the-art CPU and GPU engines, as well as a hybrid combination of the two. HybridSA achieves between 4 and 60 times higher throughput than the state-of-the-art CPU engine and between 4 and 233 times better than the state-of-the-art GPU engine across a collection of real-world benchmarks.

CCS Concepts: • Theory of computation → Formal languages and automata theory; Regular languages; • Software and its engineering → Semantics.

Additional Key Words and Phrases: regular expressions, regex matching, CUDA, shift-and algorithm, bit parallelism

## ACM Reference Format:

Alexis Le Glaunec, Lingkun Kong, and Konstantinos Mamouras. 2024. HybridSA: GPU Acceleration of Multi-pattern Regex Matching using Bit Parallelism. *Proc. ACM Program. Lang.* 8, OOPSLA2, Article 331 (October 2024), 30 pages. <https://doi.org/10.1145/3689771>

## 1 Introduction

Regular expressions [Kleene 1956] and finite-state automata (e.g., DFAs and NFAs) describe patterns over sequences and have found applications in numerous domains. They have been used for the lexical analysis of programs [Johnson et al. 1968] during compilation, the search of words and patterns in text editors [Thompson 1968], and bibliographic search [Aho and Corasick 1975]. Regular patterns are also used in network security [Yu et al. 2006] to search for intrusion signatures

---

Authors' Contact Information: [Alexis Le Glaunec](#), Rice University, Houston, USA, alexis.leglaunec@rice.edu; [Lingkun Kong](#), Rice University, Houston, USA, klk@rice.edu; [Konstantinos Mamouras](#), Rice University, Houston, USA, mamouras@rice.edu.

This work is licensed under a Creative Commons Attribution 4.0 International License.

© 2024 Copyright held by the owner/author(s).

ACM 2475-1421/2024/10-ART331

<https://doi.org/10.1145/3689771>

in network traffic, in bioinformatics [Roy and Aluru 2016] for describing protein, RNA, or DNA sequences, and in runtime verification [Bartocci et al. 2018] for specifying safety properties.

Due to the broad applicability of regular patterns, many software tools exist for solving the regular pattern matching problem. These tools are called *regex engines*. Many software implementations are meant to run on CPUs, including the widely-used PCRE [The PCRE2 Developers 2024], grep [Grep 2022], RE2 [RE2 2023], and Hyperscan [Wang et al. 2019]. Given the widespread adoption of dedicated general-purpose GPUs, it is notable that there are only a few efforts for implementing regex matching on GPUs [Avalle et al. 2016; Cascarano et al. 2010; Liu et al. 2020; Yu and Becchi 2013; Zu et al. 2012]. One of the main obstacles in taking advantage of GPUs for regular pattern matching is that the typical algorithms for automata simulation (DFA- or NFA-based) involve highly irregular memory access patterns when reading the transition function/relation from memory. These memory access patterns are not a good fit for GPUs, which require very specific and regular memory accesses to operate efficiently.

In this work, we show that it is possible to leverage the massive parallelism of modern GPUs for multi-pattern regex matching by partitioning the set of patterns into two subsets: (1) those that will execute on the CPU and (2) those that will execute on the GPU. The main idea is that for regular expressions of certain simpler forms, it is possible to implement extremely efficient NFA simulation algorithms that are a great fit for GPUs. This partitioning enables much more effective use of the available hardware, namely the CPU and the GPU. By not trying to use the GPU for patterns that are inherently difficult for the GPU execution model, we can effectively balance the load between the CPU and the GPU and achieve a substantial performance improvement.

**Contributions.** In this paper, we make the following main contributions:

- (1) We show that it is possible to implement efficient variants of the classical shift-and algorithm [Baeza-Yates and Gonnet 1992] for string searching on GPUs. The algorithms that we consider can be used to parallelize and accelerate multi-pattern matching for a significant portion of regular patterns that arise in practice. Our algorithms use *bit parallelism* to perform  $m$  NFA transitions with a constant number of logical/arithmetic operations, where  $m$  is the width of the GPU registers.

- (2) We implement a *compiler* that takes as input a set of regular expressions, identifies the subset that can efficiently execute on the GPU, and then chooses a set of specialized GPU kernels for them to maximize the performance. The compiler performs pattern rewriting optimizations and produces for each kernel a compact binary representation of the NFAs that it will execute. We call this representation an *NFA database*. During execution, the NFA database is loaded into the global memory of the GPU, and the massively parallel execution of the NFAs is initiated.

- (3) We perform an experimental evaluation of our implementation for multi-pattern matching by comparing it against the state-of-the-art regex engines Hyperscan [Wang et al. 2019] (CPU-based) and HotStart [Liu et al. 2020] (GPU-based). Our results show that our hybrid CPU-GPU approach is around 4 to 233 times faster than other tools.

The use of bit parallelism in NFA simulation (using arithmetic and bitwise operations) has been explored in several prior works (see, e.g., [Baeza-Yates and Gonnet 1992], [Wu and Manber 1992], [Navarro 2001], [Navarro and Raffinot 2002], and [Wang et al. 2019]). The main *novelties* in this paper concern (i) the careful GPU implementation of bit parallelism to altogether avoid thread divergence and uncoalesced memory accesses and (ii) the use of rewriting optimizations that enable the use of faster GPU kernels.

**Paper Outline.** Section 2 provides an overview of the necessary definitions and an exposition of NFA simulation using bit vectors for representing sets of states. In Section 3, we describe the GPU

implementation (in the CUDA programming model) of several variants of the shift-and algorithm for bit-parallel NFA execution. Section 4 describes the partitioning of the pattern set between the GPU and the CPU, how the GPU kernels are chosen, and some optimizing transformations that can speed up NFA execution on the GPU. In Section 5, we compare our tool (called HybridSA) with Hyperscan [Wang et al. 2019] and HotStart [Liu et al. 2020]. Section 6 contains a discussion of related work. We conclude in Section 7 with a brief summary of our main contributions.

## 2 Preliminaries

In this section, we give a brief overview of concepts that we will need in the later development: regular expressions, homogeneous NFAs, and the Glushkov construction. We also give a description of the algorithm for simulating the execution of homogeneous NFAs using bit vectors to represent sets of active NFA states.

Let  $\Sigma$  be a finite alphabet. A *regular expression* (or *regex*) over  $\Sigma$  is given by the grammar

|                    |                           |

|--------------------|---------------------------|

| $r ::= \epsilon  $ | [empty string]            |

| $\sigma  $         | [character class]         |

| $r \cdot r  $      | [concatenation]           |

| $r r  $            | [nondeterministic choice] |

| $r^*  $            | [Kleene star]             |

| $r\{m, n\}$        | [bounded repetition]      |

where  $\sigma \subseteq \Sigma$  is a predicate over the alphabet and  $m, n$  are natural numbers with  $m \leq n$ . The expression  $r\{m, n\}$  is called a *bounded repetition* and describes the repetition of  $r$  from  $m$  to  $n$  times. We write  $r\{n\}$  for  $r\{n, n\}$ . The concatenation symbol is sometimes omitted, i.e., we write  $r_1 r_2$  instead of  $r_1 \cdot r_2$ . The *interpretation* of a regex  $r$  is a language  $\mathcal{L}(r) \subseteq \Sigma^*$ , which is defined in the standard way.

A regular expression can be transformed into an equivalent nondeterministic finite automaton (NFA). We will use Glushkov's construction [Glushkov 1961] to convert a regular expression into an NFA. In contrast to Thompson's construction [Thompson 1968], Glushkov's construction results in  $\epsilon$ -free automata that are also *homogeneous*, i.e., all incoming transitions of a state are labeled with the same predicate over the alphabet.

**Definition 1 (Homogeneous NFA).** Let  $\Sigma$  be a finite alphabet. A *homogeneous nondeterministic finite automaton* with input alphabet  $\Sigma$  is a tuple  $\mathcal{A} = (Q, L, \Delta, I, F)$ , where

- $Q$  is a finite set of (*control*) *states*,

- $L : Q \rightarrow \mathcal{P}(\Sigma)$  is a labeling function that maps each state to a character class,

- $\Delta : Q \rightarrow \mathcal{P}(Q)$  is the *transition relation*,

- $I \subseteq Q$  is the set of *initial states*, and

- $F \subseteq Q$  is the set of *final states*,

where  $\mathcal{P}$  is the powerset operation.

Given a set of regular expressions and an input string, the multi-pattern matching problem involves simulating a set of regular expressions over the same input text and reporting the total number of matches. Multi-pattern matching is an embarrassingly parallel problem as the NFAs can be executed independently over many independent inputs. A standard approach to solve the multi-pattern matching problem is to execute each NFA independently. This is shown in Algorithm 1, where a Boolean transition matrix is used to represent the transitions of the automaton.

---

**Algorithm 1:** Simulation of the execution of a homogeneous NFA

---

```

1 Kernel NfaSimulation(init, final, labels, delta, text):

// delta is the Boolean transition matrix of the NFA

// i.e., delta[i][j] = 1 iff there is a transition from state i to state j

2 states  $\leftarrow 0\ldots0$  // n-bit vector of active states, where n is the # NFA states

3 nMatches  $\leftarrow 0$  // number of matches

4 for c in text do // left-to-right pass over input text

5   next  $\leftarrow$  init // init states are always active

6   next  $\leftarrow$  next OR (states · delta) // execute transition by matrix multiplication

7   states  $\leftarrow$  next AND labels[c] // keep active states with the right label

8   nMatches  $\leftarrow$  nMatches + ((states AND final)  $\neq 0\ldots0$ )

9 return nMatches

```

---

**Notation (Bit Vectors).** We will use the notation  $x_{n-1}x_{n-2}\dots x_2x_1x_0$  for an *n*-bit vector. The *i*-th position of the bit vector has the value  $x_i$ . If we think of the bit vector as a binary representation of a number (e.g., a GPU register), the leftmost bit is the most significant and the rightmost bit is the least significant. The *left shift* operation  $\ll$  shifts each bit to the left and inserts 0 in the least significant position. For example,  $x_3x_2x_1x_0 \ll 1 = x_2x_1x_00$  and  $x_3x_2x_1x_0 \ll 2 = x_1x_000$ .

We sometimes use the term *(bit) mask* to refer to a bit vector. This is because they are commonly used as OR masks (to set specific bits to 1) or as AND masks (to set specific bits to 0).

If  $v$  is a  $1 \times n$  matrix (i.e., a row vector) and  $M$  is an  $n \times n$  matrix, then their product  $v \cdot M$  is a  $1 \times n$  matrix, given by  $(v \cdot M)(j) = \sum_{i=0}^{n-1} v(i) \cdot M(i, j)$  for every  $j = 0, 1, \dots, n - 1$ . We will use this operation of *vector-matrix multiplication* for the product of a state bit vector with the Boolean transition matrix of an NFA.

The arguments *init, final, labels* and *delta* of NfaSimulation in Algorithm 1 represent a homogeneous NFA  $\mathcal{A} = (Q, L, \Delta, I, F)$  with  $n = |Q|$  states. Assume w.l.o.g. that  $Q = \{0, 1, \dots, n - 1\}$ . Both *init* and *final* are *n*-bit vectors that represent the sets *I* and *F* respectively. E.g., for every  $q \in Q$ , we have that  $init(q) = 1$  iff  $q \in I$ . The argument *labels* is an array of *n*-bit vectors that represents *L* as follows:  $labels[c](q) = 1$  iff  $c \in L(q)$ , for every  $c \in \Sigma$  and  $q \in Q$ . Finally, *delta* is an  $n \times n$  matrix that satisfies:  $delta(q, q') = 1$  iff  $q' \in \Delta(q)$ , for all  $q, q' \in Q$ .

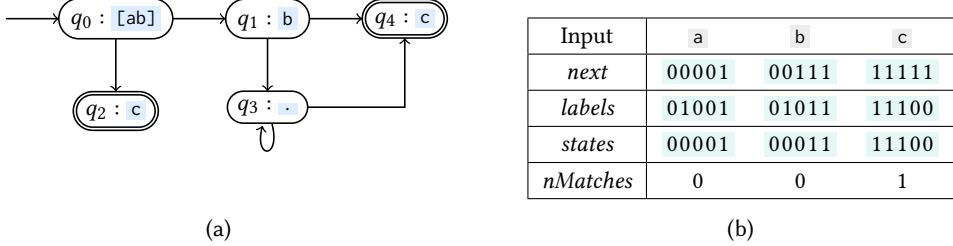

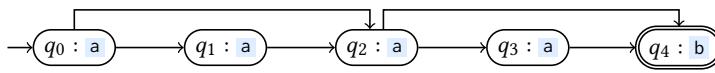

**Example 2.** Fig. 1 presents the execution of Algorithm 1 for the regex  $r_1 = [ab](c|b.*c)$  over the input stream abc. Notice that we label the states (instead of the edges) with character classes, as the automaton is homogeneous. The character masks for a, b and c are 01001, 01011, and 11100 respectively. For all other letters, the character mask is 01000 as state  $q_3$  is labeled with ., which matches any character. The mask for the set of initial states  $\{q_0\}$  (resp., set of final states  $\{q_2, q_4\}$ ) is 00001 (resp., 10100). After reading the character a, we perform vector-matrix multiplication (line 6) using the transition matrix *delta*, which gives

$$next = init \text{ OR } (states \cdot delta) = 00001 \text{ OR } (00000 \cdot delta) = 00001.$$

Then, we compute *states*, the set of states activated that also match the current input letter with

$$states = next \text{ AND } labels[a] = (00001 \text{ AND } 01001) = 00001.$$

This means that state  $q_0$  is active. We compute the intersection between *states* and *final* in

$$is\_final = (states \text{ AND } final) \neq 00000 = (00001 \text{ AND } 10100) \neq 00000 = \text{false}.$$

Thus, we have no match. In the next round, we consume character b. Right after line 6, we have that  $next = (00001 \text{ OR } (00001 \cdot delta)) = 00111$ . This is because the successors of state  $q_0$  are states

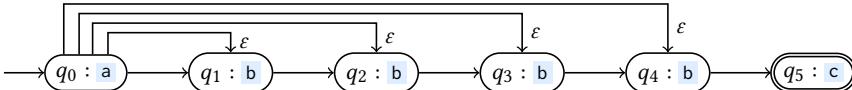

Fig. 1. NFA execution for the pattern  $r_1 = [\text{ab}](\text{c}|\text{b}.\text{*}\text{c})$  over the input string `abc`.

$q_1$  and  $q_2$ . Then, we have that  $\text{states} = (00111 \text{ AND } 01011) = 00011$ , corresponding to the set of active states  $\{q_0, q_1\}$  that both match letter  $b$ . Since  $\text{is\_final} = ((00011 \text{ AND } 10100) \neq 00000) = \text{false}$ , we still have no match. For the last character  $c$ ,  $\text{next} = (00001 \text{ OR } (00011 \cdot \text{delta})) = 11111$ , which means that all states are active in  $\text{next}$ . We compute  $\text{states} = (11111 \text{ AND } 11100) = 11100$  and obtain that  $\text{is\_final} = ((11100 \text{ AND } 10100) \neq 00000) = \text{true}$ , corresponding to a match for state  $q_4$  which is final. Thus, we report a match and increment  $nMatches$ .

For a regular expression  $r$  over  $\Sigma$ , a string  $w \in \Sigma^*$ , and a position  $j = 0, 1, \dots, |w|$ , we say that  $r$  has a *match* at position  $j$  in  $w$  if the substring  $w[i..j]$  is in  $\mathcal{L}(r)$  for some  $i = 0, \dots, j$ . We define the function  $\llbracket r \rrbracket : \Sigma^* \rightarrow \mathbb{N}$  as follows:  $\llbracket r \rrbracket(w)$  is equal to the size (i.e., cardinality) of the set

$$\{j \in \mathbb{N} \mid \text{there is } i \text{ s.t. } 0 \leq i \leq j \leq |w| \text{ and } w[i..j] \in \mathcal{L}(r)\}.$$

In other words,  $\llbracket r \rrbracket(w)$  is the number of positions  $j$  for which there is a match for  $r$  whose right endpoint is  $j$  (the left endpoint can be any position  $i \leq j$ ).

**Problem 3 (Multi-Pattern Matching).** Let  $\Sigma$  be a finite alphabet,  $r_0, r_1, \dots, r_{k-1}$  be a sequence of  $k$  regular expressions over  $\Sigma$ , and  $w$  be a finite string over  $\Sigma$ . For every  $i = 0, 1, \dots, k-1$  compute the number  $\llbracket r_i \rrbracket(w)$  of matches for the pattern  $r_i$ .

Notice that we are considering a computational problem that is more general than purely Boolean pattern matching. We choose this problem in order to have a more direct comparison with the GPU engine HotStart (see Section 5).

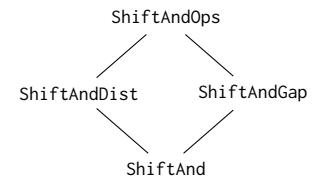

### 3 Overview of HybridSA

HybridSA uses bit parallelism to simulate NFA transitions more effectively by taking advantage of the simple matrix structure of the NFAs for real-world regexes. In this section, we present four families of kernels used in HybridSA to accelerate regexes on the GPU: ShiftAnd, ShiftAndGap, ShiftAndDist, and ShiftAndOps. We also present a solution to the multi-pattern matching problem (which is embarrassingly parallel) using the CUDA programming model.

#### 3.1 Shift-And Algorithm

Shift-And [Baeza-Yates and Gonnet 1992] is a bit-parallel algorithm that uses bitwise operations to simulate the execution of automata. It consists of two steps: (1) preprocessing of the pattern to derive bit masks that encode the NFA for the pattern, and (2) matching over the input text. An important restriction is that the pattern length must be smaller than the register size (32 bits on the GPU). Shift-And can be viewed as the simulation of a homogeneous automaton, where the states can be placed in order  $q_0, q_1, \dots, q_{n-1}$  on a line and each transition is from a state  $q_i$  to a neighboring state  $q_{i+1}$ . This transition pattern does not require the matrix multiplication operation seen in Algorithm 1. In fact, matrix multiplication can be replaced by a bitwise shift operation. Compared

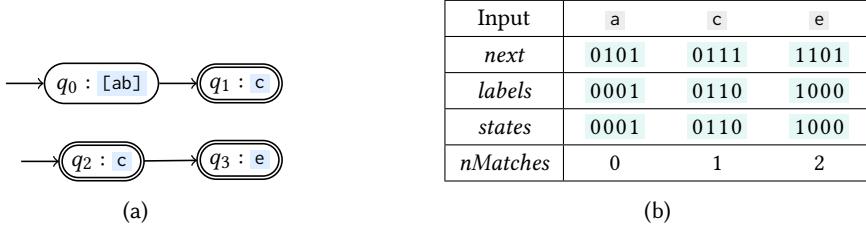

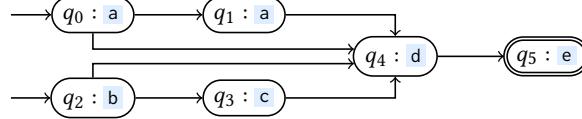

Fig. 2. Shift-And execution for the pattern  $r = [\text{ab}]\text{c}|\text{ce}?$  over the input string `ace`.

to Algorithm 1, the Shift-And algorithm can only encode transitions of the form  $(i) \rightarrow (i+1)$ . In particular, it cannot simulate back edges, i.e., transitions of the form  $(i) \rightarrow (j)$  where  $j \leq i$ .

**Example 4.** Consider the regex  $r = [\text{ab}]\text{c}|\text{ce}?$ . The automaton  $\mathcal{A}_1$  of Fig. 2a recognizes the language of  $r$ . The main idea of the Shift-And algorithm is to execute all the transitions  $(i) \rightarrow (i+1)$  with arithmetic and bitwise operations. The initial (resp. final) mask is  $maskInitial = 0101$  (resp.  $maskFinal = 1110$ ) and encodes the positions of the initial (resp. final) states. After consuming the character `a`, we start by performing the transitions with

$$next = (states \ll 1) \text{ OR } maskInitial = (0000 \ll 1) \text{ OR } 0101 = 0101.$$

Compared to Example 2, we have replaced matrix multiplication with a shift left operation. Then, we compute the active states that match letter `a` with

$$states = next \text{ AND } labels[\text{a}] = (0101 \text{ AND } 0001) = 0001.$$

This means that the initial state  $q_0$  is active. To check if there is a match, we compute the Boolean test  $((states \text{ AND } maskFinal) \neq 0000)$ , which is equal to false. So, there is no match.

After consuming letter `c`, we have  $next = (0001 \ll 1) \text{ OR } 0101 = 0111$ . We compute  $states = (0111 \text{ AND } 0110) = 0110$ . As  $is\_final = ((0110 \text{ AND } 1110) \neq 0000) = \text{true}$ , we report a match. Finally, after consuming letter `e`, we have  $next = (0110 \ll 1) \text{ OR } 0101 = 1101$ ,  $states = (1101 \text{ AND } 1000) = 1000$ , and  $is\_final = ((1000 \text{ AND } 1110) \neq 0000) = \text{true}$ .

### 3.2 Shift-And on a GPU

CUDA devices consist of single-instruction, multiple threads (SIMT) processors called *Streaming Multiprocessors* (34 on RTX 4060Ti). Each multiprocessor has a limited number of 32-bit *registers* (65 K registers per SM), *shared memory* that is local to a multiprocessor (100 KB on RTX 4060Ti) and *global memory* that is shared among the multiprocessors (8 GB on RTX 4060Ti). CUDA threads are executed on a multiprocessor, 32 threads at a time, in a CUDA *warp*. Within a warp, all 32 threads execute the same instruction at every step. CUDA warps are grouped in CUDA *thread blocks*, which are scheduled to the device's multiprocessors and executed in parallel. To execute code on the GPU, programmers implement functions called CUDA *kernel*s using a variant of C++. Each kernel execution is parameterized by (1) the number of CUDA thread blocks to execute in parallel, and (2) the number of threads per CUDA thread block. The organization of all threads of a kernel in blocks is referred to as the *thread grid*. All threads created during kernel invocation run the same piece of code. They are differentiated by using the special variables `blockIdx`, which specifies the block identifier of the current thread, and `threadIdx`, which specifies the current thread identifier within its block. More information about the CUDA programming model can be found in [NVidia 2024].

We propose an efficient CUDA implementation of the Shift-And algorithm for the embarrassingly parallel multi-pattern matching problem. In our algorithm, each CUDA thread simulates the

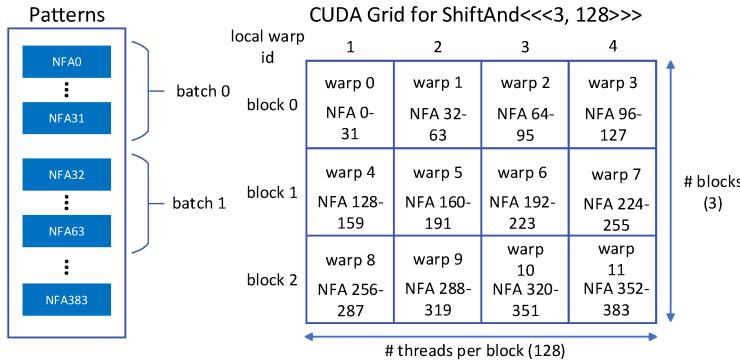

Fig. 3. Layout of the NFAs on the GPU for a grid of size (3,128).

execution of one NFA. This means that a warp, which is a collection of 32 threads, executes a group of 32 NFAs, which we call a *batch*. Fig. 3 shows the layout of the Shift-And NFA batches in the CUDA grid. Assuming that our input pattern set consists of  $n$  regexes, each regex and its corresponding Glushkov NFA is uniquely determined by a number  $i$  in the range  $0, 1, \dots, n - 1$ . We call this the *global NFA identifier* of the automaton. The  $n$  NFAs are grouped into  $\lceil n / \text{N\_NFAS\_PER\_BATCH} \rceil$  batches, where  $\text{N\_NFAS\_PER\_BATCH} = 32$ . The NFA with global identifier  $i$  is placed in the batch with identifier  $\lfloor i / \text{N\_NFAS\_PER\_BATCH} \rfloor$  and it has a batch-local identifier  $j = i \bmod \text{N\_NFAS\_PER\_BATCH}$ , which we call a *local NFA identifier*. The data that describes the NFAs of a batch is organized in the structure `Batch_SA` (see below). For  $T = \text{u32}$  (type of GPU registers), the size of the `Batch_SA` structure is equal to  $2 \cdot \text{N\_NFAS\_PER\_BATCH} \cdot \text{sizeof}(\text{u32}) + 256 \cdot \text{N\_NFAS\_PER\_BATCH} \cdot \text{sizeof}(\text{u32}) = 2 \cdot 32 \cdot 4 + 256 \cdot 32 \cdot 4 \approx 32 \text{ KB}$  stored in global memory for a given batch. For each NFA, this structure contains the mask of initial states, the mask of final states, and the mask for each character of the input alphabet. The data in `Batch_SA` uses a carefully chosen layout to ensure all thread accesses in a warp are coalesced.

```

template<typename T> struct Batch_SA {

T masks_initial[N_NFAS_PER_BATCH]; // masks for initial states

T masks_final[N_NFAS_PER_BATCH]; // masks for final states

T masks_char[N_CHARS][N_NFAS_PER_BATCH]; // masks for states that match each character

};

```

More precisely, the initial and final masks are 1D arrays indexed by a local NFA id (index 0 to 31) for a given batch. The character mask is a 2D array stored in a character-first order. The purpose of this layout is to have coalesced accesses when reading the character mask for the current input character. All `Batch_SA` arrays are parameterized by a type  $T$  that specifies the data type used to encode sets of states (it can be something other than 32-bit, the register size of the GPU). Thus, Shift-And can be extended to any data type implementing the shift left operation ( $\ll$ ), bitwise or (OR), bitwise and (AND), and the equality operator ( $=$ ).

Algorithm 2 presents pseudocode for the Shift-And kernel. We will use the example of a problem instance with 384 NFAs to explain the algorithm. We will use 384 CUDA threads to execute the NFAs in parallel. These threads will be organized in a thread grid with  $M = 3$  CUDA blocks and  $N = 128$  threads per block. This means that there will be 4 warps per block. Notice that  $M \cdot N = 384$ . We invoke the kernel with `ShiftAnd<<<M,N>>>`. The parameters inside the angled brackets define the CUDA grid dimension which is of size  $M \times N = 384$  in this example. Fig. 3 shows the mapping of the NFAs onto the CUDA grid. A batch (32 NFAs) is executed by a CUDA warp (32 threads) and a

**Algorithm 2:** Shift-And on the GPU

---

```

1 Kernel ShiftAnd<T>(output, batches, text):

2   // Each thread of the grid handles the execution of exactly one NFA

3   // blockId is the block identifier in the current grid (blockIdx.x in CUDA)

4   // threadId is the thread identifier within the current block (threadIdx.x in CUDA)

5   // N_THREADS_PER_WARP = 32 is a constant of the CUDA programming model

6   localWarpId  $\leftarrow$  threadId  $\div$  N_THREADS_PER_WARP // warp id within the block

7   // nThreadsPerBlock is the number of threads per block (blockDim.x in CUDA)

8   assert nThreadsPerBlock mod N_THREADS_PER_WARP = 0

9   nWarpsPerBlock  $\leftarrow$  nThreadsPerBlock  $\div$  N_THREADS_PER_WARP // # warps in each block

10  globalWarpId  $\leftarrow$  blockId  $\cdot$  nWarpsPerBlock + localWarpId // warp id within the grid

11  // Each warp of the grid handles exactly one batch of NFAs

12  // Each batch contains N_THREADS_PER_WARP NFAs

13  batchId  $\leftarrow$  globalWarpId // identifier for the batch to be processed

14  &BatchSA<T> batch  $\leftarrow$  &batches[batchId] // pointer to batch

15  localNfaId  $\leftarrow$  threadId mod N_THREADS_PER_WARP // NFA id within the warp/batch

16  T maskInitial  $\leftarrow$  batch.masks_initial[localNfaId] // mask of initial states

17  T maskFinal  $\leftarrow$  batch.masks_final[localNfaId] // mask of final states

18  // Execution of homogeneous NFA:

19  T states  $\leftarrow$  0 // set of active states

20  nMatches  $\leftarrow$  0 // number of matches

21  for c in text do // left-to-right pass over input text

22    mask  $\leftarrow$  batch.masks_char[c][localNfaId] // get mask for character c

23    states  $\leftarrow$  ((states  $\ll$  1) OR maskInitial) AND mask // execute transition

24    nMatches  $\leftarrow$  nMatches + ((states AND maskFinal)  $\neq$  0)

25  globalNfaId  $\leftarrow$  batchId  $\cdot$  N_NFAS_PER_BATCH + localNfaId

26  assert globalNfaId = blockId  $\cdot$  nWarpsPerBlock + localWarpId

27  output[globalNfaId]  $\leftarrow$  nMatches

```

---

block corresponds to 4 warps for a total of 384 NFAs in the dataset. There are 128 threads per block or, equivalently, 128 NFAs per block.

For example, the NFA with global identifier 200 belongs to block 1 and is executed by the warp with global id 6. At runtime, the CUDA scheduler dispatches blocks to multiprocessors (SM) and the SM scheduler selects a warp to be executed. Suppose that block 1 is dispatched to SM0 which executes warp 6 that contains NFA 200. In Algorithm 2, the execution of NFA 200 (in parallel with all the NFAs of warp 6) starts by retrieving *blockId*, the block identifier in the grid, and *threadId*, the thread identifier within the block. For NFA 200, we have *blockId* = 1 and *threadId* = 72 as NFA 200 belongs to block 1 and is the 73rd NFA in the block (out of 128). To retrieve the Shift-And masks, which are stored per batch, we need to calculate the global batch id and the local NFA id. First, we calculate the local warp id (within the block) as follows: *localWarpId* = *threadId*  $\div$  N\_THREADS\_PER\_WARP = 72  $\div$  32 = 2. Then, we calculate the global warp id (within the grid) by *globalWarpId* = *blockId*  $\cdot$  nWarpsPerBlock + *localWarpId* = 1  $\cdot$  4 + 2 = 6. Since one batch corresponds exactly to one warp, we also obtain that *batchId* = 6. We calculate the local NFA id by *localNfaId* = *threadId* mod N\_THREADS\_PER\_WARP = 72 mod 32 = 8. Now, we can obtain the masks *maskInitial* and *maskFinal* by indexing with the local NFA id.

From Line 11, the algorithm starts with the simulation of the execution of the NFA. For every character *c* of the input text, we fetch the character mask by first indexing using *c* and then using the local NFA id. We continue to simulate the transition of the NFA using the Shift-And algorithm. This requires only 1 left shift, 1 bitwise OR, and 1 bitwise AND. We continue to check whether the pattern

matches at the current location by comparing the active states with the final states (if they overlap, then there is a match). At the end of the execution, we calculate the global NFA id (within the entire pattern set) as follows:  $globalNfaId = batchId \cdot N\_NFAS\_PER\_BATCH + localNfaId = 6 \cdot 32 + 8 = 200$  and we store the number of matches for NFA 200 in the output array.

In Algorithm 2, the layout and access pattern of the `Batch_SA` structure are carefully chosen to reduce the latency incurred by accesses to the off-chip global memory. In fact, we make sure that all the threads within a warp make contiguous memory accesses, generally referred to as *coalesced accesses*. In the Shift-And pseudocode, the 32 threads of a warp access the same `Batch_SA` structure (`batchId` is computed directly from the `blockId` which is identical for the threads in a warp). Then, the 1-dimensional mask arrays `maskInitial` and `maskFinal` are indexed with `localNfaId`, which takes values from 0 to 31. The 2-dimensional array `masks_char` is accessed with two indexes: a character `c` and an index `localNfaId`. For a fixed character `c`, `masks_char[c]` is a row of the 2D array and is stored in consecutive memory locations. For this reason, the memory accesses `masks_char[c][localNfaId]` in a warp are coalesced. More details about memory coalescing can be found in [NVidia 2013a]. Algorithm 2 does not contain any branching that could possibly make the threads of a warp diverge. **Thread divergence** occurs when at least two threads disagree on the execution path within a warp and can be caused by a data-dependent conditional branch. In the event of a thread divergence, the warp executes each branch path taken serially, and the threads that are not on that path are disabled. Algorithm 2 does not use any shared memory [NVidia 2013b], which is a type of memory that can be used for inter-thread communication within a warp (in fact, within a thread block), and that often requires **warp-level synchronization** leading to additional complexity.

### 3.3 Extending Shift-And

The Shift-And algorithm only supports regular expressions that can be rewritten as a union of strings, which accounts for roughly 20% of all regexes over the datasets of Section 5. We would like to accelerate a larger percentage of the regular expressions on the GPU. Therefore, we propose extensions to the Shift-And algorithm to support more classes of regular expressions on the GPU.

**ShiftAndDist.** Shift-And restricts transitions from a state  $(i)$  to the next state  $(i + 1)$ , but many regular expressions require transitions that step over some states. We also need to support self-loops, i.e., transitions from state  $(i)$  to itself. To support more NFAs, we can generalize the bit-parallel simulation of transitions to distances other than 1. This is the main idea of the ShiftAndDist kernel. We group together NFAs with transition distance bounded above by a constant  $D$ . Algorithm 3 presents the CUDA kernel for the ShiftAndDist algorithm. The kernel is parameterized with the datatype  $T$  and the maximum distance  $D$  to execute transitions of distances from 0 to  $D$  (inclusive). Therefore, we can support all transitions of the form  $(i) \rightarrow (i + d)$  with  $0 \leq d \leq D$ , which we call shift transitions. The number of operations needed for ShiftAndDist is proportional to the maximum transition distance  $D$ . We use the structure `Batch_SA_Dist` for representing the NFAs that are handled by ShiftAndDist. Compared to `Batch_SA`, we add the 2-dimensional mask array `masks_dist`, where `masks_dist[d]` contains the source states of transitions of distance  $d$ . All threads within a warp always access the same memory location in `maskPerDist` (see lines 10 and 12), which ensures coalesced memory accesses. Moreover, ShiftAndDist completely avoids thread divergence.

```

template<typename T, uint8_t D> struct Batch_SA_Dist {

T masks_initial[N_NFAS_PER_BATCH]; // masks for initial states

T masks_final[N_NFAS_PER_BATCH]; // masks for final states

T masks_dist[D + 1][N_NFAS_PER_BATCH]; // masks for source states of edges with a given length

T masks_char[N_CHARS][N_NFAS_PER_BATCH]; // masks for states that match each character

};

```

**Algorithm 3:** ShiftAndDist for distance D on the GPU

---

```

1 Kernel ShiftAndDist<T, D>(output, batches, text):

2   ... // compute batchId and localNfaId as in ShiftAnd

3   &BatchSADist<T, D> batch ← &batches[batchId] // pointer to batch

4   T maskInitial ← batch.masks_initial[localNfaId] // mask of initial states

5   T maskFinal ← batch.masks_final[localNfaId] // mask of final states

6   T[] maskPerDist ← batch.masks_dist // pointer to masks for each distance  $\leq D$

7   T states ← 0 // set of active states

8   nMatches ← 0 // number of matches

9   for c in text do // left-to-right pass over input text

10    | next ← states AND maskPerDist[0] // states with a self-loop

11    | for d = 1, ..., D do

12    |   | next ← next OR ((states AND maskPerDist[d]) << d)

13    |   | mask ← batch.masks_char[c][localNfaId] // get mask for character c

14    |   | states ← (next OR maskInitial) AND mask // execute transition

15    |   | nMatches ← nMatches + ((states AND maskFinal) ≠ 0)

16    |   | globalNfaId ← batchId · N_NFAS_PER_BATCH + localNfaId

17    |   | output[globalNfaId] ← nMatches

```

---

**Example 5.** Consider the regex  $r = ab\{0,2\}c$ . The automaton below recognizes the language of  $r$ .

In this example, the maximum transition distance for the NFA is  $D = 3$  and it corresponds to the dashed arrow. Using Shift-And, we are only able to simulate the solid line transitions (distance 1). ShiftAndDist adds more expressiveness to our implementation by allowing for transitions with various distances. Here, the loop at line 11 in Algorithm 3 will simulate transitions of distances 0, 1, 2 and 3 (even though there is no transition of distance 0).

**ShiftAndGap.** We have implemented the specialized algorithm ShiftAndGap for the commonly occurring regexes that contain gap transitions such as  $ab\{0, k\}c$  with the transition going from state  $a$  to state  $c$ . The structure `Batch_SA_Gap` extends the existing `Batch_SA` structure with two additional fields: *maskGapI* and *maskGapF*. The mask *maskGapI* contains the positions of the states right before gaps, and *maskGapF* contains the positions of the states right after gaps. Algorithm 4 presents the pseudocode for ShiftAndGap. To efficiently compute the  $\epsilon$ -transitions, we use a bit trick at line 13. For datatype  $T = u32$ , the size of the `Batch_SA_Gap` is of about  $4 \cdot N\_NFAS\_PER\_BATCH \cdot \text{sizeof}(u32) + N\_CHARS \cdot N\_NFAS\_PER\_BATCH \cdot \text{sizeof}(u32) = 4 \cdot 32 \cdot 4 + 256 \cdot 32 \cdot 4 \approx 33\text{ KB}$  which is roughly the same as for `Batch_SA`. In general, the batch is dominated by the size of `masks_char`.

```

template<typename T> struct Batch_SA_Gap {

T masks_initial[N_NFAS_PER_BATCH]; // masks for initial states

T masks_final[N_NFAS_PER_BATCH]; // masks for final states

T masks_gap_initial[N_NFAS_PER_BATCH]; // masks for gap-initial states

T masks_gap_final[N_NFAS_PER_BATCH]; // masks for gap-final states

T masks_char[N_CHARS][N_NFAS_PER_BATCH]; // masks for states that match each character

}

```

**Algorithm 4:** ShiftAndGap on the GPU

---

```

1 Kernel ShiftAndGap<T>(output, batches, text):

2   ... // compute batchId and localNfaId as in ShiftAnd

3   &BatchSAGap<T> batch ← &batches[batchId] // pointer to batch

4   T maskInitial ← batch.masks_initial[localNfaId] // mask of initial states

5   T maskFinal ← batch.masks_final[localNfaId] // mask of final states

6   T maskGapI ← batch.masks_gap_initial[localNfaId] // mask of gap-initial states

7   T maskGapF ← batch.masks_gap_final[localNfaId] // mask of gap-final states

8   T states ← 0 // set of active states

9   nMatches ← 0 // number of matches

10  for c in text do // left-to-right pass over input text

11    mask ← batch.masks_char[c][localNfaId] // get mask for character c

12    states ← ((states << 1) OR maskInitial) AND mask // execute transition on c

13    // epsilon transitions for gaps:

14    eps ← (maskGapF – (states AND maskGapI)) AND (NOT maskGapF)

15    states ← states OR eps

16    nMatches ← nMatches + ((states AND maskFinal) ≠ 0)

17    globalNfaId ← batchId · N_NFAS_PER_BATCH + localNfaId

output[globalNfaId] ← nMatches

```

---

Table 1. Execution of the kernel ShiftAndGap<u32> for the pattern  $r = ab\{0,4\}c$  and the string `abbc`.

| Input                          | a      | b      | b      | c      |

|--------------------------------|--------|--------|--------|--------|

| <i>states</i> (before line 11) | 000000 | 011111 | 011110 | 011100 |

| <i>states</i> (after line 12)  | 000001 | 011110 | 011100 | 100000 |

| <i>eps</i> (after line 13)     | 011111 | 000000 | 000000 | 000000 |

| <i>states</i> (after line 14)  | 011111 | 011110 | 011100 | 100000 |

| <i>nMatches</i>                | 0      | 0      | 0      | 1      |

**Example 6.** Consider the regex  $r = ab\{0,4\}c$ . The following automaton  $\mathcal{A}_1$  (nondeterministic with epsilon transitions) recognizes the language of  $r$ .

In this example, we have a gap consisting of  $b\{0,4\}$ , the repetition of  $b$  between 0 and 4 times. In the automaton, there is a single gap-initial state, namely  $q_0$ , the state right before the gap  $b\{0,4\}$ . There is a single gap-final state, namely  $q_5$ , the state right after the gap. Table 1 presents the execution of  $\mathcal{A}_1$  by kernel ShiftAndGap<u32> for the input string `abbc`. The main idea of ShiftAndGap is to execute all the epsilon transitions into the gap with arithmetic and bitwise operations. The values of the masks used by ShiftAndGap for  $\mathcal{A}_1$  are the following:

$$\text{maskInitial} = 000001 \quad \text{maskFinal} = 100000 \quad \text{maskGapI} = 000001 \quad \text{maskGapF} = 100000$$

The character masks for `a`, `b` and `c` are `000001`, `011110`, and `100000` respectively. After consuming the character `a`, we start by performing the transitions of distance 1 with

$$\begin{aligned} \text{states} &= ((\text{states} \ll 1) \text{ OR } \text{maskInitial}) \text{ AND } \text{mask} \\ &= ((000000 \ll 1) \text{ OR } 000001) \text{ AND } 000001 = 000001. \end{aligned}$$

Then, we compute  $\text{eps}$ , the set of states activated by the epsilon transitions, in three steps. First, we compute the set of gap-initial states that are active with

$$\text{states AND } \text{maskGapI} = 000001 \text{ AND } 000001 = 000001.$$

Then, we identify the destination states for the epsilon transitions with

$$\begin{aligned} \text{eps} &= (\text{maskGapF} - (\text{states AND } \text{maskGapI})) \text{ AND } (\text{NOT maskGapF}) \\ &= (100000 - 000001) \text{ AND } 011111 \\ &= 011111 \text{ AND } 011111, \end{aligned}$$

which is equal to 011111. Notice that this bit vector includes the source state  $q_0$ , but this is not an issue because it is already enabled in  $\text{states}$ . So, at the end of the first round,  $\text{states} = 011111$ .

Let us consider now the body of the loop when we continue to consume the character `b`. After line 12 executes, we have that

$$\begin{aligned} \text{states} &= ((011111 \ll 1) \text{ OR } \text{maskInitial}) \text{ AND } \text{mask} \\ &= ((011111 \ll 1) \text{ OR } 000001) \text{ AND } 011110 = 011110. \end{aligned}$$

Then, we proceed to execute line 13, which computes the value

$$\begin{aligned} \text{eps} &= (\text{maskGapF} - (\text{states AND } \text{maskGapI})) \text{ AND } (\text{NOT maskGapF}) \\ &= (100000 - (011110 \text{ AND } 000001)) \text{ AND } 011111 = 000000. \end{aligned}$$

This means that no epsilon transitions are taken. This is expected, because the epsilon transitions are only taken right after we see a character `a`. So, after line 14, we have that  $\text{states} = 011110$ .

Suppose that in the third round we consume the character `b` again. After line 12 is executed, we have that  $\text{states} = ((011110 \ll 1) \text{ OR } 000001) \text{ AND } 011110 = 111101 \text{ AND } 011110 = 011100$ . As in the previous round, we get that  $\text{eps} = 000000$  after executing line 13. It follows that  $\text{states} = 011100$  after line 14.

In the final round of this example's execution, we read the character `c`. After executing line 12, we get  $\text{states} = ((011100 \ll 1) \text{ OR } 000001) \text{ AND } 100000 = 111001 \text{ AND } 100000 = 100000$ . No epsilon transitions are enabled and therefore  $\text{eps} = 000000$  after line 13 is executed. So,  $\text{states} = 100000$  after line 14. This means that the variable  $nMatches$  will be incremented by 1 at the end of this round, which indicates that a match of the regex has been found.

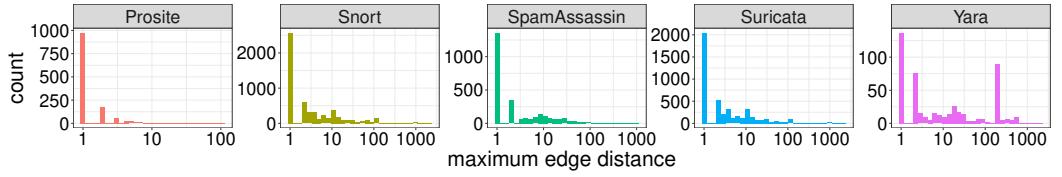

**ShiftAndOps.** In theory, ShiftAndDist can simulate all NFAs that have transitions of type  $(i) \rightarrow (j)$  where  $i \leq j$ . This corresponds to NFAs without back edges. Given an NFA with  $n$  states, the transition distance is bounded by  $n - 1$ . However, in practice this bound can be too large for efficient execution on the GPU. Take as example the regex `[A-Z0-9_-.]{20,300}x3b` from the Suricata dataset. The bound on the transition distance here is 281, thus we would iterate 282 (including distance 0) times over the loop starting at line 11 in Algorithm 3, leading to disastrous performance. Fig. 4 presents the distribution of the maximum transition distance across the Prosite, Snort, SpamAssassin, Suricata and Yara datasets which are described in more detail in Section 5. We observe that the majority of regexes have small maximum transition distance. For all datasets except Prosite, a non-negligible number of regexes have maximum distance larger than 10. Moreover, ShiftAndDist cannot support regexes with back edges, i.e. transitions of the form  $(i) \rightarrow (j)$  with  $j < i$ . We introduce a new algorithm to deal efficiently with regexes containing long transitions and to support those with backward transitions. We call it ShiftAndOps.

Algorithm 5 presents the ShiftAndOps kernel, which extends the kinds of NFA transitions that are supported on the GPU by introducing multi-edge transitions.

Fig. 4. Distribution of the maximum transition distance across the datasets

We introduce two kinds of *multi-edge transitions* to efficiently execute regexes with disjunctions: one-to-many and many-to-one transitions. A one-to-many transition has the form  $(q_i) \rightarrow (q_{k_1}, q_{k_2}, \dots, q_{k_n})$  and can be thought of as the collection of the  $n$  individual NFA transitions  $q_i \rightarrow q_{k_1}$ ,  $q_i \rightarrow q_{k_2}$ , ...,  $q_i \rightarrow q_{k_n}$ . So, if  $q_i$  is active, then the states  $q_{k_1}, q_{k_2}, \dots, q_{k_n}$  are activated after the transition is performed. One-to-many transitions arise in regexes with disjunctions such as  $r = a(b|c?b|b+)$ , where the first state labeled with `a` activates the first states in each disjunction. A many-to-one transition has the form  $(q_{k_1}, q_{k_2}, \dots, q_{k_n}) \rightarrow (q_i)$  and is essentially the collection of the  $n$  individual NFA transitions  $q_{k_1} \rightarrow q_i, q_{k_2} \rightarrow q_i, \dots, q_{k_n} \rightarrow q_i$ . If any of the states  $q_{k_1}, q_{k_2}, \dots, q_{k_n}$  is active, then the state  $q_i$  gets activated after the transition is performed. Many-to-one transitions are useful for regexes with disjunctions such as  $r = (a|b+|cd)e$ , where any of the states labeled with `a`, `b` or `d` can activate the state labeled with `e`. Compared to Algorithm 3 for the `ShiftAndDist` kernel, Algorithm 5 adds a new block starting at line 14 to simulate the multi-edge transitions. The structure `Batch_SA_Ops` extends `Batch_SA` with the four additional mask arrays `masks_shift`, `masks_dist`, `masks_src` and `masks_dst`. The bit vector `masks_shift[i][localNfaId]` contains the source states for the  $i$ -th shift operation for NFA `localNfaId` of the batch. The integer `shift_dist[i][localNfaId]` is the distance of the  $i$ -th shift operation. The bit vector `masks_src[i][localNfaId]` contains the source states which activate the destination states in `masks_dst[i][localNfaId]` for NFA `localNfaId` of the batch. In the block executing multi-edge transitions (starting at line 14), one-to-many and many-to-one transitions are executed using the same instructions. Example 7 shows the masks used by `ShiftAndOps` for the execution of regex  $r = a(bc|de|fg|)h$ .

```

template<typename T, uint8_t M, uint8_t N> struct Batch_SA_Ops {

T masks_initial[N_NFAS_PER_BATCH]; // masks for initial states

T masks_final[N_NFAS_PER_BATCH]; // masks for final states

T masks_shift[M][N_NFAS_PER_BATCH]; // masks for source states of edges with a given length

uint32_t shift_dist[M][N_NFAS_PER_BATCH]; // distance for each shift operation

T masks_src[N][N_NFAS_PER_BATCH]; // source masks for multi-edge transitions

T masks_dst[N][N_NFAS_PER_BATCH]; // destination masks for multi-edge transitions

T masks_char[N_CHARS][N_NFAS_PER_BATCH]; // masks for states that match each character

};

```

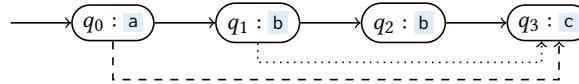

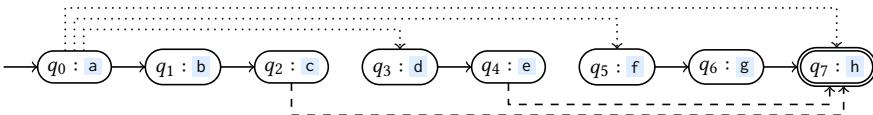

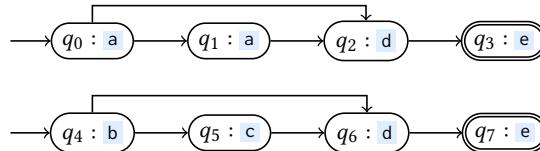

**Example 7.** Consider the regex  $r = a(bc|de|fg|)h$ . The following automaton  $\mathcal{A}_1$  implements  $r$ .

In this example, we have three kinds of operations: 1 one-to-many operation, 1 many-to-one operation and 1 shift operation. The one-to-many operation corresponds to the dotted lines starting from state  $q_0$  and going to the set of states  $\{q_3, q_5, q_7\}$ . The many-to-one operation, in dashed line, goes from the set of states  $\{q_2, q_4\}$  to the final state  $q_7$ . The remaining transitions are of distance 1

**Algorithm 5:** ShiftAndOps for M shifts and N multi-edge transitions on the GPU

---

```

1 Kernel ShiftAndOps<T, M, N>(output, batches, text):

2   ... // compute batchId and localNfald as in ShiftAnd

3   &BatchSOPs<T, M, N> batch ← &batches[batchId] // pointer to batch

4   T maskInitial ← batch.masks_initial[localNfald] // mask of initial states

5   T maskFinal ← batch.masks_final[localNfald] // mask of final states

6   T states ← 0 // set of active states

7   nMatches ← 0 // number of matches

8   for c in text do // left-to-right pass over input text

9     next ← 0 // next active states

10    for i = 0, ..., M - 1 do // take M "shift" transitions

11      mask ← batch.masks_shift[i][localNfald]

12      d ← batch.shift_dist[i][localNfald]

13      next ← next OR ((states AND mask) ≪ d)

14    for i = 0, ..., N - 1 do // take N "multi-edge" transitions

15      src ← batch.masks_src[i][localNfald] // set of source states

16      dst ← batch.masks_dst[i][localNfald] // set of destination states

17      if (states AND src) ≠ 0 then next ← next OR dst

18      mask ← batch.masks_char[c][localNfald] // get mask for character c

19      states ← (next OR maskInitial) AND mask // execute transition

20      nMatches ← nMatches + ((states AND maskFinal) ≠ 0)

21    globalNfald ← batchId · N_THREADS_PER_WARP + localNfald

22    output[globalNfald] ← nMatches

```

---

Table 2. Multi-edge masks of the kernel ShiftAndOps<u32, 1, 2> for the pattern  $r = a(bc|de|fg|h)$ .

| Operation                 | src            | dst                 | mask_src | mask_dst |

|---------------------------|----------------|---------------------|----------|----------|

| one-to-many (dotted line) | $q_0$          | $\{q_3, q_5, q_7\}$ | 00000001 | 10101000 |

| many-to-one (dashed line) | $\{q_2, q_4\}$ | $q_7$               | 00010100 | 10000000 |

Table 3. Execution of the kernel ShiftAndOps<u32, 1, 2> for the pattern  $a(bc|de|fg|h)$  and the string  $abch$ .

| Input                  | a        | b        | c        | h        |

|------------------------|----------|----------|----------|----------|

| next (before line 14)  | 00000000 | 00000010 | 00000100 | 00000000 |

| next (before line 18)  | 00000000 | 10101010 | 00000100 | 10000000 |

| mask (after line 18)   | 00000001 | 00000010 | 00000100 | 10000000 |

| states (after line 19) | 00000001 | 00000010 | 00000100 | 10000000 |

| <i>nMatches</i>        | 0        | 0        | 0        | 1        |

and are executed using 1 shift operation (solid line). Note that transition  $q_0 \rightarrow q_1$  (resp.,  $q_6 \rightarrow q_7$ ) can be encoded either in the one-to-many (resp., many-to-one) operation or in the shift operation.

Table 3 presents the execution of  $\mathcal{A}_1$  by kernel ShiftAndOps<u32, 1, 2> for the input string  $abch$ . ShiftAndOps can execute all the transitions leading to a single state (resp., starting from a single state) in one operation. The values of the masks used by the multi-edge transitions are shown in Table 2. For the shift transition, we have  $mask\_shift = 01101011$  and  $shift\_dist = 1$  because the states  $q_0, q_1, q_3, q_5, q_6$  are source states of transitions of distance 1. The character masks for  $a, b, c$  and  $h$  are 00000001, 00000010, 00000100 and 10000000 respectively. After consuming the

character `a`, we start by performing the shift transitions of distance 1 with

$$\begin{aligned} next &= next \text{ OR } ((states \text{ AND } mask) \ll d) \\ &= 00000000 \text{ OR } ((00000000 \text{ AND } 01101011) \ll 1) = 00000000. \end{aligned}$$

To perform the one-to-many operation  $q_0 \rightarrow \{q_3, q_5, q_7\}$  we calculate

$$states \text{ AND } src = 00000000 \text{ AND } 00000001 = 00000000.$$

Similarly, to perform the many-to-one operation  $\{q_2, q_4\} \rightarrow q_7$  we calculate

$$states \text{ AND } src = 00000000 \text{ AND } 00010100 = 00000000.$$

This means that no multi-edge operations are applied and we have that  $next = 00000000$  before line 18. The value of *states* after line 19 is computed with

$$\begin{aligned} states &= (next \text{ OR } maskInitial) \text{ AND } mask \\ &= (00000000 \text{ OR } 00000001) \text{ AND } 00000001 = 00000001. \end{aligned}$$

We proceed now to the second round. After consuming the character `b`, we have that

$$next = 00000000 \text{ OR } ((00000001 \text{ AND } 01101011) \ll 1) = 00000010$$

before line 14. This corresponds to taking the shift transition from  $q_0$  to  $q_1$ . The one-to-many operation  $q_0 \rightarrow \{q_3, q_5, q_7\}$  is enabled (because  $q_0$  is active in *states*), so we obtain  $next = 10101010$  after all transitions are performed. After line 19, we have that  $states = (10101010 \text{ OR } 00000001) \text{ AND } 00000010 = 00000010$ .

For the third round, we consume the character `c`, and  $next = 00000000 \text{ OR } ((00000010 \text{ AND } 01101011) \ll 1) = 00000100$  before line 14. This corresponds to taking the shift transition from  $q_1$  to  $q_2$ . No multi-edge operation is enabled, and therefore *next* is not updated. After line 19, we have that  $states = (00000100 \text{ OR } 00000001) \text{ AND } 00000100 = 00000100$ .

For the final round, we consume the character `h`, and  $next = 00000000 \text{ OR } ((00000100 \text{ AND } 01101011) \ll 1) = 00000000$  before line 14. This means that the shift operation performs no transition. For the many-to-one operation  $\{q_2, q_4\} \rightarrow q_7$ , we have that  $states \text{ AND } src = 00000100 \text{ AND } 00010100 = 00000100$ . So, we take the multi-edge operation and we have before line 18 that  $next = 10000000$ . The one-to-many operation  $q_0 \rightarrow \{q_3, q_5, q_7\}$  is not performed ( $q_0$  is not active in *states*). After line 19, we have  $states = (10000000 \text{ OR } 00000001) \text{ AND } 10000000 = 10000000$ . As  $states \text{ AND } maskFinal = 10000000 \neq 00000000$ , we report a match and increment *nMatches*.

We need 13 basic operations (i.e., bitwise and memory access operations) to execute *r* with `ShiftAndOps<u32, 1, 2>`. We would need 31 basic operations if we used `ShiftAndDist<u32, 7>`. Table 4 has more details on the number of basic operations required for executing our kernels.

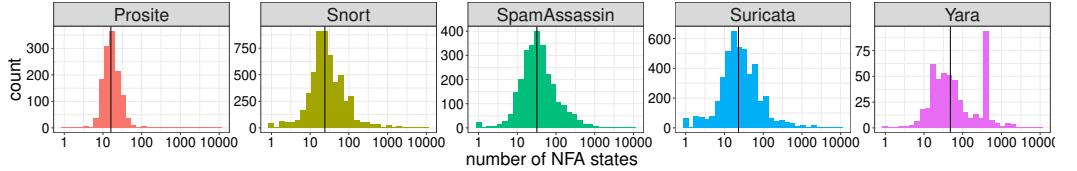

**Kernel datatype.** Until now, we have only considered regexes of size at most 32 (# character classes), because registers on the GPU are 32 bits wide. However, if we want to support a large number of regular expressions, we need to extend this bound. Fig. 5 presents the distributions of the number of NFA states across the datasets. The medians are: 16 for Prosite, 24 for Snort, 32 for SpamAssassin, 23 for Suricata and 48 for Yara. From the median, we already know that more than half of the regexes would not be handled with the `u32` datatype for the SpamAssassin and Yara datasets. We observe that for the Prosite dataset, the majority of regexes can be simulated using Shift-And. For the other datasets, a large portion of the regexes have more than 32 states. This shows there is a need for wider datatypes. The NVCC compiler for CUDA code supports bitwise operations up to 128 bits. For each of the 4 kernel families (Shift-And, ShiftAndDist, ShiftAndGap and ShiftAndOps), we have created variants for datatype up to `u256`.

Fig. 5. Distribution of the number of NFA states per regex across the datasets. Vertical line indicates the median.

Table 4. Summary of the operations per input character to simulate the transitions for the ShiftAnd, ShiftAndGap, ShiftAndDist and ShiftAndOps kernels. We use the symbol  $\ll$  for the left shift operation, OR for bitwise or, AND for bitwise and, and NOT for bitwise complement.

| kernel                 | mem. access | $\ll$ | OR      | AND     | NOT | total     |

|------------------------|-------------|-------|---------|---------|-----|-----------|

| ShiftAnd<u32>          | 1           | 1     | 1       | 1       | 0   | 4         |

| ShiftAndGap<u32>       | 1           | 1     | 2       | 4       | 1   | 9         |

| ShiftAndDist<u32, D>   | $D + 1$     | $D$   | $D + 1$ | $D + 1$ | 0   | $4D + 3$  |

| ShiftAndOps<u32, M, N> | $2(M+N)$    | $M$   | $M + N$ | $M + N$ | 0   | $5M + 4N$ |

**Number of operations.** Table 4 summarizes the number of bitwise operations and memory accesses per input character for each kernel. We exclude the operations needed to calculate the number of matches. For ShiftAnd and ShiftAndGap, the total number of basic operations is constant. For ShiftAndDist< $D$ >, it is linear in the maximum distance  $D$ . For ShiftAndOps< $M, N$ >, the total number of basic operations is linear in  $M$  (# shift operations) and  $N$  (# multi-edge operations). The kernel ShiftAnd<u32> uses the least number of operations, namely 4. The kernels ShiftAndGap<u32> and ShiftAndOps<u32, 1, 1> both require 9 operations, thus we expect their performance to be similar. For datatypes  $T$  that are wider than u32, each bitwise operation requires several machine instructions. Therefore, we generally expect that doubling the width of the datatype (for instance, from 64 to 128 bits) will double the number of machine instructions executed per input character (for instance, 16 operations for ShiftAnd<u128>).

**Kernel expressiveness.** Table 5 presents a summary of the kernels' capabilities to simulate the different types of transitions mentioned earlier. We observe that ShiftAndGap is more expressive than ShiftAnd as it can execute all the transitions that ShiftAnd can execute in addition to the gap transitions. ShiftAndDist and ShiftAndGap are incomparable because even though ShiftAndGap can execute transitions with distance greater than 1, those are limited to gap transitions whereas ShiftAndDist<u32,  $D$ > cannot execute gap transitions with distance greater than  $D$ . When  $N > 0$ , the kernel ShiftAndOps<u32,  $M, N$ > is more expressive than ShiftAndGap<u32>, as a gap transitions can be expressed as a one-to-many transition. By construction, ShiftAndOps<u32,  $M + 1, N$ > is more expressive than ShiftAndDist<u32,  $M$ > as the shift transitions from 0 to  $M$  can be executed with  $M + 1$  shift transitions (not necessarily for consecutive distances unlike ShiftAndDist) in addition to the  $M$  multi-edge transitions. Fig. 6 shows the relationships between GPU kernels using a Hasse diagram, in which kernels are ordered by expressiveness.

Fig. 6. Hasse diagram for GPU kernel expressiveness.

Table 5. Summary of the expressiveness of the ShiftAnd, ShiftAndGap, ShiftAndDist and ShiftAndOps kernels.  $\infty$  means that the distance is only bounded by the number of states.

| kernel                 | shifts  | min. dist. | max. dist. | backedges | self-loops | gaps | multi-edges |

|------------------------|---------|------------|------------|-----------|------------|------|-------------|

| ShiftAnd<u32>          | 1       | 1          | 1          | ✗         | ✗          | ✗    | ✗           |

| ShiftAndGap<u32>       | 1       | 1          | 1          | ✗         | ✗          | ✓    | ✗           |

| ShiftAndDist<u32, D>   | $D + 1$ | 0          | $+\infty$  | ✗         | ✓          | ✗    | ✗           |

| ShiftAndOps<u32, M, N> | $M$     | $-\infty$  | $+\infty$  | ✓         | ✓          | ✓    | $N$         |

#### 4 Compilation and Optimizations

Recall that an instance of the multi-pattern matching problem consists of a set of patterns, given as regexes, and an input string over which to search for pattern occurrences. This section describes the compilation of regexes into NFA data that can be used by the GPU kernel families ShiftAnd, ShiftAndDist, ShiftAndGap and ShiftAndOps that were described in Section 3.

First, we describe the compilation process which transforms a dataset in the form of a set of regexes into masks (i.e., bit vectors) that are used for execution on the GPU. Then, we explain how we determine for each pattern whether it should execute on the CPU or on the GPU using a specific kernel. Finally, we discuss two transformations that allow us to move a regex (NFA) from a more computationally expensive kernel to a cheaper one.

**Compilation procedure and execution.** Initially, the input dataset is given as a set of regular expressions. HybridSA carefully chooses a list of kernels to run on the GPU. The regexes that cannot be handled by the chosen GPU kernels are executed on the CPU using Hyperscan. Since modern CPUs typically have several cores, the CPU workload is parallelized using threads. Hyperscan accepts a set of regexes as input, so no transformation of the patterns is needed. For the GPU part, kernel execution uses a representation of NFAs in terms of bit masks, as described in Section 3. For a given regular expression, the bit masks used to represent its NFA differ based on whether it is executed (for example) by ShiftAnd, ShiftAndOps<u32, 1, 1>, or ShiftAndOps<64, 1, 1>. The procedure that transforms a regex dataset into batches of masks is performed by a compilation library that we have implemented in Rust. It consists of 3 steps. In the first step, each regex is mapped to the cheapest kernel that can execute it. For instance, consider the regex  $r = ab?c$  and the kernels ShiftAndDist<u32, 2> and ShiftAndDist<u32, 3>. The compiler will choose ShiftAndDist<u32, 2>, as it can execute  $r$  and requires fewer operations than ShiftAndDist<u32, 3>. In the second step, we compute the masks for each regex and its associated kernel. For the regex  $r = ab?c$  and kernel ShiftAndDist<u32, 2>, we compute the *mask\_initial* and *mask\_final* masks which contain respectively the positions of initial and final states as well as *mask\_dist*[ $d$ ] for the source states of transitions of distance  $d$  between 0 and 2 and *mask\_char*[ $c$ ] containing the positions of states whose label matches the character  $c$ . In the third step, masks belonging to regexes to be executed by the same kernel variant are grouped together into batches (see Section 3) of 32 regexes to form a batch database. This database is used during GPU execution.

For the execution, our kernels are implemented in CUDA and the kernel variants are created using C++ templates. We have chosen not to generate specialized code, as it would not provide a substantial performance benefit. For a given dataset, we start by compiling the regex dataset. Then, we invoke the CUDA kernels concurrently using a Foreign Function Interface which binds the CUDA functions to Rust functions.

**Choice of kernels to execute on the GPU.** We are given a set of regular expressions. First, we need to decide which regexes to put on the GPU. Then, for regexes that are executed on the GPU,

we need to choose the kernel that will execute it. For a fixed regex  $r$ , there is a list of candidate kernels. `ShiftAndOps` is the most expressive kernel, because it is capable of simulating any regex  $r$ . Nevertheless, it would not be wise to execute all the regexes on the GPU with the `ShiftAndOps` kernel. Consider, for example,  $r = a.\{0,100\}b$ . Executing  $r$  with the `ShiftAndOps` or `ShiftAndDist` kernels would require many bitwise operations, resulting in poor performance. Instead, it is better to execute  $r$  with `ShiftAndGap`, which requires fewer bitwise operations in this case. In general, our compiler splits a set of regexes into two subsets: one subset that is executed on the GPU using our CUDA kernels and the other is executed on the CPU with Hyperscan. The split is done to balance the load between the CPU and the GPU. Then, for a given regex, we choose the kernel that will execute it. The strategy we use consists in selecting the kernel with the least number of operations that can simulate the regex like we did with  $r$  above. Moreover, it is inefficient to execute a kernel for only 1 NFA because the other 31 threads in the warp would not be performing useful work. If 10 regexes are compiled for `ShiftAndDist<u32, 4>` and 22 regexes for `ShiftAndDist<u32, 5>`, it is better to pack the batches by compiling all the 32 regexes for `ShiftAndDist<u32, 5>` to use a single batch instead of two. In practice, we have observed a reduction of wasted regexes (i.e. padding regexes within a batch, that do not perform any meaningful instruction) by half thanks to batch packing for the datasets considered in the experiment section.

**Splitting between GPU and CPU.** In our hybrid algorithm, regexes are split between GPU and CPU and executed in parallel. To attain the best performance, the durations of GPU and CPU processing should be as close as possible to prevent underutilizing the computational resources (if one finished early, then it would sit idle). We use a *training stage* to choose how the regexes are split between the CPU and the GPU. For a given dataset, we have collected a set of input strings that are representative of the application. The training input strings are disjoint from the input strings used for the performance evaluation. We consider different choices  $K_i$ , where  $K_i$  is a set of kernels. Every  $K_i$  splits the dataset into two parts: 1) the regexes that can be handled by  $K_i$  on the GPU, and 2) the rest of the regexes that go to the CPU. Each choice  $K_i$  has a score  $throughput(K_i)$ , which is the throughput of HybridSA for the GPU-CPU split induced by  $K_i$ . Finding an optimal CPU-GPU split is not easy, as the number of possible choices is astronomical (i.e.  $2^{\# \text{regexes}}$ ). We use a "fastest kernel first" strategy which gives good performance while executing in a timely manner. In this strategy, we start by examining the choice  $K_1 = \{\text{ShiftAnd}<\text{u32}\>\}$ , then  $K_2 = \{\text{ShiftAnd}<\text{u32}\>, \text{ShiftAndDist}<\text{u32, 1}\>\}$ , etc. The exploration of the choices stops when we achieve peak throughput for HybridSA. This corresponds to having roughly the same computation time on the GPU and the CPU. In practice, we observe that the balance between GPU and CPU computation times is preserved when switching to the input strings of the experiments.

**Distributivity Rewriting.** We now consider the numbering problem. For a given NFA, there are several possible numbering of the automaton states, which change the operations needed to simulate it with our kernels. We perform some rewritings to reduce the number of operations to simulate an NFA and ultimately accelerate more regexes on the GPU.

Our first rewriting is at the level of the regular expression, and is based on a distributivity property that says that concatenation distributes over union. By distributivity, we can rewrite  $(r_1 + r_2) \cdot r_3$  as  $r_1 \cdot r_3 + r_2 \cdot r_3$ . If we name  $m$  and  $n$  the number of states respectively of  $r_1$  and  $r_2$ , we observe that the rewriting replaced a transition of distance  $m + n$  into two transitions of distance  $m$  and  $n$ . This comes at the cost of more NFA states as  $r_3$  is duplicated. In addition to moving regexes from expensive to cheaper kernels (in terms of the number of operations), the rewriting allows for more regexes to be supported by the existing kernels, and thus to be accelerated on the GPU. In practice, we apply distributivity rewriting when it allows us to move a regex from a slower kernel to a faster kernel according to the ranking that we maintain in Table 6.

**Example 8.** Consider the regex  $r = (a\{1,2\}|bc?)de$ . The following automaton  $\mathcal{A}_1$  implements  $r$ .

We note that the transition  $q_0 \rightarrow q_4$  has distance 4. After distributing the concatenation over the union, i.e.,  $(a\{1,2\}|bc?)de = (a\{1,2\}de|bc?de)$ , we obtain the following automaton  $\mathcal{A}_2$ :

Both  $\mathcal{A}_1$  and  $\mathcal{A}_2$  recognize the language of  $r$ , but  $\mathcal{A}_2$  reduces the maximum transition distance from 4 to 2 compared to  $\mathcal{A}_1$ . Thus, after the rewriting and re-labeling of the states in each of the connected components,  $r$  can be executed with kernel `ShiftAndDist<u32, 2>` instead of `ShiftAndDist<u32, 4>` before the rewriting which requires more operations (see Table 4).

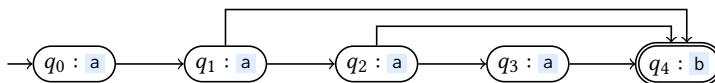

**Bounded repetition rewriting.** In addition to the distributivity rewriting, we use another rewriting over bounded repetitions to lower the maximum transition distance. The intuition behind this rewriting is that we want to break down transitions into smaller transitions to reduce the overall distance. The rewriting is based on the following identity over regular expressions:  $\sigma\{k, d \cdot k\} = (\sigma\{1, d\})\{k\}$ . From a maximum distance of  $(d - 1) \cdot k + 1$ , we go down to a maximum distance of  $d$ . This rewriting can be generalized to regexes of the form  $\sigma\{m, n\}$  when  $n \leq d \cdot m$  to reduce the maximum distance to  $d$ . In practice, we would choose the minimum  $d$  such that  $n \leq d \cdot m$  to have the lowest possible maximum distance. With this rewriting, we are able to compile the rewritten regex with a kernel that uses fewer operations than the original regex.

**Example 9.** Consider the regex  $r = a\{2,4\}b$ . The following automaton  $\mathcal{A}_1$  given by the Glushkov construction recognizes the language of  $r$ .

Notice that transition  $q_1 \rightarrow q_4$  has distance 3. After applying the rewriting  $a\{2,4\}b = a\{1,2\}a\{1,2\}b$  to  $r$ , we obtain the following automaton  $\mathcal{A}_2$ :

Both  $\mathcal{A}_1$  and  $\mathcal{A}_2$  recognize the language of  $r$ , but  $\mathcal{A}_2$  reduces the maximum transition distance from 3 to 2 compared to  $\mathcal{A}_1$ .

## 5 Experiments

We have implemented HybridSA using the Rust programming language for the compiler and CUDA for the GPU kernels. In this section, we evaluate the performance of HybridSA to answer the following questions:

- (1) What classes of regular expressions can HybridSA execute efficiently on the GPU?

- (2) How well does HybridSA multi-pattern matching perform compared to existing state-of-the-art tools?

**Experimental setup.** The experiments were executed on a desktop machine running Ubuntu 22.04 and equipped with an Intel(R) Core(TM) i9-12900K CPU (16 cores, multithreading up to 24 threads), an NVIDIA GeForce RTX 4060 Ti (34 multiprocessors, Ada Lovelace architecture with 8 GB of global memory), and 32 GB of memory. We compile the kernels with CUDA 12.2. For each experiment, we run 10 trials and report the mean of the measurements. For the GPU measurements, we take a similar approach to previous works and focus on the execution time of the kernels, excluding memory transfers between CPU and GPU because they are negligible and can be overlapped with computations. Throughput is calculated by dividing the input size (in characters) by the execution time.

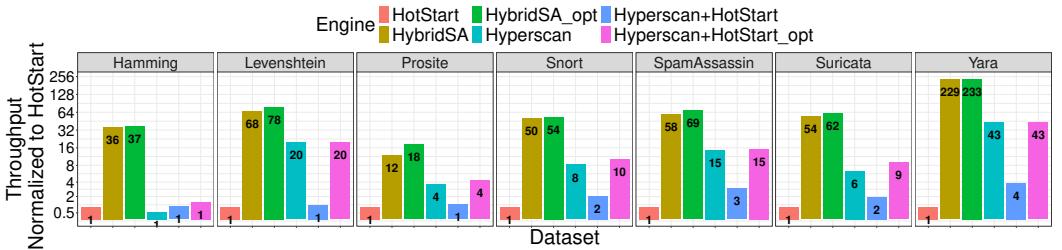

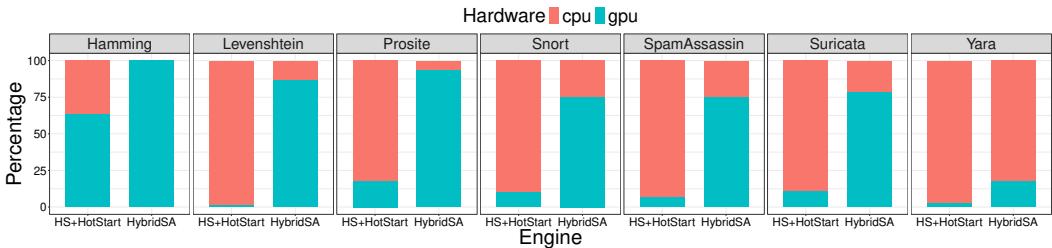

**Evaluated schemes.** We compare the performance of HybridSA against HotStart [Liu et al. 2020], which is a state-of-the-art engine for multi-pattern matching on the GPU, and the state-of-the-art CPU engine Hyperscan [Wang et al. 2019]. Since HybridSA uses both the CPU and the GPU, for a fair comparison we also consider a hybrid combination of Hyperscan and HotStart that we call Hyperscan+HotStart. A comparison between HybridSA and Hyperscan+HotStart, which use the same computational resources (i.e., CPU and GPU), will show the performance improvement of HybridSA due to the effectiveness of the bit-parallel kernels described in Section 3. To demonstrate the effectiveness of the optimizations presented in Section 4, we evaluate two variants of HybridSA: (1) HybridSA\_no\_opt, which uses the bit-parallel kernels, and (2) HybridSA\_opt, which uses the rewriting and batch packing optimizations. The kernels used to execute regexes on the GPU are chosen per dataset following the compilation strategy described in Section 4.

We compare our implementation against the HotStart-MaC variant of the HotStart algorithm presented in [Liu et al. 2020], which is the version with the best overall performance. It is based on NFA execution, with various optimizations to reduce data movement and improve the compute utilization of GPU resources. Compared to HybridSA, HotStart executes all the regexes on the GPU, and the unit of computation of a thread in HotStart is the NFA state whereas, for HybridSA, a warp executes a set of 32 NFAs. Moreover, the subset of regexes that are executed by HybridSA on the GPU are input independent, meaning that the throughput is independent from the input. On the opposite, the HotStart throughput depends on the input stream. More specifically, an input stream that gives rise to many matches can degrade the overall throughput of HotStart. The HotStart algorithm performs two steps: hot state execution followed by cold state execution. Hot states are NFA states that are the most likely to get activated during matching, and in practice they are chosen to be the initial states. If many cold states are active, the second stage duration will be impacted.

To use the full computational power of the CPU, we run Hyperscan in a multithreaded setting with 24 threads, which is the number of threads maximizing the performance for the CPU we use. Hyperscan can be parallelized over the input streams or the regexes. In our settings, we parallelize over the input streams. We have observed that parallelizing over input streams has better performance compared to parallelizing over regexes. This is because the execution time of regular expressions is not uniform in Hyperscan, which can create an imbalance among the threads in the case of regex parallelism. For the combination of HotStart and Hyperscan, we select the percentage of regexes on the GPU maximizing the overall throughput, where regexes are chosen randomly.

**Regex split between HotStart and Hyperscan.** Finding an optimal CPU-GPU split for HotStart+Hyperscan is not easy, as the number of possible choices is enormous (i.e.,  $2^{\# \text{ regexes}}$ ). We have observed that the regexes that are expensive for Hyperscan are those that are highly nondeterministic and that match frequently. But these are also the kinds of regexes that we have noticed are expensive for HotStart. So, there does not seem to be a clear criterion for regexes that are expensive for Hyperscan but cheap for HotStart, which could be used to inform the GPU-CPU split as we did with HybridSA. Thus, we compare two choices of split: 1) split based on a training step to

Table 6. Throughput (in MB/sec) for the top 10 fastest kernels on the GPU.

| kernel                 | throughput | datatype | d | ops |

|------------------------|------------|----------|---|-----|

| ShiftAnd<u32>          | 222        | u32      | 0 | 0   |

| ShiftAndDist<u32, 1>   | 195        | u32      | 1 | 0   |

| ShiftAnd<u64>          | 180        | u64      | 0 | 0   |

| ShiftAndGap<u32>       | 174        | u32      | 0 | 0   |

| ShiftAndDist<u32, 2>   | 160        | u32      | 2 | 0   |

| ShiftAndDist<u32, 3>   | 147        | u32      | 3 | 0   |

| ShiftAndOps<u32, 1, 1> | 139        | u32      | 1 | 1   |

| ShiftAndOps<u32, 1, 2> | 125        | u32      | 1 | 2   |

| ShiftAndDist<64, 1>    | 124        | u64      | 1 | 0   |

| ShiftAndDist<u32, 4>   | 124        | u32      | 4 | 0   |

select the percentage of regexes that go to the GPU to maximize the overall throughput (labeled HotStart+Hyperscan\_opt), and 2) the HybridSA’s CPU-GPU split.

**Benchmarks.** We evaluate the performance of HybridSA over 7 applications, which contain regexes collected from real applications. These benchmarks are: (1) the **Snort** [Roesch 1999; Snort 2024] and (2) **Suricata** benchmarks [Suricata 2024] that contain patterns for network traffic, (3) the **Prosite** benchmark that includes protein motifs from the PROSITE database [Roy and Aluru 2016; Sigrist et al. 2009], (4) the **Yara** [Yara 2024] benchmarks that contain patterns that indicate the presence of viruses, (5) the **SpamAssassin** benchmark [SpamAssassin 2024] that includes patterns for detecting spam email, (6) the **Hamming** and (7) **Levenshtein** datasets containing DNA motifs extracted from the Human genome [Consortium 2022]. Compared to the AutomataZoo [Wadden et al. 2018] benchmark set, our application benchmarks are more up-to-date and contain more regexes. We use 1 GB input (split into input streams of size 8 KB) from real-world applications (PCAP packets, Spam emails, binary viruses, Human genome) for each application.

## 5.1 Classes of Regexes on the GPU

HybridSA excels at executing regexes with structured transition pattern that can be efficiently simulated on the GPU with bitwise operations. Fig. 7 compares the throughput performance of variants of the ShiftAnd, ShiftAndGap, ShiftAndDist and ShiftAndOps kernels on the GPU over 100 batches (i.e. 3200 regexes) and present the kernels used on the GPU per dataset for the GPU part of the hybrid algorithm HybridSA. Table 6 presents the top 10 kernels with highest throughput on the GPU over 100 batches, which corresponds to a dataset of 3200 regexes. All the kernels in the top 10 have a high throughput of more than 100 MB/s, ensuring an efficient execution on the GPU for the regexes that can be executed by those kernels. Note that our implementation is compute-bound, because the GPU simulates the execution of a large number of NFAs for each element of the input. The throughput is relative to the number of regexes in the dataset, and it would increase for a smaller dataset. Therefore, a GPU with more compute resources would enable higher throughput.

**Datatype.** In Table 6, which shows the top 10 kernels with the highest throughput, we only find kernels with datatypes u32 and u64. As expected, ShiftAnd<u32> has the highest throughput at around 220 MB/s, followed by ShiftAndDist<u32, 1> and ShiftAnd<u64>. In general, when we double the bit width of the datatype, we expect the throughput to be roughly divided by 2, given that GPU registers are 32-bit wide. However, when we go from 32-bit to 64-bit, the throughput only decreases from 222 to 180 MB/s for ShiftAnd<u32>, and from 195 down to 124 MB/s for