# A Sub-1-V Capacitively-Biased Voltage Reference With an Auto-Zeroed Buffer and a TC of 18-ppm/°C

Heungsik Eum<sup>✉</sup>, Student Member, IEEE, Kofi A. A. Makinwa<sup>✉</sup>, Fellow, IEEE, Inhee Lee<sup>✉</sup>, Senior Member, IEEE, and Youngcheol Chae<sup>✉</sup>, Senior Member, IEEE

**Abstract**—This brief presents a capacitively-biased CMOS voltage reference, which can operate from a sub-1V supply while achieving a low temperature coefficient (TC) and a competitive power-supply rejection ratio (PSRR). The reference voltage is generated by a capacitive bias circuit that provides a well-defined proportional-to-absolute-temperature (PTAT) bias current for a  $\Delta V_{th}$  type reference that consists of two stacked MOSFETs with different threshold voltages. The generated output voltage is sampled by an auto-zeroed (AZ) buffer, which can drive capacitive loads up to 2 nF. Fabricated in a 65 nm CMOS process, the prototype voltage reference occupies 0.058 mm<sup>2</sup>, including the AZ buffer and an on-chip timing generator. It outputs a reference voltage of 204.1 mV with a minimum supply voltage of 0.7 V. It achieves a TC of 18 ppm/°C from  $-40$  °C to  $85$  °C and a PSRR of  $-75$  dB at 100 Hz with only 200  $\mu$ V ripple.

**Index Terms**—CMOS voltage reference, capacitively-biased circuit, sub-threshold voltage reference, CMOS analog design, sub-1-V, high-precision circuits.

## I. INTRODUCTION

MOST electronic systems require voltage references that must be stable over process, voltage, and temperatures (PVT) variations [1], [2], [3]. The increasing interest in battery-operated portable applications has led to a demand for low-power and low-voltage references. As CMOS processes have scaled down, however, their supply voltage has scaled accordingly. Therefore, a key challenge in scaled CMOS processes is the design of accurate voltage references that can operate at low supply voltages.

Manuscript received 16 June 2024; revised 9 August 2024; accepted 26 August 2024. Date of publication 4 September 2024; date of current version 27 December 2024. This work was supported in part by the Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Science and Information and Communication Technology under Grant NRF-2023R1A2C3005110; in part by the Samsung Electronics; in part by the NSF Awards under Grant 2043017; and in part by the Hewlett International Grant Program. This brief was recommended by Associate Editor E. Moisello. (Corresponding author: Youngcheol Chae.)

Heungsik Eum and Youngcheol Chae are with the Department of Electrical and Electronics Engineering, Yonsei University, Seoul 03722, South Korea (e-mail: ychae@yonsei.ac.kr).

Kofi A. A. Makinwa is with the Microelectronics Department, Delft University of Technology, 2628 Delft, The Netherlands.

Inhee Lee is with the Department of Electrical and Computer Engineering, University of Pittsburgh, Pittsburgh, PA 15260 USA.

Color versions of one or more figures in this article are available at <https://doi.org/10.1109/TCSII.2024.3454348>.

Digital Object Identifier 10.1109/TCSII.2024.3454348

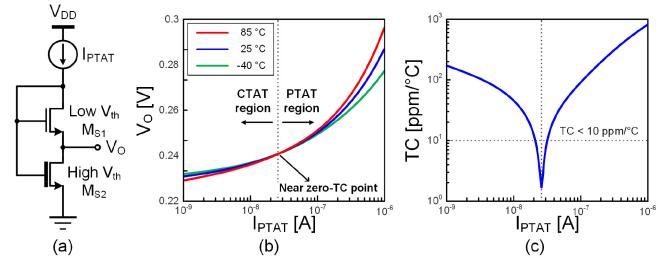

Fig. 1. (a)  $\Delta V_{th}$  voltage reference using  $I_{PTAT}$  bias current and (b) simulated output voltage  $V_O$  and (c) TC versus  $I_{PTAT}$ .

Bandgap references (BGRs) based on BJTs or diodes are well-known for their robustness to PVT variations [4]. They accomplish this by summing proportional-to-absolute-temperature (PTAT) voltages and complementary-to-absolute-temperature (CTAT) voltages generated with the help of precisely biased BJTs [5]. However, despite their accuracy, conventional BGRs require a high supply voltage, making them difficult to use in advanced CMOS processes. Switched-capacitor (SC) techniques can then be employed to realize low-voltage BGRs, which only consume a few tens of nW [6], [7], [8], [9]. Compared to traditional BGRs, however, such references exhibit quite high temperature coefficients (TCs  $>30$  ppm/°C). Recently, a curvature correction scheme improves TCs even at a low supply voltage, along with the SC techniques [10]. However, the numerous switches in the scheme increase its complexity. Furthermore, high-quality BJTs are not always available in advanced CMOS processes. Alternatively, as shown in Fig. 1(a), so-called  $\Delta V_{th}$  voltage references can also be made, which output the threshold voltage difference of two different MOSFETs. They are also quite PVT robust and can operate from low supply voltages while consuming low power, ranging from a few pW to tens of nW [11], [12], [13], [14], [15], [16]. However, their biasing schemes are not defined well, which causes relatively high TCs ( $>50$  ppm/°C).

This brief presents a sub-1-V  $\Delta V_{th}$  voltage reference that is biased by a PTAT current generated by a SC bias circuit. It allows the generation of a well-defined PTAT current, which enables the proposed voltage reference core to achieve a precise voltage with a low TC and competitive PSRR. The reference voltage is subsequently sampled by an auto-zeroed (AZ) buffer that has two output stages, which can then drive

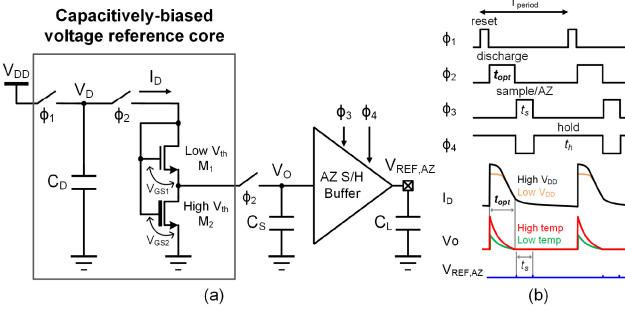

Fig. 2. (a) The proposed capacitively-biased voltage reference and (b) its timing diagram.

significant capacitive loads with minimal ripples, such as the reference buffers of ADCs. Fabricated in a 65 nm CMOS process, the proposed voltage reference generates an output of 204.1 mV from a minimum supply voltage of 0.7 V. It achieves a TC of 18 ppm/°C from -45 to 85 °C and a power supply rejection ratio (PSRR) of -75 dB at 100 Hz.

## II. PROPOSED VOLTAGE REFERENCE

### A. Principle of PTAT-Biased $\Delta V_{th}$ Voltage Reference

Fig. 1(a) illustrates the simplified schematic of the proposed voltage reference, which relies on the  $\Delta V_{th}$  between a thin-oxide (low  $V_{th}$ ) transistor M<sub>S1</sub> and a thick-oxide (high  $V_{th}$ ) transistor M<sub>S2</sub>. Biased by a PTAT current (I<sub>PTAT</sub>), the stacked combination of M<sub>S1</sub> and M<sub>S2</sub> generates an output voltage  $V_O = V_{GS2} - V_{GS1}$ , whose temperature dependence is determined by I<sub>PTAT</sub> and by the characteristics of the two transistors. Fig. 1(b)~(c) shows the simulated  $V_O$  at three different temperatures as a function of I<sub>PTAT</sub>. It can be seen that the temperature dependence of  $V_O$  changes from CTAT to PTAT depending on the magnitude of I<sub>PTAT</sub>. At a certain I<sub>PTAT</sub>,  $V_O$  exhibits a near zero-TC, as can be seen in Fig. 1(c). However, in the chosen 65 nm CMOS process, this current is typically in the order of a few tens of nA, making its precise generation challenging. To address this problem, inspired by [17], [18], a SC- biasing scheme is proposed in this brief.

### B. Proposed Capacitively-Biased Voltage Reference

Fig. 2 shows the proposed capacitively-biased voltage reference and its timing diagram. One operation period  $T_{Period}$  (=80  $\mu$ s) and a capacitor  $C_D$  (=1.9 pF) are selected to make the leakage on  $C_S$  (=0.75 pF) negligible. During a reset phase ( $\phi_1$ ),  $C_D$  is initially charged to the supply voltage  $V_{DD}$ . In the subsequent discharge phase ( $\phi_2$ ),  $C_D$  is discharged via the stacked diode-connected MOSFETs, resulting in a time-varying  $V_O$  ( $=V_{GS2} - V_{GS1}$ ). After an initial transient, the stacked MOSFETs will enter the weak inversion region, and the voltage  $V_D$ , along with its discharging bias current  $I_D$ , will be solely determined by their exponential I-V characteristic, regardless of the initial  $V_{DD}$ . Fig. 3(a) shows that after a brief (here, after 1  $\mu$ s),  $V_D$  decreases logarithmically as a function of CTAT. As depicted in Fig. 3(b),  $I_D$  becomes an approximately PTAT current, given by  $mC_DV_T/t$ , where  $m$  is the slope factor of M<sub>2</sub>,  $V_T$  is the thermal voltage,

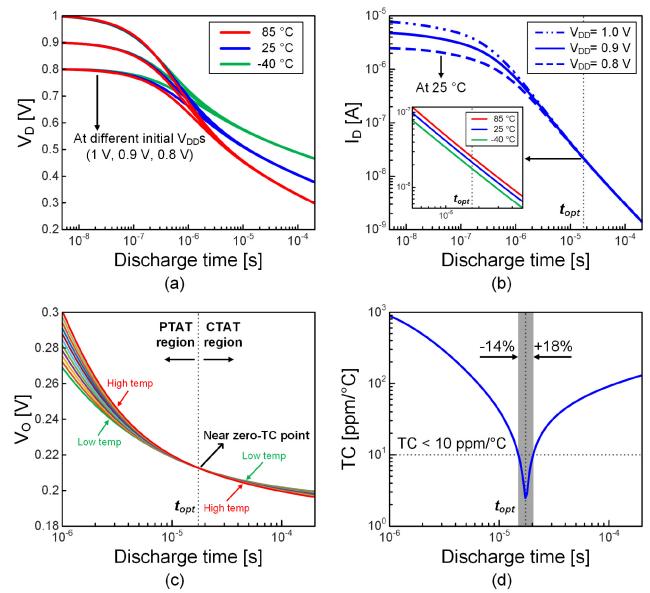

Fig. 3. Simulation results of the core of the proposed reference: (a) Diode voltage  $V_D$ , (b) discharge current  $I_D$ , (c) output voltage  $V_O$ , and (d) TC versus discharge time.

and  $t$  is the discharge time. The simulation results of  $V_O$  versus the discharge time are shown in Fig. 3(c)~(d). As  $I_D$  decreases, the temperature dependency of  $V_O$  changes from PTAT to CTAT, and a near zero-TC point exists at  $t_{opt}$  in the middle. And then the resulting  $V_O$  can then be sampled by disconnecting  $C_S$ . As shown in Fig. 2, an AZ S/H buffer with high input impedance and low offset is employed to drive an external load. The AZ S/H buffer samples  $V_O$  during a sample/AZ phase ( $\phi_3$ ) and generates a low-offset copy  $V_{REF,AZ}$  during a hold phase ( $\phi_4$ ). All the pulses are generated by an on-chip timing generator, enabling the voltage reference from an external clock.

The two different transistors in Fig. 2, M<sub>1</sub> and M<sub>2</sub>, are used to generate  $\Delta V_{th}$ . The sizes of M<sub>1</sub> ( $W/L_1 = 10/1 \mu\text{m}/\mu\text{m}$ ) and M<sub>2</sub> ( $W/L_2 = 4.2/8.4 \mu\text{m}/\mu\text{m}$ ) are selected to minimize the leakage of M<sub>1</sub> and optimize the TC of  $V_O$ . In simulation, the lowest TC of  $\sim 2.7 \text{ ppm/}^\circ\text{C}$  is achieved at  $t_{opt}$  ( $=17.5 \mu\text{s}$ ) generating  $V_O$  of about 0.2 V. The TC remains below 10 ppm/°C even when the discharge time varies over a wide range (-14% to +18%) around  $t_{opt}$ . Monte-Carlo simulations show that the corresponding variation of  $V_O$  is approximately  $\pm 3.6 \text{ mV}$  ( $\pm 1.8\%$ ). As shown in Fig. 3(b), at  $t_{opt}$ , the required  $I_D$  is in the order of a few tens of nA (17.5, 21.4, and 25.1 nA at -40, 25, and 85 °C, respectively) even with a  $V_{DD}$  variation from 0.8 to 1 V. These results indicate that the reference core can be operated at a sub-1-V supply, and that the TC of  $V_O$  is robust to variations in the discharge time.

### C. Auto-Zeroed Sample-and-Hold Buffer

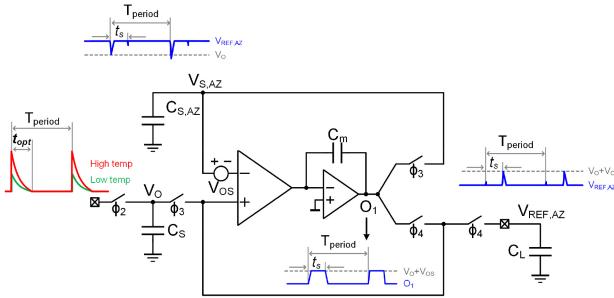

As shown in Fig. 4, the output node ( $O_1$ ) of the buffer with a single output stage switches between  $V_O$  and  $V_O + V_{OS}$ , causing large ripples at the boundary of two phases. To suppress the ripples, splitting it into two output stages is more effective, where the output stages maintain each output

Fig. 4. Schematic of the auto-zeroed sample-and-hold buffer with single output stage.

Sample/AZ phase

Hold phase

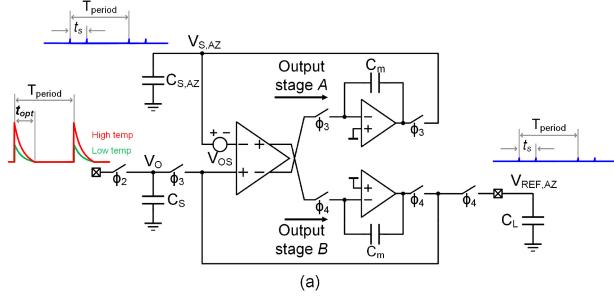

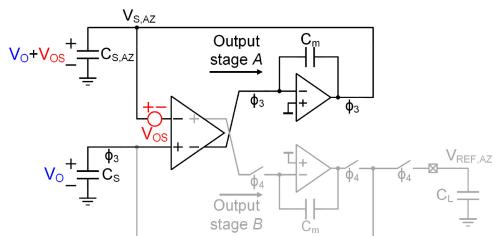

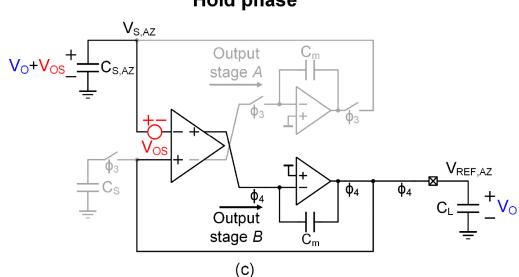

Fig. 5. (a) Schematic of the proposed auto-zeroed sample-and-hold buffer, and operation in (b) sample/AZ phase and (c) hold phase.

voltage. Fig. 5 shows the proposed buffer that consists of a single input stage that alternately drives two output stages. While one output stage (A) drives an on-chip sample/AZ capacitor  $C_{S,AZ}$  ( $=3.8\text{ pF}$ ), which copies  $V_O$  during the sample/AZ phase, the other output stage (B) drives the load capacitor ( $C_L$ ). During the sample/AZ phase ( $\phi_3$ ), the buffer is configured for unity gain via the first output stage (A), and thus stores  $V_O + V_{OS}$  on  $C_{S,AZ}$ , where  $V_{OS}$  is the buffer's offset voltage. In the subsequent hold phase ( $\phi_4$ ), the buffer is configured to unity gain via the second output stage (B), canceling its offset and transferring  $V_O$  to the output capacitive load up to 2 nF. To achieve low-offset, the input stage has a

Fig. 6. Measured  $V_{REF,AZ}$  at  $-40$ ,  $25$ , and  $85$   $^{\circ}\text{C}$ .

(a)

(b)

(c)

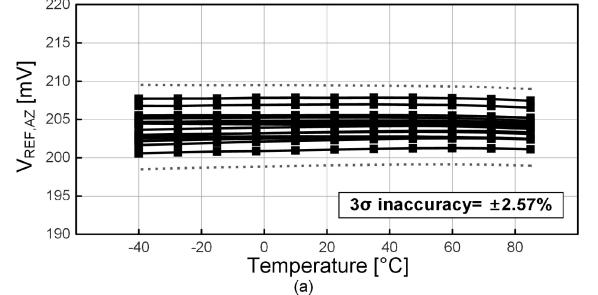

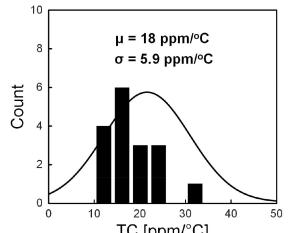

Fig. 7. (a) Measured inaccuracy, and distribution of (b)  $V_{REF,AZ}$  and (c) TC at  $t_{opt}$ .

gain of  $>53$  dB over PVT. The amplifier's open-loop gain is  $>85$  dB, ensuring that its initial offset can be suppressed to the micro-volt level. The buffer's simulated offset voltage remains within  $10\text{ }\mu\text{V}$  over PVT, which is negligible compared to the expected spread in  $V_O$ . At room temperature, the integrated noise of the buffer is  $50\text{ }\mu\text{V}_{\text{rms}}$ .

### III. MEASUREMENT RESULTS

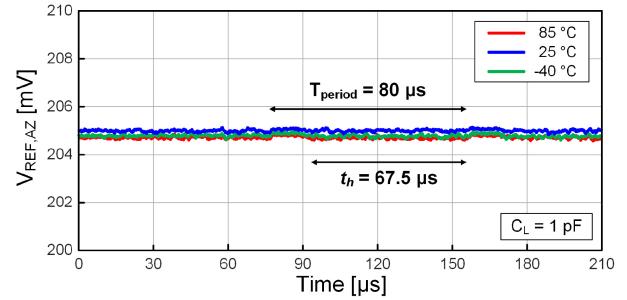

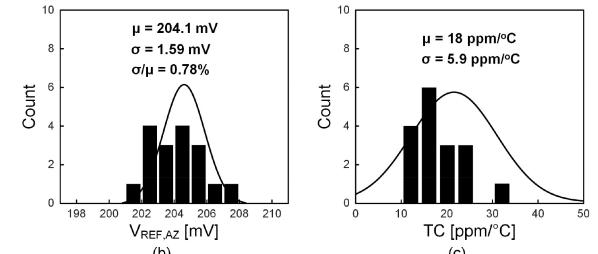

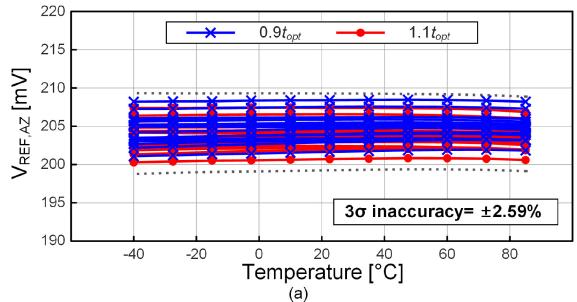

The prototype reference is fabricated in a 65 nm CMOS process. An external reference clock is employed for testing. The measurements were carried out on 17 samples in ceramic DIL packages. As shown in Fig. 6, using a load capacitor  $C_L$  of 1 pF and a hold time  $t_h$  of  $67.5\text{ }\mu\text{s}$ , the measured  $V_{REF,AZ}$  has an output ripple of  $200\text{ }\mu\text{V}$  caused by the residual charge injection of switches in the S/H buffer. The distribution of  $V_{REF,AZ}$  is depicted in Fig. 7. The measured  $3\sigma$ -inaccuracy is  $\pm 2.57\%$  at  $t_{opt}=17.5\text{ }\mu\text{s}$ . The measured mean ( $\mu$ ) and standard deviation ( $\sigma$ ) of  $V_{REF,AZ}$  are  $204.1\text{ mV}$  and  $1.59\text{ mV}$ , respectively, corresponding to a  $\sigma/\mu$  ratio of  $0.78\%$ . The measured TC is  $18\text{ ppm/}^{\circ}\text{C}$  with a spread of  $5.9\text{ ppm/}^{\circ}\text{C}$ . To assess its robustness to timing errors, the distribution of  $V_{REF,AZ}$  is also measured at  $0.9t_{opt}$  and  $1.1t_{opt}$ , as shown in Fig. 8. The  $3\sigma$ -inaccuracy and the  $\sigma/\mu$  ratio remain consistent

Fig. 8. (a) Measured inaccuracy, distribution of (b)  $V_{\text{REF},\text{AZ}}$  and (c) TC at  $0.9t_{\text{opt}}$ , and distribution of (d)  $V_{\text{REF},\text{AZ}}$  and (e) TC at  $1.1 t_{\text{opt}}$ .

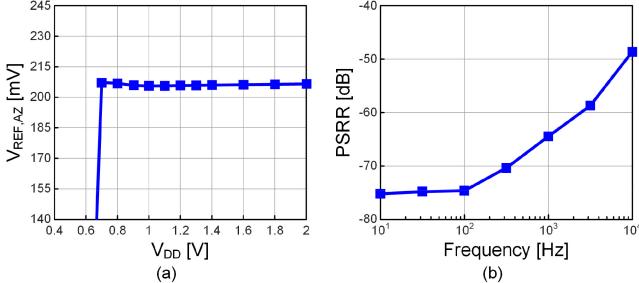

Fig. 9. (a) Measured  $V_{\text{REF},\text{AZ}}$  versus  $V_{\text{DD}}$  and (b) PSRR.

at  $\pm 2.59\%$  and  $0.78\%$ , respectively. Although the TC and  $V_{\text{REF},\text{AZ}}$  vary slightly by  $3.2 \text{ ppm}^{\circ}\text{C}$  and  $0.9 \text{ mV}$ , respectively, these results confirm the reference's robustness to timing variations.

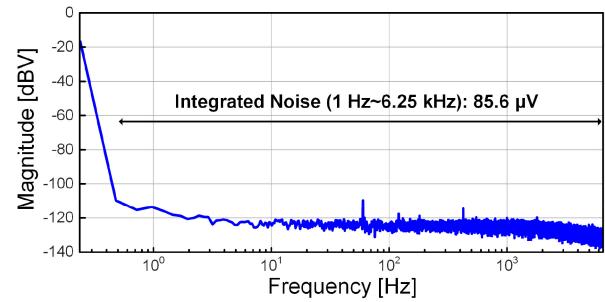

As shown in Fig. 9(a), the reference can be operated from supply voltages ranging from 0.7 to 2 V. In Fig. 9(b), a measured PSRR of  $-75 \text{ dB}$  is attained at 100 Hz. Fig. 10 presents the measured noise spectrum, which shows that the total integrated noise from 1 Hz to 6.25 kHz is  $85.6 \mu\text{V}_{\text{rms}}$  mainly limited by the sampling noise of  $C_S$  ( $=0.75 \text{ pF}$ ). Under a 0.8 V supply at 25 °C, the power consumption including the buffer and the timing generator is  $10 \mu\text{W}$ , chosen to drive external loads and accommodate AC performance assessment of the reference core precisely under a wide range of test

Fig. 10. Measured output noise spectrum.

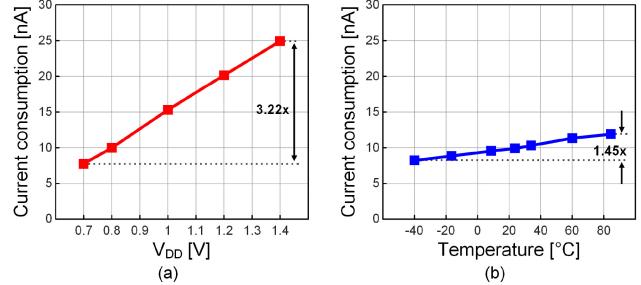

Fig. 11. Current consumption of the reference core at different (a) supply voltages and (b) temperatures.

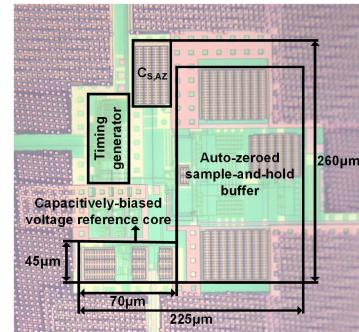

Fig. 12. Chip micrograph.

conditions. Fig. 11 shows that the reference core's current consumption increases by a factor of 3.22 as the supply voltage ranges from 0.7 to 1.4 V. Also, the current consumption varies by a factor of 1.45 from  $-40 \text{ }^{\circ}\text{C}$  to  $85 \text{ }^{\circ}\text{C}$ , which is significantly smaller than leakage-based voltage reference ( $300\times$  in [12]). Fig. 12 shows the chip micrograph that occupies a core area of  $3,150 \mu\text{m}^2$  and a total area of  $0.058 \text{ mm}^2$ .

Table I provides performance summary and comparison to previous sub-1-V SC-based references. This brief provides the lowest TC and a competitive PSRR with small ripples compared to prior sub-1-V references based on BJT [6], [7], [9],  $\Delta V_{\text{th}}$  [13], and diode [18]. Furthermore, due to the SC technique and its simplicity, it is also suitable for IoT applications, similar to [9].

#### IV. CONCLUSION

This brief presents a sub-1V CMOS voltage reference. Thanks to its capacitively-biased  $\Delta V_{\text{th}}$  reference architecture, compared with prior sub-1-V SC-based voltage references,

TABLE I

PERFORMANCE SUMMARY AND COMPARISON TO PREVIOUS

SC-BASED REFERENCES

| Publication                   | This Work       | [6]                   | [7]             | [13]                | [9]                 | [18]       |

|-------------------------------|-----------------|-----------------------|-----------------|---------------------|---------------------|------------|

| Technology                    | 65nm            | 130nm                 | 130nm           | 65nm                | 65nm                | 16nm       |

| Reference Core                | $\Delta V_{th}$ | BJT                   | BJT             | $\Delta V_{th}$     | BJT                 | Diode      |

| Including buffer              | Yes             | Yes                   | No              | No                  | No                  | No         |

| Min. $V_{DD}$ [V]             | 0.7             | 0.75                  | 0.5             | 0.62                | 0.5                 | 0.85       |

| Temp. range [°C]              | -40 to 85       | -20 to 85             | 0 to 80         | -25 to 110          | -40 to 120          | -20 to 110 |

| TC (μ) [ppm/°C]               | 18              | 40                    | 75 <sup>†</sup> | 108                 | 38                  | < 52       |

| $V_{REF}$ [mV]                | 204.1           | 256                   | 500             | 389.9               | 503                 | 370        |

| $\sigma/\mu$ [%]              | 0.78            | 1                     | 0.67            | 1                   | 0.46                | 0.24       |

| Output ripple                 | 200 μV          | 20mV                  | 50μV            | 100μV <sup>††</sup> | 200μV <sup>††</sup> | -          |

| # of chips                    | 17              | 180                   | 6               | 15                  | 10                  | 10         |

| PSRR @100 dB                  | -75             | -86                   | -40             | -62                 | -50                 | -49        |

| Core power [nW]               | 8               | 15 - 20               | 19.7            |                     | 24                  | 18         |

| Total power [nW]              | 10,000          | 170                   | 32              |                     |                     | 388        |

| Core area [μm <sup>2</sup> ]  | 3,150           | 20,000 <sup>†††</sup> |                 | 26,400              | 77,000              | 42,500     |

| Total area [μm <sup>2</sup> ] | 58,500          | 70,000                |                 |                     |                     | 1,680      |

<sup>†</sup>Best TC <sup>††</sup>Simulated <sup>†††</sup>Estimated

the proposed voltage reference achieves the lowest TC of 18 ppm/°C, which is also robust to its  $t_{opt}$  variations. It also provides 204.1 mV at a minimal supply voltage of 0.7 V and features a PSRR of -75 dB at 100 Hz, while maintaining a core power of 8 nW and occupying only a core area of 3,150  $\mu\text{m}^2$ . An AZ S/H buffer is used to drive external (capacitive) loads with low-offset and only 200  $\mu\text{V}$  of output ripple.

## APPENDIX

### THEORETICAL ANALYSIS OF THE PROPOSED VOLTAGE REFERENCE CORE

In this section, the proposed voltage reference during the discharge phase is theoretically analyzed. To simplify the expression, the derivation with partial differentiation is omitted. Assuming  $V_{DS} \gg V_T$ , its drain current is expressed by

$$I_D = \mu C_{DEP} \left( \frac{W}{L} \right) V_T^2 \exp \left( \frac{V_{GS} - V_{TH}}{mV_T} \right) = I_0 \exp \left( \frac{V_{GS} - V_{TH}}{mV_T} \right), \quad (1)$$

where  $\mu$  is the carrier mobility,  $C_{DEP}$  is the depletion capacitance,  $W$  and  $L$  are the width and length of the NMOS respectively,  $V_T$  is the thermal voltage,  $V_{GS}$  and  $V_{TH}$  are the gate-source voltage and threshold voltage of the NMOS respectively, and  $m$  is the slope factor of the transistor. The capacitor discharge with diode-connected NMOS ( $M_2$ ) in Fig. 2 is approximately expressed by

$$V_{GS2}(t) = -m_2 V_T \ln \left( \frac{I_{O2} t}{C_{Dm2} V_T} \right) + V_{TH2}. \quad (2)$$

Applying (2) to (1), the capacitive bias circuit generates a  $V_{DD}$ -insensitive current after a short time and is expressed as

$$I_D = \frac{C_{Dm2} V_T}{t}. \quad (3)$$

Finally, considering  $V_O = V_{GS2} - V_{GS1}$  with the same  $I_D$ , the output voltage  $V_O$  can be given by

$$V_O(t) = (m_1 - m_2) V_T \ln \left( \frac{I_{O2} t}{C_{Dm2} V_T} \right) + m_1 V_T \ln \left( \frac{I_{O1}}{I_{O2}} \right) + \Delta V_{TH}. \quad (4)$$

The first term has CTAT characteristics that vary with the discharge time  $t$ , while the other terms have time-invariant PTAT characteristics. With the discharge time, the thermal property of  $V_O$  changes from PTAT to CTAT, and there is a zero-TC point of  $V_O$  at  $t_{opt}$  in the middle. As a result,  $V_O$  can be expressed as

$$V_O(t_{opt}) = V_{TH2} - V_{TH1}. \quad (5)$$

## REFERENCES

- [1] Z. Tang et al., “3.4 A 14b 98Hz-to-5.9kHz 1.7-to-50.8  $\mu\text{W}$  BW/power scalable sensor interface with a dynamic bandgap reference and an untrimmed gain error of  $\pm 0.26\%$  from -40°C to 125°C,” in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, 2024, pp. 60–62.

- [2] J.-H. Boo et al., “A single-trim switched capacitor CMOS bandgap reference with a 3σ inaccuracy of +0.02%, -0.12% for battery-monitoring applications,” *IEEE J. Solid-State Circuits*, vol. 56, no. 4, pp. 1197–1206, Apr. 2021.

- [3] C. Lee et al., “A miniaturized wireless neural implant with body-coupled power delivery and data transmission,” *IEEE J. Solid-State Circuits*, vol. 57, no. 11, pp. 3212–3227, Nov. 2022.

- [4] H. Banba et al., “A CMOS bandgap reference circuit with sub-1V operation,” *IEEE J. Solid-State Circuits*, vol. 34, no. 5, pp. 670–674, May 1999.

- [5] R. J. Widlar, “New developments in IC voltage regulators,” *IEEE J. Solid-State Circuits*, vol. 6, no. 1, pp. 2–7, Feb. 1971.

- [6] V. Ivanov et al., “An ultra low power bandgap operational at supply from 0.75 V,” *IEEE J. Solid-State Circuits*, vol. 47, no. 7, pp. 1515–1523, Jul. 2012.

- [7] A. Shrivastava et al., “5.4 A 32nW bandgap reference voltage operational from 0.5V supply for ultra-low power systems,” in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, 2015, pp. 1–3.

- [8] U. Chi-Wa, W.-L. Zeng, M.-K. Law, C.-S. Lam, and R. P. Martins, “A 0.5-V Supply, 36 nW bandgap reference with 42 ppm/°C average temperature coefficient within -40 °C to 120 °C,” *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 67, no. 11, pp. 3656–3669, Nov. 2020.

- [9] C.-W. U, M.-K. Law, C.-S. Lam, and R. P. Martins, “Switched-capacitor bandgap voltage reference for IoT applications,” *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 69, no. 1, pp. 16–29, Jan. 2022.

- [10] C.-F. Lee, C.-W. U, R. P. Martins, and C.-S. Lam, “A 0.5V 22.5ppm/°C bandgap voltage reference with leakage current injection for curvature correction,” *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 70, no. 10, pp. 3897–3901, Oct. 2023.

- [11] C.-Z. Shao et al., “A 1.8-nW, -73.5-dB PSRR, 0.2-ms startup time, CMOS voltage reference with self-biased feedback and capacitively coupled schemes,” *IEEE J. Solid-State Circuits*, vol. 56, no. 6, pp. 1795–1804, Jun. 2021.

- [12] L. Fassio, L. Lin, R. De Rose, M. Lanuzza, F. Crupi, and M. Alioto, “Trimming-less voltage reference for highly uncertain harvesting down to 0.25 V, 5.4 pW,” *IEEE J. Solid-State Circuits*, vol. 56, no. 10, pp. 3134–3144, Oct. 2021.

- [13] M. Liu, K. Pelzers, R. van Dommele, A. van Roermund, and P. Harpe, “A106nW 10 b 80 kS/s SAR ADC with duty-cycled reference generation in 65 nm CMOS,” *IEEE J. Solid-State Circuits*, vol. 51, no. 10, pp. 2435–2445, Oct. 2016.

- [14] K. Yu et al., “A 0.5V 22.5ppm/°C bandgap voltage reference with leakage current injection for curvature correction A 23-pW NMOS-only voltage reference with optimum body selection for process compensation,” *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 69, no. 11, pp. 4213–4217, Nov. 2022.

- [15] J. Wang et al., “A Picowatt CMOS voltage reference operating at 0.5-V power supply with process and temperature compensation for low-power IoT systems,” *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 70, no. 4, pp. 1336–1340, Apr. 2023.

- [16] C. Che et al., “A 0.4-V 8400- $\mu\text{m}^2$  voltage reference in 65-nm CMOS exploiting well-proximity effect,” *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 70, no. 10, pp. 3822–3826, Oct. 2023.

- [17] M. Eberlein et al., “A 40nW, Sub-IV truly ‘digital’ reverse bandgap reference using bulk-diodes in 16nm FinFET,” in *Proc. IEEE Asian Solid-State Circuits Conf. (A-SSCC)*, 2018, pp. 99–102.

- [18] M. Eberlein et al., “Time-controlled and FinFET compatible sub-bandgap references using bulk-diodes,” *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 66, no. 10, pp. 1608–1612, Oct. 2019.