# High-Performance $\text{TiO}_2$ Thin-Film Transistors: In-Depth Investigation of the Correlation between Interface Traps and Oxygen Vacancies

Chandan Samanta, Saravanan Yuvaraja, Tuofu Zhama, Haochen Zhao, Lars Gundlach, and Yuping Zeng\*

Cite This: *ACS Appl. Electron. Mater.* 2024, 6, 5575–5585

Read Online

ACCESS |

Metrics & More

Article Recommendations

Supporting Information

**ABSTRACT:** The role of surface contamination, along with surface oxygen vacancies, plays a key role in the overall carrier transport in thin-film transistors (TFTs). In this study, it is shown that the quality of the semiconductor/dielectric interface and the surface roughness of the channel can be improved by  $\text{O}_2$  annealing of the  $\text{TiO}_2$  channel and subsequent  $\text{N}_2\text{O}$  treatment. It has been observed that the surface contamination related to carbonaceous compounds by  $\text{O}_2$  annealing at  $500\text{ }^\circ\text{C}$  (sample C500) is substantially reduced by 61% in comparison to that annealed at  $375\text{ }^\circ\text{C}$  (sample C375), which leads to a reduction of interface state traps ( $D_{it}$ ) at the channel/dielectric interface. TFTs with a higher  $\text{O}_2$  annealing temperature (C500) exhibit an SS of  $88\text{ mV/dec}$ , an  $I_{ON}/I_{OFF}$  of  $\sim 10^9$ , and a mobility  $\mu_{FE}$  of  $1.5\text{ cm}^2/\text{V}\cdot\text{s}$  under a battery-powered voltage of  $1\text{ V}$ . In contrast, the sample C375 results in greater donor states such as surface oxygen vacancies ( $V_{os}$ ), and the transistors exhibit a mobility  $\mu_{FE}$  of  $2.95\text{ cm}^2/\text{V}\cdot\text{s}$  and an  $I_{ON}/I_{OFF}$  of  $\sim 10^9$ , despite a degradation of the SS value ( $123\text{ mV/dec}$ ) due to the large number of interface states. Therefore, to fabricate high-performance devices, it is possible to tune the optimum values of surface contamination and oxygen vacancies by adjusting the  $\text{O}_2$  annealing temperature. Also, these TFTs show excellent stability under both negative bias stress (NBS) and positive gate bias stress (PBS) in the dark as well as with laser illumination with minimal modifications of the electrical characteristics upon both gate stresses up to  $1800\text{ s}$ , suggesting the feasibility of our  $\text{TiO}_2$  TFTs for practical applications. A low gate leakage and  $I_{OFF}$  current, as well as high-performance electrical characteristics, make the ICs ideal for low-power internet of things (IoT) applications.

**KEYWORDS:** wide-bandgap semiconductor, oxide electronics,  $\text{TiO}_2$ , TFT, interface state

## 1. INTRODUCTION

The growing popularity of the internet of things (IoT) has led to increased demand for portable electronic devices. Consequently, there is a significant push to develop high-quality thin-film transistors (TFTs) capable of low-power operation. This is particularly important for emerging technologies such as foldable screens and wearable sensors. Among various devices, metal-oxide thin-film transistors (TFTs) have been receiving considerable attention in the field of electronics due to their superior properties over silicon-based TFTs. These properties include high optical transparency, impressive carrier mobility, excellent uniformity, and simpler production processes. High-performance metal-oxide TFTs, utilizing channel materials such as  $\text{InGaZnO}$ ,  $\text{SiInZnO}$ ,  $\text{ZnSnO}$ ,  $\text{SiZnSnO}$ ,  $\text{InZnO}$ , and  $\text{In}_2\text{O}_3$ , have demonstrated remarkable potential in various applications.<sup>1–4</sup> These

applications include active matrix displays, RFID tags, and logic circuits, showcasing the versatility of these transistors. However, a major challenge with these advanced TFTs is their reliance on  $\text{ZnO}$ -related compound semiconductors. The use of scarce and costly elements such as indium and gallium in these compounds significantly hampers their widespread application and scalability. Consequently, the industry is facing a pressing need for high-performance TFTs that utilize more

Received: March 26, 2024

Revised: June 27, 2024

Accepted: June 27, 2024

Published: July 16, 2024

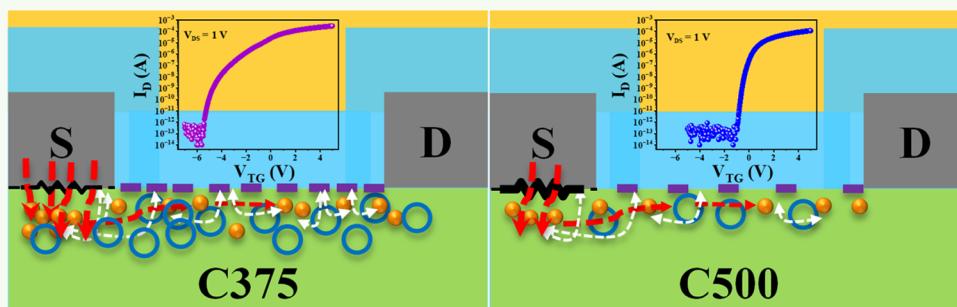

**Figure 1.** (a) Three-dimensional (3D) view and (b) cross-sectional view of the fabricated TiO<sub>2</sub> thin-film transistors (TFTs) with the same device dimensions. (c) Top-view microscopy image of the fabricated TiO<sub>2</sub> TFTs. (d) Grazing incidence X-ray diffraction (GI-XRD) spectrum of O<sub>2</sub>-annealed TiO<sub>2</sub> films with different temperatures. AFM images for chips (e) C375 and (f) C500.

cost-efficient and readily available materials, especially for large-scale electronic applications.

Titanium oxide (TiO<sub>2</sub>) has emerged as a promising solution in this context. TiO<sub>2</sub> stands out due to its chemical and mechanical stability, nontoxic nature, cost-effective growth methods, and abundance on earth. These properties position TiO<sub>2</sub> as an ideal candidate for channel materials in TFT applications. Recent developments have led to the successful fabrication of TiO<sub>2</sub>-based TFTs, which have demonstrated performance levels comparable to their InGaZnO counterparts.<sup>5–7</sup> For instance, Katayama et al. developed a field-effect transistor (FET) using a rutile TiO<sub>2</sub> active channel, employing an amorphous LaAlO<sub>3</sub> insulator on ultrasmooth rutile single crystals. This structure, achieving reproducible n-type FET action with aluminum as the source/drain contact, displayed notable anisotropy in field-effect mobility.<sup>8</sup> The introduction of a MgO insulating buffer layer between TiO<sub>2</sub> and LaAlO<sub>3</sub> reduced the off-state current, achieving a decent on-to-off current ratio of 10<sup>4</sup> and a poor subthreshold swing (SS) (>3 V/dec). The team also proposed an oxygen modulation method for growing high-quality anatase films.<sup>9</sup> This method involved alternating deposition under low oxygen pressure with annealing under high oxygen pressure, enhancing the crystallinity of the film and resulting in high resistivity. The anatase film exhibited superior performance in FETs, with an on-to-off current ratio over 10<sup>5</sup> and a field-effect mobility exceeding 0.3 cm<sup>2</sup>/V-s. There is another report on the fabrication of n-type TiO<sub>x</sub> TFTs, with Al as the source/drain contact, using metal–organic chemical vapor deposition at 250 °C, achieving ideal characteristics.<sup>10</sup> Through optimal N<sub>2</sub>O plasma treatment, they successfully reduced the off-current, significantly improving the on-to-off ratio without affecting the on-current.<sup>11</sup> This method resulted in a significant increase in the on-to-off ratio by almost 5 orders of magnitude. However, the reported device exhibited a poor subthreshold swing of 1.47 V/dec. In a separate study, Park et al. enhanced the performance of n-type TiO<sub>x</sub> TFTs with plasma-enhanced atomic layer deposition (ALD).<sup>12</sup> Here, the source/drain contacts were made of Al. The N<sub>2</sub>O plasma treatment improved the on-to-off ratio to 4.7 × 10<sup>5</sup> with a saturation mobility of 1.64 cm<sup>2</sup>/V-s. Also, Choi et al. fabricated an amorphous TiO<sub>2</sub> channel-based oxide TFT, with molybdenum as the source/drain contact, using direct-current magnetron sputtering, achieving notable mobility and on-to-off ratios after

rapid thermal annealing (RTA).<sup>13</sup> Another report, Zhong et al. observed an enhancement in the electrical characteristics of TiO<sub>x</sub> TFTs using SiO<sub>2</sub> as the gate dielectrics post-annealing, which improved the interface structure and TiO<sub>x</sub> crystallinity.<sup>14</sup> After annealing, the device exhibited inferior characteristics such as a high threshold voltage (22.82 V) and a high subthreshold swing (>2 V/dec).

In our recent work, using a two-step annealing process (oxygen (O<sub>2</sub>) annealing at 500 °C followed by nitrous oxide (N<sub>2</sub>O) annealing at 300 °C), we developed a titanium oxide (TiO<sub>2</sub>) transistor that showed good performance, with a subthreshold swing of 92 mV/dec, an off-current  $\sim 10^{-12}$  A, and a saturation current of approximately 2.8  $\mu$ A/ $\mu$ m at a drain–source voltage ( $V_{DS}$ ) of 2 V.<sup>15</sup> In this paper, to further enhance its performance and ultimately obtain a BEOL-compatible fabrication process, we experimented with O<sub>2</sub> annealing at different temperatures. After fine-tuning these annealing conditions, we achieved even better performance in our TiO<sub>2</sub> transistors. The improvements included a lower subthreshold swing of 88 mV/dec and a reduced off-current of around  $10^{-13}$ – $10^{-14}$  A at an operating voltage of 1 V, which make the ICs ideal for low-power IoT applications. To understand how these changes improved the transistor performance, we conducted an in-depth investigation of the interface quality between TiO<sub>2</sub> and zirconium dioxide (ZrO<sub>2</sub>) and its correlation with the oxygen vacancies based on surface-sensitive techniques such as X-ray photoelectron spectroscopy (XPS), photoluminescence (PL), and AC conductance–voltage (G–V) measurements. Additionally, a carrier transport mechanism was proposed, allowing a better understanding of TiO<sub>2</sub> material properties for future electronic and optoelectronic devices.

## 2. RESULTS AND DISCUSSION

Figure 1a–c respectively shows the three-dimensional schematic, cross-sectional view, and top-view microscopic image of the fabricated TiO<sub>2</sub> TFTs. All TFTs have a top gate configuration with different source-to-drain or channel length ( $L_{SD}$ ) values and a fixed gate width ( $L_W$ ) of 70  $\mu$ m with a gate-to-source/drain overlap ( $L_{GS,OV}/L_{GD,OV}$ ) of 1.5  $\mu$ m. The crystal structure of the ALD-deposited TiO<sub>2</sub> film was characterized by X-ray diffraction (XRD). Figure 1d shows the XRD data for TiO<sub>2</sub> films annealed at 375 and 500 °C, wherein both samples exhibit a polycrystalline nature with peaks at 24.8, 37.4, and

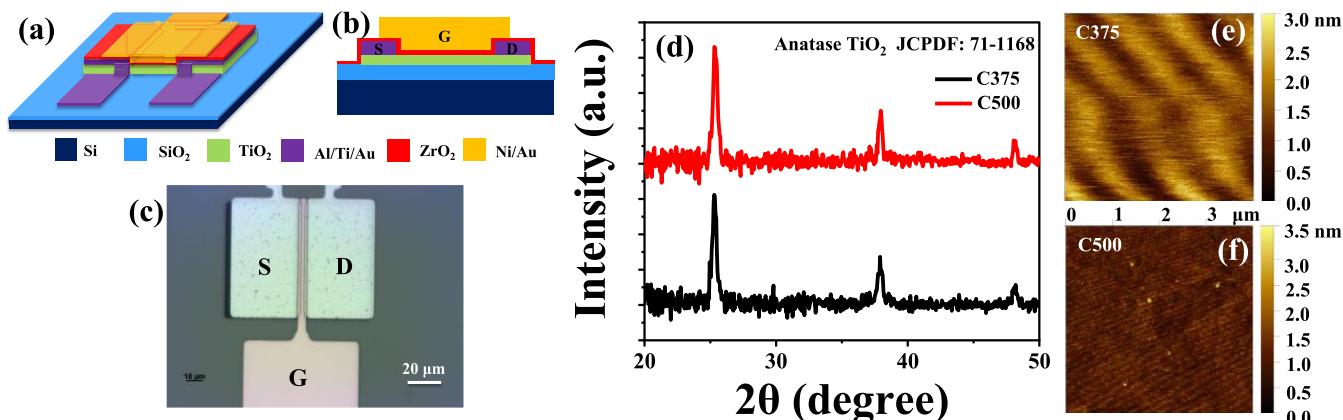

**Figure 2.** STEM-HAADF image of the  $\text{TiO}_2$  device for chips (a) C375 and (b) C500. Cross-sectional TEM images of the layered structure for chips (c) C375 and (d) C500. High-resolution TEM images for the  $\text{TiO}_2/\text{ZrO}_2$  interface of the selected region for chips (e) C375 and (f) C500. The inset shows the fast Fourier transform image of the selected region.

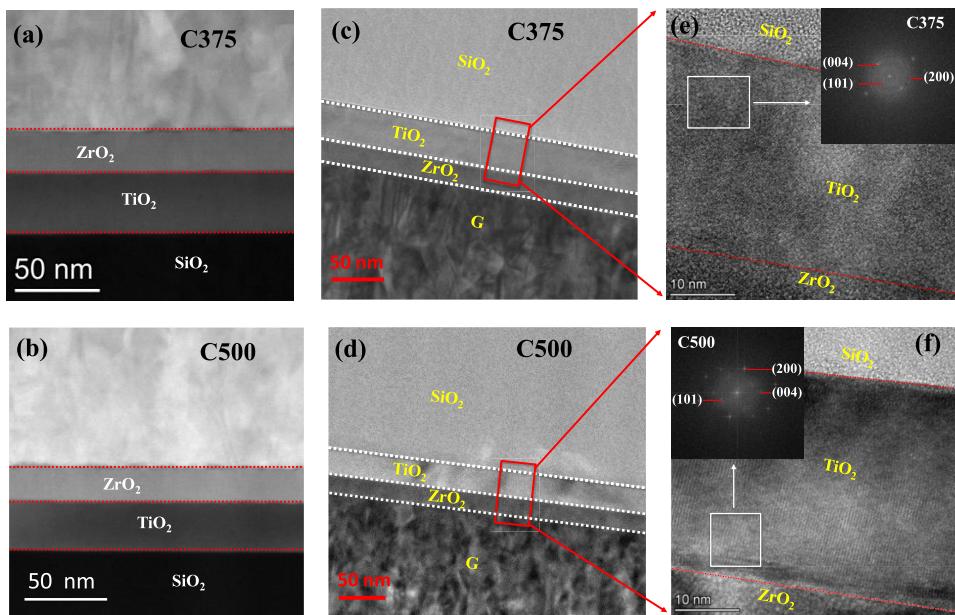

**Figure 3.** Transfer curves ( $I_D - V_{TG}$ ) with different source-to-drain length ( $L_{SD}$ ) values for chips (a) 375 and (b) 500. Transfer curves with different drain voltage  $V_{DS}$  values for a fixed channel length  $L_{SD} = 3 \mu\text{m}$  for chips (c) C375 and (d) C500. The insets show the output characteristics data ( $I_D - V_{DS}$ ) recorded with different top gate voltage ( $V_{TG}$ ) values.

47.6°, corresponding to the (101), (004), and (200) crystal planes of the anatase phase. The surface morphology of the channel is also important for achieving a high-quality channel/dielectric interface. Thus, surface roughness measurement is performed by atomic force microscopy (AFM) after  $\text{O}_2$

annealing and  $\text{N}_2\text{O}$  treatment. Figure 1e,f shows the atomic force microscopy (AFM) image of the  $\text{TiO}_2$  channel with  $\text{N}_2\text{O}$  treatment for chips C375 and C500, respectively. It is seen that  $\text{O}_2$  annealing alone does not significantly affect the root mean square (RMS) surface roughness of the channel data given in

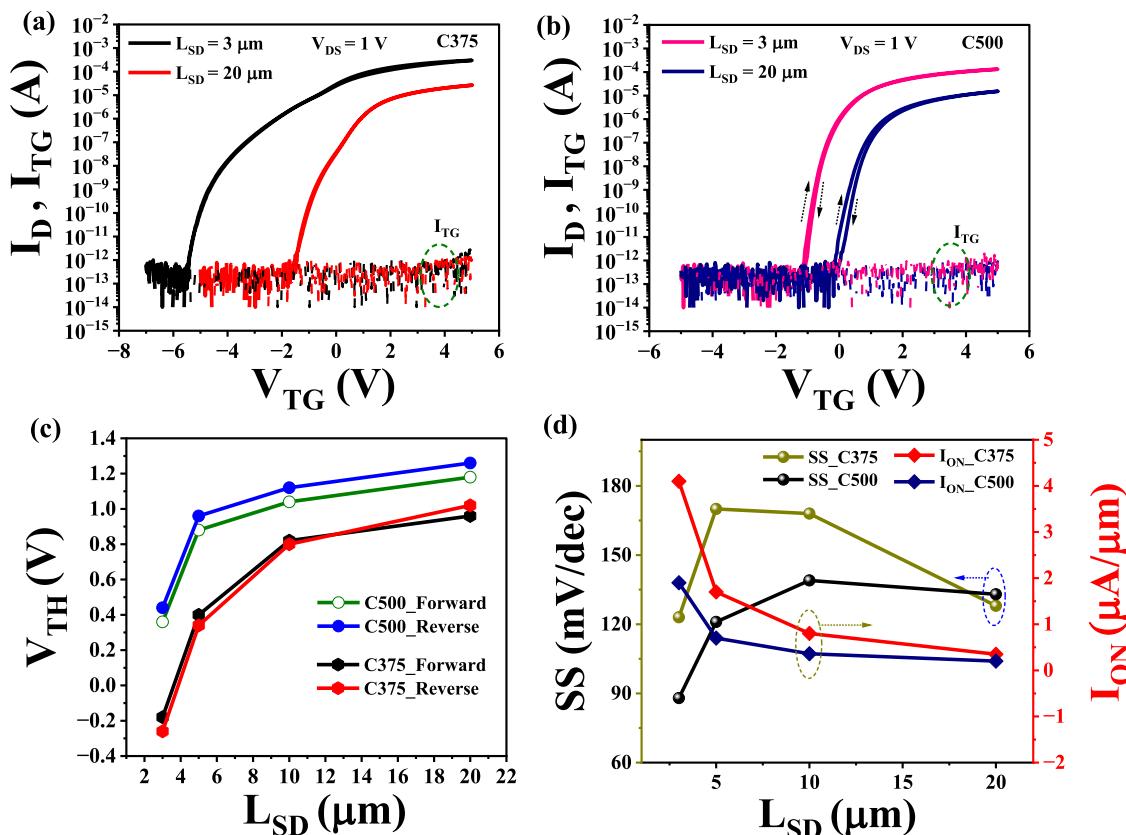

**Figure 4.** Double-sweep transfer curves ( $I_D$ – $V_{TG}$ ) of short-channel ( $L_{SD} = 3 \mu\text{m}$ ) and long-channel ( $L_{SD} = 20 \mu\text{m}$ ) devices with the gate leakage current for chips (a) C375 and (b) C500. (c) Threshold voltage ( $V_{TH}$ ) as a function of the channel length for forward and reverse sweeps for both chips. (d) SS as a function of the channel length ( $L_{SD}$ ) of the TFTs on chips C375 and C500. The right-hand axis in the same graph shows  $I_{ON}$  as a function of  $L_{SD}$ .

the Figure S1, Supporting Information. Interestingly, the RMS surface roughness of the channel reduced substantially from 0.6 to 0.3 nm with  $\text{N}_2\text{O}$  treatment for the chip C500. However, for chip C375, the RMS surface roughness is slightly decreased from 0.51 to 0.43 nm with  $\text{N}_2\text{O}$  treatment.

In order to understand the physical structure (film thickness) and interface quality of  $\text{TiO}_2$  TFT, samples are investigated through cross-sectional transmission electron microscopy (TEM), and the focused ion beam (FIB) technique was employed for cross-sectional sample preparation for the above investigation.

Scanning transmission electron microscopy high-angle annular dark-field (STEM-HAADF) images of  $\text{TiO}_2$  TFTs are shown in Figure 2a,b for chips C375 and C500, respectively. Figure 2c,d shows the cross-sectional TEM images of the  $\text{TiO}_2$  TFT corresponding to chips C375 and C500, respectively. The thickness of the  $\text{TiO}_2$  and  $\text{ZrO}_2$  layers, as depicted in the TEM image, are  $\approx 30$  and  $\approx 20$  nm, respectively. Figure 2e,f further shows the high-resolution TEM image of the  $\text{ZrO}_2/\text{TiO}_2$  interface for chips C375 and C500, respectively. As depicted in the images, the interface between  $\text{ZrO}_2$  and  $\text{TiO}_2$  is very sharp for the high-temperature chip C500 in comparison with the low-processing chip C375, and the lattice structure with different crystal orientations is observed in  $\text{TiO}_2$ , indicating the polycrystalline nature of  $\text{TiO}_2$ .<sup>5</sup> The fast Fourier transform (FFT) image of the selected region is shown in the inset of Figure 2e,f, which predicts better polycrystallinity of the  $\text{TiO}_2$  anatase phase for chip C500 in comparison with chip C375. First, we measured the

electrical characteristics of the two chips C375 and C500 with different channel length ( $L_{SD}$ ) devices.

To understand the effects of  $\text{N}_2\text{O}$  plasma treatment on the electrical properties of the  $\text{TiO}_2$  channel, the  $I_D$ – $V_{DS}$  curves with  $V_{BG} = 0$  V of the  $\text{TiO}_2$  back gate device were tested with the  $\text{N}_2\text{O}$  treatment time and different  $\text{N}_2\text{O}$  flow rates. Data are given in the Figure S2, Supporting Information. The electrical performance of  $\text{TiO}_2$  can be enhanced by a proper  $\text{N}_2\text{O}$  plasma treatment duration, while excessive treatment results in degradation, which agrees with previous reports based on other oxide channels.<sup>16</sup> Figure 3a,c shows the transfer ( $I_D$ – $V_{TG}$ ) curves with different channel lengths for C375 and C500 at  $V_{DS} = 1$  V, respectively, and the right-hand axis in the same graph shows the linear behavior of the drain current  $I_D$  with respect to the channel length. As shown in the figure, the threshold voltage of the devices gradually shifts to the right side with increasing channel length due to more electron trapping in the channel and dielectric interface. Figure 3b,d shows the typical transfer characteristics with different drain voltage  $V_D$  values for a fixed channel length  $L_{SD} = 3 \mu\text{m}$  of chips C375 and C500, respectively. The output characteristics data ( $I_D$ – $V_{DS}$ ) recorded with different top gate voltage ( $V_{TG}$ ) values from -5 to 5 V with steps of 1 V are shown in the inset of Figure 3b,d for chips C375 and C500, respectively. The double-sweep transfer curves ( $I_D$ – $V_{TG}$ ) at  $V_{DS} = 1$  V were recorded to measure the hysteresis of short-channel ( $L_{SD} = 3 \mu\text{m}$ ) and long-channel ( $L_{SD} = 20 \mu\text{m}$ ) devices for both chips C375 and C500, as shown in Figure 4a,b, respectively, and the same graph also shows the gate leakage current ( $I_{TG}$ ). The low

Table 1. Comparisons of This Work with Other  $\text{TiO}_2$  TFTs from the Published Literature<sup>a</sup>

| channel/dielectric            | method     | $V_{\text{DS}}$ (V) | SS (mV/dec) | $\mu_{\text{FE}}$ ( $\text{cm}^2/(\text{V s})$ ) | $I_{\text{ON}}$ ( $\mu\text{A}/\mu\text{m}$ ) | $I_{\text{ON}}/I_{\text{OFF}}$ | references |

|-------------------------------|------------|---------------------|-------------|--------------------------------------------------|-----------------------------------------------|--------------------------------|------------|

| $\text{TiO}_2/\text{ZrO}_2$   | PE-ALD     | 10                  | 112         | 4                                                | 1.42                                          | $1.4 \times 10^8$              | 5          |

| $\text{TiO}_2/\text{ZrO}_2$   | Th-ALD     | 20                  | 101         | 5                                                | 10                                            | $1.2 \times 10^9$              | 6          |

| $\text{TiO}_2/\text{LaAlO}_3$ | PLD        | 100                 | >1000       | 0.3                                              | 0.05                                          | $10^5$                         | 9          |

| $\text{TiO}_2/\text{SiO}_2$   | PE-ALD     | 35                  | 1860        | 1.64                                             | 4.0                                           | $4.7 \times 10^5$              | 12         |

| $\text{TiO}_2/\text{SiO}_2$   | sputtering | 10                  | 2450        | 0.69                                             | 0.03                                          | $2 \times 10^7$                | 13         |

| $\text{TiO}_2/\text{ZrO}_2$   | PE-ALD     | 2                   | 92          | 5.45                                             | 2.8                                           | $2.5 \times 10^8$              | 15         |

| $\text{TiO}_2/\text{SiO}_2$   | sputtering | 10                  | >1000       | 10.7                                             | 1.8                                           | $10^4$                         | 18         |

| $\text{TiO}_2/\text{SiO}_2$   | sputtering | 10                  | >1000       | 0.04                                             | 0.03                                          | $4 \times 10^4$                | 14         |

| $\text{TiO}_2/\text{ZrO}_2$   | Th-ALD     | 20                  | 142         | 2.5                                              | 1.4                                           | $1.4 \times 10^8$              | 19         |

| $\text{TiO}_2/\text{ZrO}_2$   | Th-ALD     | 1                   | 123         | 2.95                                             | 4.1                                           | $10^9$                         | this work  |

| $\text{TiO}_2/\text{ZrO}_2$   | Th-ALD     | 1                   | 88          | 1.5                                              | 1.5                                           | $10^9$                         | this work  |

<sup>a</sup>PE = plasma-enhanced; Th = thermal.

$I_{\text{TG}}$  with a flat curvature in all samples indicates the excellent insulating properties of  $\text{ZrO}_2$ . All TFTs show negligible hysteresis, indicating a smaller number of mobile charges in the dielectric/semiconductor interface. The TFT with a short channel ( $L_{\text{SD}} = 3 \mu\text{m}$ ) in chip C500 shows exceptional switching characteristics, including a high  $I_{\text{ON}}/I_{\text{OFF}}$  ratio of  $\sim 10^9$ , a low subthreshold swing (SS) of 88 mV/dec, and a low off-current of  $\sim 10^{-13} \text{ A}$ . In contrast, the value of SS with a short channel ( $L_{\text{SD}} = 3 \mu\text{m}$ ) device on chip C375 increased to 123 mV/dec due to a large value of the interface state in a low-annealing channel/dielectric interface.

It is noted that SS are extracted over two decades of drain current from  $10^{-12}$  to  $10^{-10} \text{ A}$  according to the equation<sup>15</sup>

$$\text{SS} = \left( \frac{\partial \log(I_{\text{DS}})}{\partial V_{\text{GS}}} \right)^{-1} \quad (1)$$

The steep SS for chip C500 can be ascribed to a possible high-quality channel/dielectric interface with low interface state traps ( $D_{\text{it}}$ ), which will be discussed in detail in the next section. As shown in Figure 4c, the threshold voltage during reverse sweep is shifted to the right (positive) in chip C500, whereas it is shifted to the left (negative) in chip C375 for a short channel length. It has been suggested that this unusual shift may be the result of an irreversible charge–discharge effect in bulk traps that already existed.<sup>17</sup> Moreover, in standard performance devices, the threshold voltage ( $V_{\text{TH}}$ ) shifts positively during fast  $I$ – $V$  double-sweep measurement. However, for short-channel length devices in chip C375, the threshold  $V_{\text{TH}}$  shifts negatively as channel electrons escape from bulk traps to metal gates instead of injecting into bulk traps. Figure 4d shows the variation of SS with channel length ( $L_{\text{SD}}$ ) of the TFTs on chips C375 and C500. The right-hand axis in the same graph shows the  $I_{\text{ON}}$  current as a function of  $L_{\text{SD}}$ , and the value of the  $I_{\text{ON}}$  current decreases with increasing channel length of devices due to a reduced channel resistance.

Interestingly, as shown in the data, the value of the  $I_{\text{ON}}$  current decreased for chip C500 due to an increase in the contact resistance and sheet resistance. The contact resistance ( $R_{\text{C}}$ ) and sheet resistance ( $R_{\text{S}}$ ) measured by the transmission line method (TLM) for chip C500 are 13.5 and 5.3  $\text{k}\Omega$ , respectively (given in the Figure S3, Supporting Information), whereas for chip C375, the values are  $R_{\text{C}} = 6.4 \text{ k}\Omega$  and  $R_{\text{S}} = 2.7 \text{ k}\Omega$ .

The performance of a TFT depends on the quality of the channel as it can give rise to high carrier mobilities. The field-effect mobility ( $\mu_{\text{FE}}$ ) of the carriers in the channel and the

threshold voltage  $V_{\text{TH}}$  of the TFT were calculated using the following conventional equation<sup>15</sup>

$$\mu_{\text{FE}} = \frac{L}{WC_{\text{OX}}V_{\text{DS}}}g_{\text{m}} \quad (2)$$

where  $L$  and  $W$  are the length and width of the device, respectively,  $C_{\text{OX}}$  is the specific gate capacitance obtained by  $C$ – $V$  measurement, and  $g_{\text{m}} = \frac{\partial I_{\text{DS}}}{\partial V_{\text{GS}}}$  is the transconductance.

For chip C375 with a short channel, the extracted value of  $\mu_{\text{FE}}$  is  $2.95 \text{ cm}^2/\text{V}\cdot\text{s}$ , whereas for chip C500, it is  $1.5 \text{ cm}^2/\text{V}\cdot\text{s}$ . In addition, the outstanding electrical performance of  $\text{TiO}_2$  TFTs stands out among the state-of-the-art TFTs based on the  $\text{TiO}_2$  channel and compares favorably with the previous literature reports on  $\text{TiO}_2$  (Table 1).<sup>14,18,19</sup> We also tested multiple devices with the same  $L_{\text{SD}} = 3 \mu\text{m}$  for both chips. The data are shown in Figure S4 (given in the Supporting Information), and deviations in the subthreshold slope (SS) and threshold voltage ( $V_{\text{TH}}$ ) are less than  $\pm 4\%$ , which is important for large-area applications and circuit integration. We tested the aging effect of our  $\text{TiO}_2$  TFT with time and measured the electrical characteristics. As shown in the data (given in the Figure S5, Supporting Information), performance parameters such as subthreshold swing (SS) and threshold voltage ( $V_{\text{TH}}$ ) of  $\text{TiO}_2$  TFTs for both chips degraded barely even after a 4-month time period. We also determined the environmental stability of our  $\text{TiO}_2$  TFTs and measured their electrical characteristics with a relative humidity of up to 80%. The transfer curves of TFTs shifted to negative values for chip C375 because of electron trapping and detrapping at the channel/dielectric interface, whereas no obvious shift was observed for chip C500 (given in the Figure S6, Supporting Information), suggesting the feasibility of our  $\text{TiO}_2$  TFTs for practical applications.

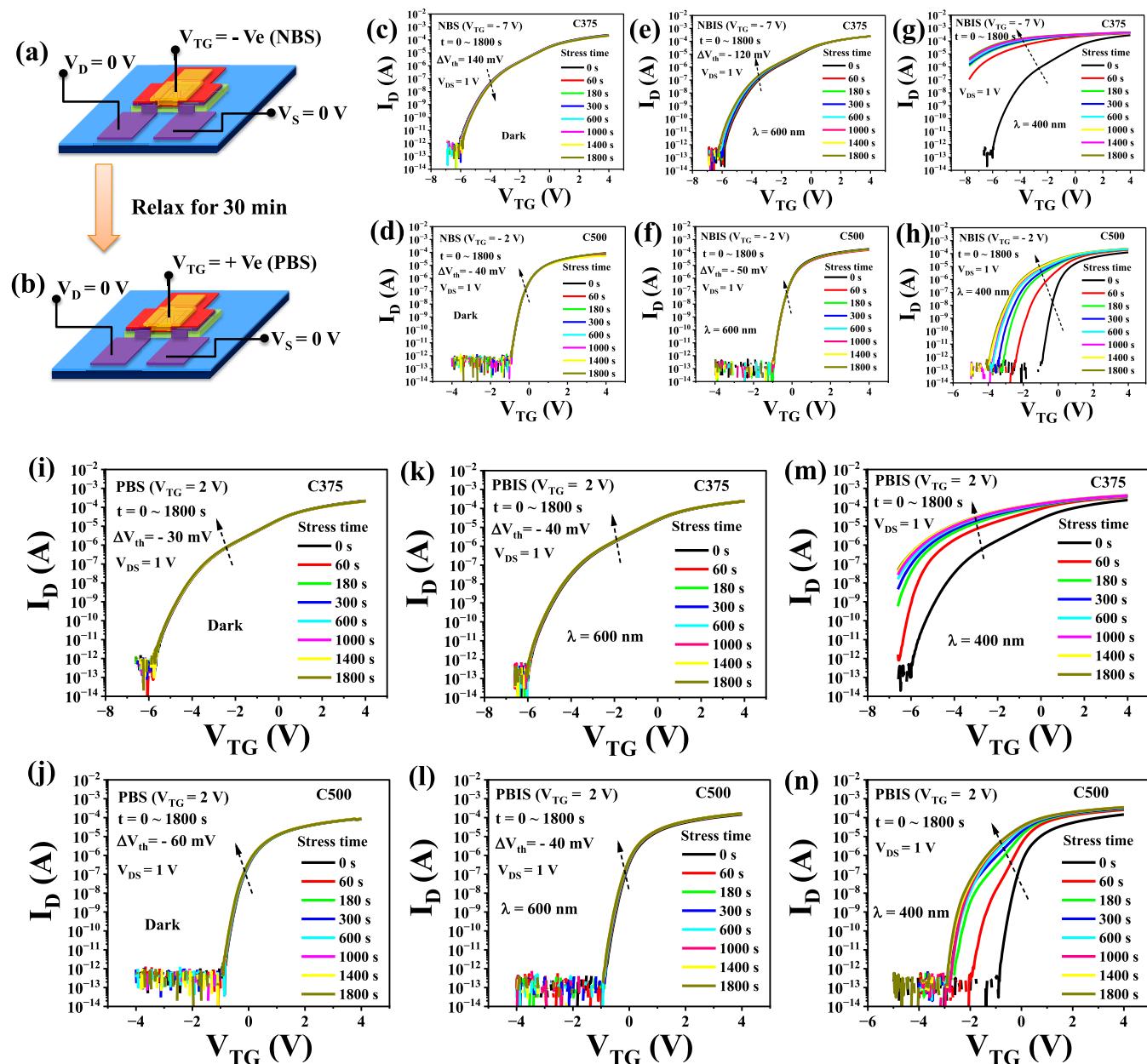

In addition, we also performed a gate bias stability test on  $\text{TiO}_2$  TFTs on the same short-channel device with  $L_{\text{SD}} = 3 \mu\text{m}$  for chips C375 and C500. Figure 5a,b shows the measurement setup (the details are given in the Figure S7, Supporting Information) for  $\text{TiO}_2$  TFTs under negative bias stress (NBS) and positive bias stress (PBS) tests in the dark, while the negative bias illumination stress (NBIS) and positive bias illumination stress (PBIS) tests are performed using laser light with illumination wavelength  $\lambda = 600$  and  $400 \text{ nm}$  and intensity  $I = 150 \text{ mW}/\text{cm}^2$  for a better understanding of the device mechanism in the presence of oxygen vacancies. Figure 5c,d shows the transfer curves of the  $\text{TiO}_2$  TFT under  $V_{\text{DS}} = 1 \text{ V}$  after different accumulated bias times up to 1800 s during negative bias stress in the dark for chips C375 and C500,

**Figure 5.** Measurement setup for  $\text{TiO}_2$  TFTs under (a) negative bias stress (NBS) and (b) positive bias stress (PBS) tests. Transfer curves ( $I_D - V_{TG}$ ) of the  $\text{TiO}_2$  TFT for chips (c) C375 and (d) C500 during the NBS test in the dark. Transfer curves of the  $\text{TiO}_2$  TFT for chips (e) C375 and (f) C500 during the NBIS test with the illumination of light with  $\lambda = 600 \text{ nm}$ . Transfer curves of the  $\text{TiO}_2$  TFT for chips (g) C375 and (h) C500 during the NBIS test with the illumination of light with  $\lambda = 400 \text{ nm}$ . Transfer curves ( $I_D - V_{TG}$ ) of the  $\text{TiO}_2$  TFT for chips (i) C375 and (j) C500 during the PBS test in the dark. Transfer curves of the  $\text{TiO}_2$  TFT for chips (k) C375 and (l) C500 during the PBIS test with the illumination of light with  $\lambda = 600 \text{ nm}$ . Transfer curves of the  $\text{TiO}_2$  TFT for chips (m) C375 and (n) C500 during the PBIS test with illumination of light with  $\lambda = 400 \text{ nm}$ .

respectively, while Figure 5e,f shows the transfer curves of the  $\text{TiO}_2$  TFT after different accumulated bias times up to 1800 s during the NBIS test with illumination of light with  $\lambda = 600 \text{ nm}$  for chip C375 and C500, respectively. Interestingly, when the illumination wavelength  $\lambda = 600 \text{ nm}$ , the transfer curves of TFTs in Figure 5e,f are slightly shifted toward negative values for both the chips in comparison to those in Figure 5g,h with an illuminated wavelength  $\lambda = 400 \text{ nm}$ . This enormous shift of the transfer curve occurs because of a synergistic effect of the electron trapping and detrapping at the channel/dielectric interface with the excitation of oxygen vacancies under gate bias with the illumination wavelength  $\lambda = 400 \text{ nm}$ .<sup>15</sup>

Similarly, Figure 5i,j shows the transfer curves of the  $\text{TiO}_2$  TFT under  $V_{DS} = 1 \text{ V}$  after different accumulated bias times up to 1800 s during positive bias stress in the dark for chips C375 and C500, respectively. Figure 5k,l depicts the transfer curves of the  $\text{TiO}_2$  TFT after different accumulated bias times up to 1800 s during the PBIS test with the illumination of light with  $\lambda = 600 \text{ nm}$  for chips C375 and C500, respectively. Similarly, when the illumination wavelength  $\lambda = 400 \text{ nm}$ , the transfer curves of TFTs in Figure 5m,n for chips C375 and C500, respectively, shifted toward negative values for both the chips in comparison to those in Figure 5k,l with  $\lambda = 600 \text{ nm}$ . Our TFTs show excellent stability with minimum electrical

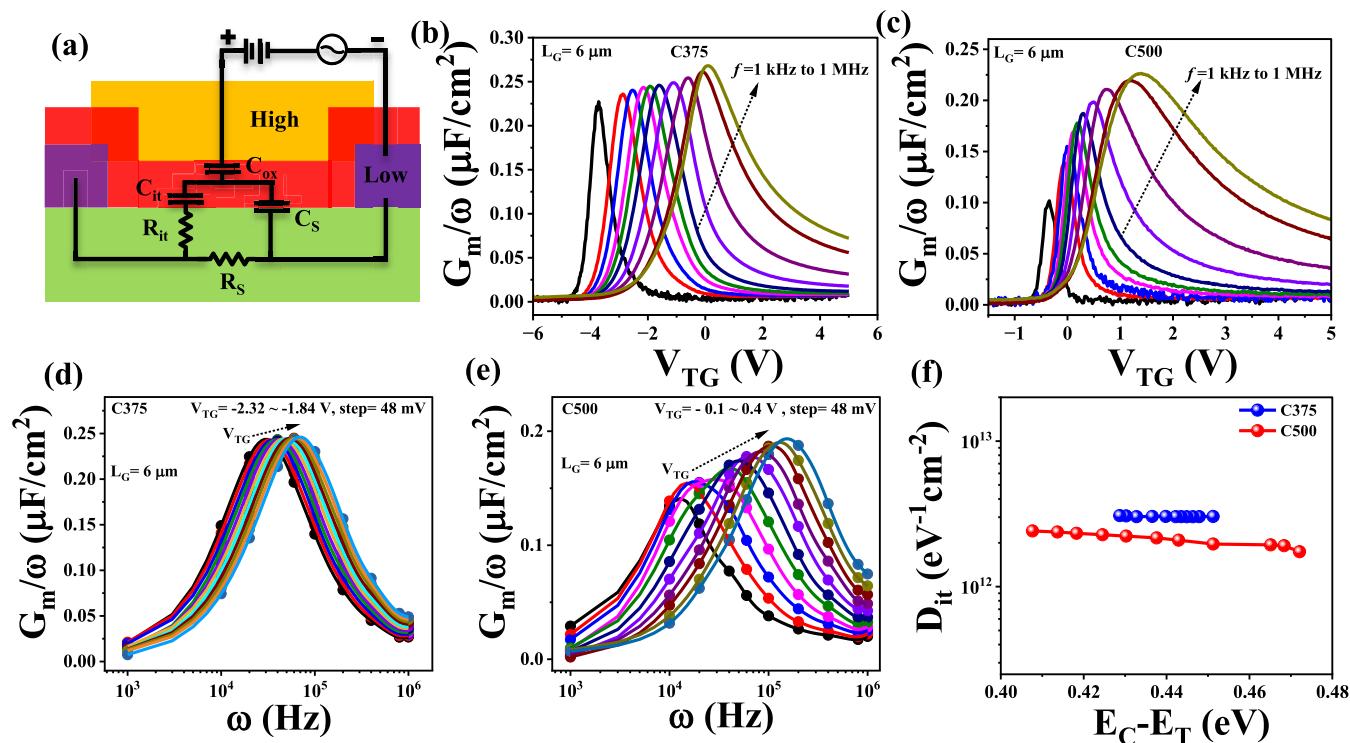

**Figure 6.** (a) Schematic illustration of the  $C/G-V/f$  measurement setup of the  $\text{TiO}_2$  TFT. Measured equivalent parallel conductance ( $G/\omega$ ) as a function of the applied voltage for chips (b) C375 and (c) C500. Conductance ( $G/\omega$ ) as a function of  $\omega$  for interface trap density ( $D_{\text{it}}$ ) extraction for chips (d) C375 and (e) C500 using the AC conductance method. Note that the symbols denote measured data and lines denote fitting results. (f) Comparison of the extracted  $D_{\text{it}}$  as a function of the energy level for the device with the channel length ( $L_{\text{SD}} = 3 \mu\text{m}$ ) for both chips.

performance changes upon both NBS and PBS in the dark as well as with illumination gate stress up to 1800 s, suggesting the feasibility of our  $\text{TiO}_2$  TFTs for practical applications.

We further investigated the interface quality of  $\text{ZrO}_2/\text{TiO}_2$  by systematic capacitance–voltage ( $C-V$ ) and AC conductance–voltage ( $G-V$ ) measurements at different frequencies (1 kHz to 1 MHz) to extract the  $D_{\text{it}}$ . In order to measure the  $C-V$  and  $G-V$  responses of TFTs, the gate terminal was biased high, the source terminal was biased low, and the drain terminal was left open with an AC signal being superimposed, as shown in Figure 6a. The value of dielectric capacitance ( $C_{\text{ox}}$ )  $\sim 1 \mu\text{F}/\text{cm}^2$  was calculated from the accumulation region of the  $C-V$  curves. According to Figure S8a in the Supporting Information,  $C-V$  curves are stretched over the frequency range of 1 kHz to 1 MHz for chip C375 because of the trapping of charge carriers in the interface trap states.<sup>20–22</sup> On the other hand, for chip C500 in Figure S8b, however, the low interface trap density and small frequency dispersion of capacitance indicate a good interface. The interface trap state density  $D_{\text{it}}$  was extracted from the measured equivalent parallel conductance  $G_m$  as a function of the bias voltage and frequency.

Figure 6b,c shows the measured equivalent parallel conductance ( $G_m/\omega$ ) as a function of the applied voltage under different frequencies for chips C375 and C500, respectively. The  $G_m/\omega-V$  curves show that there is a peak at a certain frequency, and as the application frequency increases, the peak intensity increases, and its position shifts toward a higher applied voltage. For the interface states, the conductance represents the loss mechanism resulting from the trapping and detrapping processes of the charge carriers. It is described by the equation below<sup>7,23</sup>

$$\frac{G_m}{\omega} = \frac{e_0 D_{\text{it}}}{2\omega\tau_{\text{it}}} \ln[1 + (\omega\tau_{\text{it}})^2] \quad (3)$$

where  $D_{\text{it}}$  is the interface trap density,  $\tau_{\text{it}}$  is the corresponding trap lifetime constant,  $\omega$  is the angular frequency ( $\omega = 2\pi f$ ), and  $e_0$  is the elementary electron charge. Thus, the value of  $D_{\text{it}}$  and its related time constant  $\tau_{\text{it}}$  can be obtained quantitatively with  $D_{\text{it}} = \frac{2.5}{e_0} \left( \frac{G_m}{\omega} \right)_{\text{peak}}$  and  $\tau_{\text{it}} = \frac{1.98}{\omega_0}$  by fitting the experimental  $G_m/\omega-\omega$  data. Figure 6d,e shows the conductance as a function of the angular frequency under different top gate voltage ( $V_{\text{TG}}$ ) values for chips C375 and C500, respectively. It must be noted that the symbols indicate experimental data, which are well matched with the modeled results that are indicated by lines.

The extracted  $D_{\text{it}}$  with its related time constant  $\tau_{\text{it}}$  can be mapped to the energy level ( $E_C - E_T$ ) according to the Shockley–Read–Hall statistics<sup>24,25</sup>

$$\tau_{\text{it}} = \frac{1}{v_{\text{th}}\sigma_n N_C} \exp\left(\frac{E_C - E_T}{\kappa T}\right) \quad (4)$$

where  $v_{\text{th}}$  is the thermal velocity,  $\sigma_n$  is the electron capture cross section, and  $N_C$  is the effective density of states in the  $\text{TiO}_2$  conduction band. By assuming  $T = 300 \text{ K}$ ,  $v_{\text{th}} = 10^7 \text{ cm/s}$ ,  $\sigma_n = 10^{-14} \text{ cm}^2$ , and  $N_C = 10^{19} \text{ cm}^{-3}$ , the extracted  $D_{\text{it}}$  values are shown comparatively in Figure 6f as a function of the energy level for both chips C375 and C500. It is observed that the  $D_{\text{it}}$  of  $\sim 3 \times 10^{12} \text{ 1/eV cm}^2$  for chip C375 reduced to  $\sim 1.8 \times 10^{12} \text{ 1/eV cm}^2$  with the high annealing temperature for chip C500. The reduced  $D_{\text{it}}$  value can be explained by the fact that surface contamination is substantially reduced with increasing  $\text{O}_2$  annealing temperature (we will discuss this in detail in a

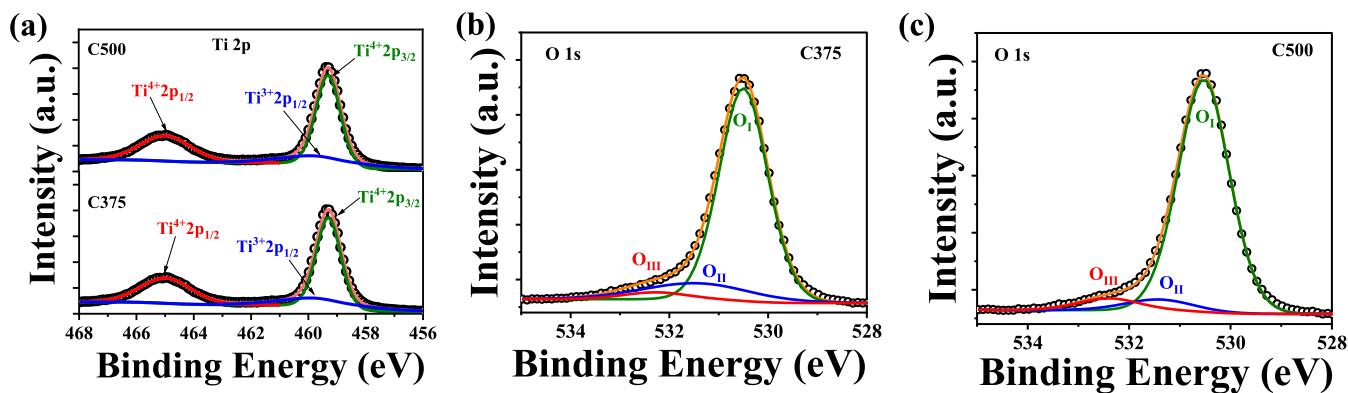

**Figure 7.** Chemical analysis of  $\text{TiO}_2$  films with different annealing temperatures. (a) Ti 2p peak for chips C375 and C500. Deconvoluted XPS spectra of the O 1s peak in lattice oxygen ( $\text{O}_1$ ), carbonate species ( $\text{O}_{\text{II}}$ ), and surface adsorbate ( $-\text{OH}$ )/nonlattice oxygen ( $\text{O}_{\text{III}}$ ) for chips (b) C375 and (c) C500.

later section), which leads to a high-quality channel/dielectric interface with low interface state traps ( $D_{\text{it}}$ ) as result of a steep SS for chip C500.

To understand the effect of the annealing temperature on the chemical composition as well as the surface state of  $\text{TiO}_2$  films, the films were investigated by XPS. A surface-sensitive technique such as XPS can provide information regarding changes in the chemical state of the species that constitute the film.

Figure 7a shows the high-resolution XPS spectra of Ti 2p peak with deconvoluted spectra. The decomposition of Ti 2p leads to  $\text{Ti} 2\text{p}_{3/2}$  and  $\text{Ti} 2\text{p}_{1/2}$  peaks located at 459.2 and 464.9 eV, respectively, with a spin–orbit splitting of 5.7 eV.<sup>26</sup> This corresponds to the typical signature for  $\text{Ti}^{4+}$  in stoichiometric  $\text{TiO}_2$ . However, there is also a shoulder peak at a binding energy of 460.4 eV corresponding to the  $\text{Ti}^{3+}$  in  $\text{Ti}_2\text{O}_3$ .<sup>27,28</sup> This indicates that both  $\text{TiO}_2$  and  $\text{Ti}_2\text{O}_3$  are formed in the film. Figure 7b,c shows the O 1s core-level spectra for chips C375 and C500, respectively. In all cases, the decomposition occurs through three major contributions denoted as  $\text{O}_1$  (530.5 eV),  $\text{O}_{\text{II}}$  (531.4 eV), and  $\text{O}_{\text{III}}$  (532.2 eV for C375 and 532.4 eV for chip C500). The low-energy peak  $\text{O}_1$  with a BE of 530.5 eV is assigned to the lattice oxygen ( $\text{Ti}–\text{O}$ ) bond, while  $\text{O}_{\text{II}}$  and  $\text{O}_{\text{III}}$ , at higher binding energies, correspond to carbonate species ( $-\text{CO}$ ) or the remaining precursor ligands stuck in the film related to surface contamination and nonlattice oxygen related to the  $-\text{OH}$ /surface-adsorbed state, respectively.<sup>27</sup> A quantitative analysis of the O 1s peaks is shown in Table 2.

It has been seen that for the high-annealing-temperature chip C500, the overall surface contamination ( $\text{O}_{\text{II}}$ ) related to carbonaceous compounds/precursor ligands is substantially

reduced by 61% in comparison with the low-annealing chip C375, which leads to a high-quality channel/dielectric interface with low interface state traps ( $D_{\text{it}}$ ), as shown in Figure 6f, whereas the area of the nonlattice oxygen ( $\text{O}_{\text{III}}$ ) increases by 54% for chip C500 with increasing annealing temperature. Therefore, the overall oxygen vacancies ( $V_{\text{o}}$ s) were reduced by 37% for chip C500 with increasing  $\text{O}_2$  annealing temperature. Photoluminescence (PL) spectroscopy was also performed to quantify the defect states of the  $\text{TiO}_2$  film with different annealing temperatures (given in the Figure S9, Supporting Information), which is well corroborated with the XPS results.

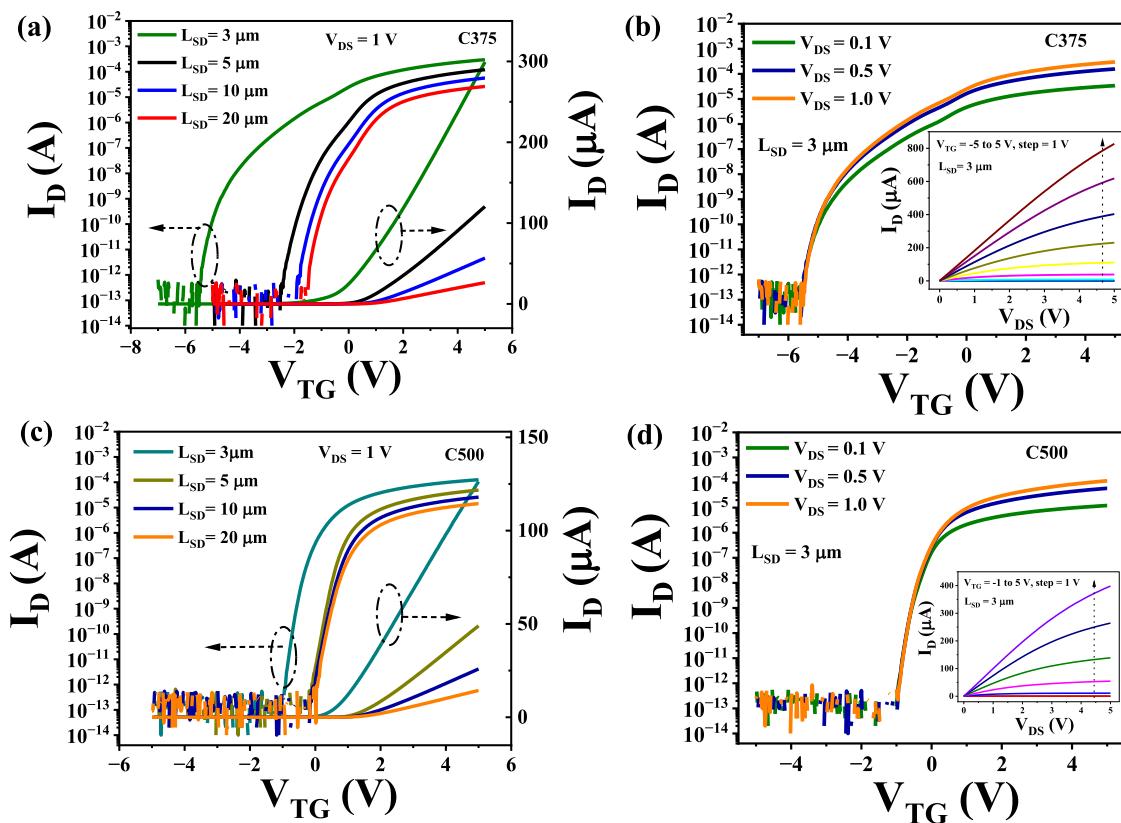

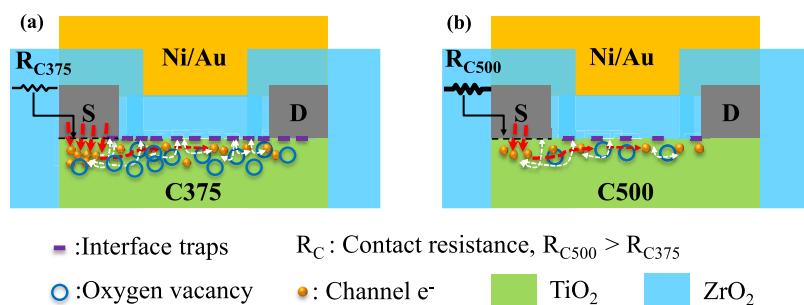

In order to conceptually depict the working mechanism of the device, a schematic representation of electron transport is shown in Figure 8. There are a large number of interface traps and oxygen vacancies in the  $\text{TiO}_2$  channel for the low-annealing-temperature chip C375, as depicted in Figure 8a. However, these interface traps and oxygen vacancies were substantially reduced with an increasing  $\text{O}_2$  annealing temperature for chip C500, as shown in Figure 8b. It is interesting to note that the presence of more donor-like oxygen vacancies in chip C375 may enhance the mobility of carriers with increasing carrier concentration,<sup>29</sup> whereas there is a degradation of the SS value due to the large number of interface states because of surface contamination. On the other hand, for chip C500, a high-quality channel/dielectric interface with low interface state traps ( $D_{\text{it}}$ ) induces steep SS. However, there is an increase in the series electrical resistance (given in the Supporting Information) for chip C500, which degrades the ON state current of devices as compared with the low-annealing chip C375. In conclusion, the conductance of a  $\text{TiO}_2$  thin film can be influenced by both the surface and the bulk, and oxygen vacancies can either be beneficial or disadvantageous depending on whether they are located in the bulk or at the interface.<sup>29,30</sup> Therefore, XPS measurement confirms that a high annealing temperature reduces the surface contamination related to carbonaceous compounds, which is crucial for the formation of a high-quality channel/dielectric interface. However, it needs to be emphasized that surface contamination and oxygen vacancies in the channel can be optimized by tuning the  $\text{O}_2$  annealing temperature for the fabrication of high-performance electronic devices.

### 3. CONCLUSIONS

In summary, high-performance  $\text{TiO}_2$ -based TFTs were demonstrated by using multistack metal contacts along with

**Table 2. Area Percentage of the Deconvoluted O 1s Peak for ALD-Deposited  $\text{TiO}_2$  Films Annealed at Different Temperatures**

| deconvoluted O 1s peak  | chips   |                     |         |                     |

|-------------------------|---------|---------------------|---------|---------------------|

|                         | C375    |                     | C500    |                     |

|                         | BE (eV) | area percentage (%) | BE (eV) | area percentage (%) |

| $\text{O}_1$            | 530.5   | 82.5                | 530.5   | 89                  |

| $\text{O}_{\text{II}}$  | 531.4   | 14                  | 531.4   | 5.6                 |

| $\text{O}_{\text{III}}$ | 532.2   | 3.5                 | 532.4   | 5.4                 |

| $\text{V}_{\text{o}}$ s | 17.5    |                     | 11      |                     |

**Figure 8.** Schematic representation of the electron transport for chips (a) C375 and (b) C500 in a  $\text{TiO}_2$  semiconductor channel in the presence of interface traps and oxygen vacancies.

a high-quality channel/dielectric interface. It is found that the carrier transport and electrical performance of TFTs can be tuned by  $\text{O}_2$  annealing with the control of oxygen vacancies and contamination of the channel. TFTs with a higher  $\text{O}_2$  annealing temperature (C500) exhibit an enhanced electrical performance, including a stepper SS of 88 mV/dec, a higher  $I_{\text{ON}}/I_{\text{OFF}}$  of  $\sim 10^9$ , and a mobility  $\mu_{\text{FE}}$  of  $1.5 \text{ cm}^2/\text{V}\cdot\text{s}$  under a battery-powered voltage of 1 V. In contrast, the transistors in chip C375 exhibit a degradation of SS value to  $\sim 123$  mV/dec due to the large number of interface states. This high performance, along with low gate leakage and low  $I_{\text{OFF}}$  current, are highly promising to be employed in IoT applications with low power consumption requirements, offering a potential solution for applications with cost-effective demands. Furthermore, this study discloses the possible carrier transport mechanism in the stoichiometry with carbonaceous  $\text{TiO}_2$  thin films, providing a better understanding of  $\text{TiO}_2$  material properties, which facilitates the further development of  $\text{TiO}_2$ -based electronic and optoelectronic devices in the future.

## 4. EXPERIMENTAL SECTION

**4.1. Fabrication Process.** The devices were fabricated around a base of 260 nm thermally grown  $\text{SiO}_2$ /Si substrate, where  $\text{SiO}_2$  was employed for isolation purposes. First, a thin  $\text{TiO}_2$  film of 30 nm was deposited on the  $\text{SiO}_2$ /Si substrate by thermal atomic layer deposition (ALD) at 150 °C with tetrakisdimethylamino-titanium (TDMAT) and  $\text{H}_2\text{O}$  as the Ti and O sources, respectively. The sample was split into two chips, followed by rapid thermal annealing (RTA) at 375 and 500 °C for 30 min under an  $\text{O}_2$  atmosphere. The chips were then subjected to the same device fabrication process. The devices using  $\text{TiO}_2$  films annealed at 375 and 500 °C were named C375 and C500 chips, respectively. In the second step, the  $\text{TiO}_2$  layer mesas were created by standard lithography and inductively coupled plasma (ICP) etching in a  $\text{CF}_4/\text{Ar}$  environment to isolate individual devices. After that, Al/Ti/Au (170 nm/10 nm/70 nm) was deposited as source/drain metal contacts followed by RTA annealing under a  $\text{N}_2$  atmosphere at 300 °C. The chips were then brought into a plasma-enhanced chemical vapor deposition (PECVD) chamber to carry out  $\text{N}_2\text{O}$  treatment at 300 °C for 1 min. Next, a 20 nm-thick  $\text{ZrO}_2$  gate dielectric was deposited by  $\text{O}_2$  plasma-enhanced ALD. Finally, the Ni (180 nm)/Au (70 nm) metal stack was evaporated as the gate contact.

**4.2. Characterization Methods.** The crystal structures of the  $\text{TiO}_2$  thin films with different annealing temperatures were characterized by grazing incidence X-ray diffraction (GI-XRD). The physical thicknesses of channel  $\text{TiO}_2$  and dielectric  $\text{ZrO}_2$  were measured by an ellipsometer (J.A. Woolam M-2000VI) using the Cauchy model based on the accompanying Si wafer during deposition. The surface morphology and roughness of  $\text{TiO}_2$  mesas with different  $\text{ZrO}_2$  thicknesses were examined by atomic force microscopy (AFM) in the tapping mode (Dimension-3100 V SPM). In order to understand the physical structure (film thickness) and

interface quality of  $\text{TiO}_2$  TFTs, samples are characterized by cross-sectional transmission electron microscopy (TEM). The focused ion beam (FIB) technique (Tescan S8000X Plasma FIB) was employed for cross-sectional sample preparation for the above investigation. Photoluminescence (PL) spectroscopy with 320 nm pulsed excitation by a Ti:sapphire laser source was used in a time-correlated single photon counting (TCSPC) system to quantify the defect states of the  $\text{TiO}_2$  film with different annealing temperatures. The chemical compositions of the  $\text{TiO}_2$  thin films were analyzed by X-ray photoelectron spectroscopy (XPS) (Thermo Scientific) with an Al  $\text{K}\alpha$  X-ray source at an energy of 1486.6 eV at a base pressure below  $5 \times 10^{-8}$  Torr. The data analysis was performed with Advantage software. All peak positions and relative sensitivity factors were calibrated to the C 1s peak at 284.8 eV, and the error in the binding energies is within 0.1 eV. For accurate detection, 5 nm-thick film surfaces were etched with Ar ions before XPS characterization. Current–voltage ( $I$ – $V$ ) measurements of the two chips were carried out at room temperature using an Agilent B1500A semiconductor parameter analyzer. Capacitance–voltage ( $C$ – $V$ ) measurements were also performed at room temperature using the Agilent B1520A from 1 kHz to 10 MHz.

## ■ ASSOCIATED CONTENT

### SI Supporting Information

The Supporting Information is available free of charge at <https://pubs.acs.org/doi/10.1021/acsaem.4c00524>.

AFM images;  $I_{\text{D}}-V_{\text{DS}}$  curves of the  $\text{TiO}_2$  back gate device with different  $\text{N}_2\text{O}$  treatment times and flow rates;  $I_{\text{D}}-V_{\text{DS}}$  data for the TLM structure; reproducibility of  $\text{TiO}_2$  TFTs; stability (aging effect); environmental stability of  $\text{TiO}_2$  TFTs; measurement setup for NBS and PBS tests; capacitance–voltage ( $C$ – $V$ ) at different frequencies; room temperature PL spectra with deconvoluted peaks of the  $\text{TiO}_2$  film (PDF)

## ■ AUTHOR INFORMATION

### Corresponding Author

**Yuping Zeng** – Department of Electrical & Computer Engineering, University of Delaware, Newark, Delaware 19716, United States;  [orcid.org/0000-0002-6128-8103](https://orcid.org/0000-0002-6128-8103); Email: [yzeng@udel.edu](mailto:yzeng@udel.edu)

### Authors

**Chandan Samanta** – Department of Electrical & Computer Engineering, University of Delaware, Newark, Delaware 19716, United States

**Saravanan Yuvaraja** – Department of Electrical & Computer Engineering, University of Delaware, Newark, Delaware 19716, United States;  [orcid.org/0000-0001-9187-0543](https://orcid.org/0000-0001-9187-0543)

**Tuofu Zhama** – Department of Electrical & Computer Engineering, University of Delaware, Newark, Delaware 19716, United States

**Haochen Zhao** – Department of Electrical & Computer Engineering, University of Delaware, Newark, Delaware 19716, United States

**Lars Gundlach** – Department of Chemistry and Biochemistry, University of Delaware, Newark, Delaware 19716, United States;  [orcid.org/0000-0002-4312-0614](https://orcid.org/0000-0002-4312-0614)

Complete contact information is available at:

<https://pubs.acs.org/10.1021/acsaelm.4c00524>

## Author Contributions

C.S.: conceptualization, data curation, formal analysis, and writing—original draft and methodology; S.Y.: writing—review and editing; T.Z.: data curation and AFM analysis; H.Z.: data analysis (TEM); L.G.: data curation (PL); Y.Z.: supervision, conceptualization, and project administration. All authors have given approval to the final version of the manuscript.

## Notes

The authors declare no competing financial interest.

## ACKNOWLEDGMENTS

The authors acknowledge the University of Delaware Nanofabrication Facility (UDNF). C.S. acknowledges financial support from the University of Delaware for Nanofabrication Facility. Y.Z. acknowledges financial support under NASA Grants (80NSSC22M0039/80NSSC22M0171/80NSSC23M0134) and the NSF career award (2239302). The Authors would also like to acknowledge the funding support from NSF Fuse program with No. 2328840.

## REFERENCES

- (1) Yuvaraja, S.; Khandelwal, V.; Tang, X.; Li, X. Wide bandgap semiconductor-based integrated circuits. *Chip* **2023**, *2*, No. 100072.

- (2) Zhang, Y.; Udrea, F.; Wang, H. Multidimensional device architectures for efficient power electronics. *Nat. Electron.* **2022**, *5*, 723–734.

- (3) Zhong, W.; Li, G.; Lan, L.; Li, B.; Chen, R. Effects of annealing temperature on properties of InSnZnO thin film transistors prepared by Co-sputtering. *RSC Adv.* **2018**, *8*, 34817.

- (4) Samanta, C.; Ghimire, R. R.; Ghosh, B. Fabrication of Amorphous Indium–Gallium–Zinc–Oxide Thin-Film Transistor on Flexible Substrate Using a Polymer Electrolyte as Gate Dielectric. *IEEE Trans. Electron Devices* **2018**, *65*, 2827–2832.

- (5) Zhang, J.; Cui, P.; Lin, G.; Zhang, Y.; Sales, M. G.; Jia, M.; Li, Z.; Goodwin, C.; Beebe, T.; Gundlach, L.; Ni, C.; McDonnell, S.; Zeng, Y. High performance anatase-TiO<sub>2</sub> thin film transistors with a two-step oxidized TiO<sub>2</sub> channel and plasma enhanced atomic layer-deposited ZrO<sub>2</sub> gate dielectric. *Appl. Phys. Express* **2019**, *12*, No. 096502.

- (6) Zhang, J.; Sales, M. G.; Lin, G.; Cui, P.; Pepin, P.; Vohs, J. M.; McDonnell, S.; Zeng, Y. Ultrathin-Body TiO<sub>2</sub> Thin Film Transistors with Record On-Current Density, ON/OFF Current Ratio, and Subthreshold Swing via O<sub>2</sub> Annealing. *IEEE Electron Device Lett.* **2019**, *40*, 1463–1466.

- (7) Zhang, J.; Zhang, Y.; Cui, P.; Lin, G.; Ni, C.; Zeng, Y. One-Volt TiO<sub>2</sub> Thin Film Transistors with Low-Temperature Process. *IEEE Electron Device Lett.* **2021**, *42*, 521–524.

- (8) Katayama, M.; Ikesaka, S.; Kuwano, J.; Yamamoto, Y.; Koinuma, H.; Matsumoto, Y. Field-effect transistor based on atomically flat rutile TiO<sub>2</sub>. *Appl. Phys. Lett.* **2006**, *89*, No. 242103.

- (9) Katayama, M.; Ikesaka, S.; Kuwano, J.; Koinuma, H.; Matsumoto, Y. High quality anatase TiO<sub>2</sub> film: Field-effect transistor based on anatase TiO<sub>2</sub>. *Appl. Phys. Lett.* **2008**, *92*, No. 132107.

- (10) Park, J. W.; Han, S. W.; Jeon, N.; Jang, J.; Yoo, S. Improved Electrical Characteristics of Amorphous Oxide TFTs Based on TiO<sub>x</sub> Channel Layer Grown by Low-Temperature MOCVD. *IEEE Electron Device Lett.* **2008**, *29*, 1319–1321, DOI: [10.1109/LED.2008.2005737](https://doi.org/10.1109/LED.2008.2005737).

- (11) Park, J. W.; Lee, D.; Kwon, H.; Yoo, S. Improvement of On-Off-Current Ratio in TiO<sub>x</sub> Active-Channel TFTs Using N<sub>2</sub>O Plasma Treatment. *IEEE Electron Device Lett.* **2009**, *30*, 362–364, DOI: [10.1109/LED.2009.2013647](https://doi.org/10.1109/LED.2009.2013647).

- (12) Park, J. W.; Lee, D.; Kwon, H.; Yoo, S.; Huh, J. Performance Improvement of N-Type TiO<sub>x</sub> Active-Channel TFTs Grown by Low-Temperature Plasma-Enhanced ALD. *IEEE Electron Device Lett.* **2009**, *30*, 739–741, DOI: [10.1109/LED.2009.2021587](https://doi.org/10.1109/LED.2009.2021587).

- (13) Choi, K. H.; Kim, H. K. Fabrication of Transparent TiO<sub>2-x</sub> Channel-Based Thin Film Transistors using an Oxygen-Deficient TiO<sub>2-x</sub> Target. *Electrochem. Solid-State Lett.* **2011**, *14*, H314.

- (14) Zhong, N.; Cao, J. J.; Shima, H.; Akinaga, H. Effect of Annealing Temperature on TiO<sub>2</sub>-Based Thin-Film-Transistor Performance. *IEEE Electron Device Lett.* **2012**, *33*, 1009–1011.

- (15) Zhang, J.; Jia, M.; Sales, M. G.; Zhao, Y.; Lin, G.; Cui, P.; Santiwipharat, C.; Ni, C.; McDonnell, S.; Zeng, Y. Impact of ZrO<sub>2</sub> Dielectrics Thickness on Electrical Performance of TiO<sub>2</sub> Thin Film Transistors with Sub-2 V Operation. *ACS Appl. Electron. Mater.* **2021**, *3*, 5483–5495.

- (16) Abliz, A.; Nurmat, P.; Wan, D. Rational design of oxide heterostructure InGaZnO/TiO<sub>2</sub> for high-performance thin-film transistors. *Appl. Surf. Sci.* **2023**, *609*, No. 155257.

- (17) Ho, S. H.; Chang, T. C.; Lu, Y. H.; Chen, C. E.; Tsai, J. Y.; Liu, K. J.; Tseng, T. Y.; Cheng, O.; Huang, C. T.; Lu, C. S. Investigation of abnormal negative threshold voltage shift under positive bias stress in input/output n-channel metal-oxide-semiconductor field-effect transistors with TiN/HfO<sub>2</sub> structure using fast I-V measurement. *Appl. Phys. Lett.* **2014**, *104*, No. 113503.

- (18) Shih, W. S.; Young, S. J.; Ji, L. W.; Water, W.; Shiu, H. W. TiO<sub>2</sub>-Based Thin Film Transistors with Amorphous and Anatase Channel Layer. *J. Electrochem. Soc.* **2011**, *158*, H609.

- (19) Zhang, J.; Lin, G.; Cui, P.; Jia, M.; Li, Z.; Gundlach, L.; Zeng, Y. Enhancement-/Depletion-Mode TiO<sub>2</sub> Thin-Film Transistors via O<sub>2</sub>/N<sub>2</sub> Preannealing. *IEEE Trans. Electron Devices* **2020**, *67*, 2346–2351.

- (20) Cui, P.; Zhang, J.; Jia, M.; Lin, G.; Wei, L.; Zhao, H.; Gundlach, L.; Zeng, Y. InAlN/GaN metal–insulator–semiconductor high-electron-mobility transistor with plasma enhanced atomic layer-deposited ZrO<sub>2</sub> as gate dielectric. *Jpn. J. Appl. Phys.* **2020**, *59*, No. 020901.

- (21) Lee, S.; Park, S.; Kim, S.; Jeon, Y.; Jeon, K.; Park, J. H.; Park, J.; Song, I.; Kim, C. J.; Park, Y.; Kim, D. M.; Kim, D. H. Extraction of subgap density of states in amorphous InGaZnO thin-film transistors by using multifrequency Capacitance–Voltage characteristics. *IEEE Electron Device Lett.* **2010**, *31*, 231–233.

- (22) Shaw, A.; Jin, J. D.; Mitrovic, I. Z.; Hall, S.; Wrench, J. S.; Chalker, P. R. Extraction of the sub-band gap density of states of nb doped ZnO thin film transistors using C-V measurements. *Microelectron. Eng.* **2017**, *178*, 213–216.

- (23) Liu, S.; Yang, S.; Tang, Z.; Jiang, Q.; Liu, C.; Wang, M.; Shen, B.; Chen, K. J. Interface/border trap characterization of Al<sub>2</sub>O<sub>3</sub>/AlN/GaN metal-oxide-semiconductor structures with an AlN interfacial layer. *Appl. Phys. Lett.* **2015**, *106*, No. 051605.

- (24) Takei, K.; Kapadia, R.; Fang, H.; Plis, E.; Krishna, S.; Javey, A. High quality interfaces of InAs-on-insulator field-effect transistors with ZrO<sub>2</sub> gate dielectrics. *Appl. Phys. Lett.* **2013**, *102*, No. 153513.

- (25) Chen, H. C.; Kuo, C. W.; Chang, T. C.; Lai, W. C.; Chen, P. H.; Chen, G. F.; Huang, S. P.; Chen, J. J.; Zhou, K. J.; Shih, C. C.; Tsao, Y. C.; Huang, H. C.; Sze, S. M. Investigation of the Capacitance–Voltage Electrical Characteristics of Thin-Film Transistors Caused by Hydrogen Diffusion under Negative Bias Stress in a Moist Environment. *ACS Appl. Mater. Interfaces* **2019**, *11*, 40196–40203.

(26) Bharti, B.; Kumar, S.; Lee, H. N.; Kumar, R. Formation of oxygen vacancies and  $Ti^{3+}$  state in  $TiO_2$  thin film and enhanced optical properties by air plasma treatment. *Sci. Rep.* **2016**, *6*, No. 32355.

(27) Dufond, M. E.; Diouf, M. W.; Badie, C.; Laffon, C.; Parent, P.; Ferry, D.; Grosso, D.; Kools, J. C. S.; Elliott, S. D.; Santinacci, L. Quantifying the Extent of Ligand Incorporation and the Effect on Properties of  $TiO_2$  Thin Films Grown by Atomic Layer Deposition Using an Alkoxide or an Alkylamide. *Chem. Mater.* **2020**, *32*, 1393–1407.

(28) Donnell, S.; Jose, F.; Shiel, K.; Snelgrove, M.; McFeely, C.; McGill, E.; O'Connor, R. Thermal and plasma enhanced atomic layer deposition of ultrathin  $TiO_2$  on silicon from amide and alkoxide precursors: growth chemistry and photoelectrochemical performance. *J. Phys. D: Appl. Phys.* **2022**, *55*, No. 085105, DOI: 10.1088/1361-6463/ac360c.

(29) Zhang, J.; Liu, N.; Zhang, W.; Ye, J. Exploring the influence of oxygen vacancy on the transport behaviour of  $Ba_{1-x}La_xSnO_3$  epitaxial films at different doping regimes. *J. Appl. Phys.* **2023**, *134*, No. 055701, DOI: 10.1063/5.0157281.

(30) Klasen, A.; Baumli, P.; Sheng, Q.; Johannes, E.; Bretschneider, S. A.; Hermes, I. M.; Bergmann, V. W.; Gort, C.; Axt, A.; Weber, S. A. L.; Kim, H.; Butt, H. J.; Tremel, W.; Berger, R. Removal of Surface Oxygen Vacancies Increases Conductance Through  $TiO_2$  Thin Films for Perovskite Solar Cells. *J. Phys. Chem. C* **2019**, *123*, 13458–13466.

CAS BIOFINDER DISCOVERY PLATFORM™

## PRECISION DATA FOR FASTER DRUG DISCOVERY

CAS BioFinder helps you identify targets, biomarkers, and pathways

Unlock insights

**CAS**

A division of the

American Chemical Society