Received 21 February 2025; accepted 20 March 2025. Date of publication 31 March 2025; date of current version 10 April 2025.

The review of this article was arranged by Editor S. Menzel.

Digital Object Identifier 10.1109/JEDS.2025.3556316

# Performance and Scalability of Strain Engineered 2D MoTe<sub>2</sub> Phase-Change Memristors

MARIA VITORIA GUIMARAES LEAL<sup>1</sup>, AHMAD AZIZIMANESH<sup>1</sup>,

NAZMUL HASAN<sup>1</sup>, AND STEPHEN M. WU<sup>1,2</sup>

1 Department of Electrical and Computer Engineering, University of Rochester, Rochester, NY 14627, USA

2 Department of Physics and Astronomy, University of Rochester, Rochester, NY 14627, USA

CORRESPONDING AUTHOR: M. V. G. LEAL and S. M. WU (e-mail: mguimar2@ur.rochester.edu; stephen.wu@rochester.edu)

This work was supported by the National Science Foundation (NSF) under Grant OMA-1936250 and Grant ECCS-1942815.

**ABSTRACT** This work presents a performance optimization and scalability study of a two-dimensional vertical molybdenum ditelluride (MoTe<sub>2</sub>) phase-change memristor. The device switches between the semimetallic (1T') and semiconducting (2H) states under an electric field. Process-induced strain engineering techniques at the contacts reduces the switching energy barrier, biasing the active region closer to the phase switching point. This work focuses on optimizing this technique to achieve the best yield and device performance, with a low switching voltage ( $\leq 0.5V$ ) and high on/off ratio  $\geq 10^5$ . Small length and area of the contact between the metal stressor and the 2D 1T'-MoTe<sub>2</sub> flake are critical for high yield and performance, potentially due to lowered chances of encountering defects introduced during the fabrication process ( $L \leq 0.6\mu\text{m}$  and  $A \leq 0.3\mu\text{m}^2$ ). Smaller flake contact perimeters  $\leq 1.2\mu\text{m}$  also reduce defect incidence, and increases on/off ratios. The switching voltage is influenced by the contact-flake geometry, exhibiting a lower value for 2D flake geometries with contact angles  $\leq 65^\circ$  likely due to geometric variation in strain distribution effects from process-induced strain engineering. These results demonstrate that by accounting for device geometry, our process may achieve yield approaching 90% with consistent low switching voltage and high on/off ratio. Yield and performance properties become better when scaled down in size due to our phase-change mechanism, which is the opposite behavior to most conductive filament based memristors.

**INDEX TERMS** Memristor, two-dimensional materials, strain engineering, phase-change memory, device fabrication.

## I. INTRODUCTION

The memristor is a two terminal device that can be switched between a high resistance and low resistance state under applied voltage bias, causing a characteristic hysteresis loop [1], [2]. This hysteretic resistive behavior makes memristors promising for next-generation memory and neuromorphic computing applications [3], [4], [5]. Two-dimensional (2D) materials can be used to fabricate these devices, attracting great attention due to their lower-power operation, compatibility with flexible substrates, and potential integration through 3D monolithic integration, while also offering benefits such as reduced latency, reduced switching voltage, and reduced footprint [6], [7]. Despite the benefits, both regular and 2D memristors typically rely on

filamentary conduction from the motion of defects, grain boundaries or metal ions to operate. This results in highly variable behaviors, limited scalability, and fewer engineerable or designable parameters, making them unsuitable for translation from laboratory-based demonstration to industrial applications [8].

Recent advances from our group and others include the development of high-performance vertical molybdenum ditelluride (MoTe<sub>2</sub>) phase-change memristors [9], [10], which operates on a fundamentally different mechanism. A forward bias voltage drives an electric-field-induced phase transition in 2D MoTe<sub>2</sub>, switching between semimetallic (1T') and semiconducting (2H) states to represent the two resistive states. This phase-change mechanism has the

potential to offer more stable and controllable switching compared to traditional filamentary memristors due to it relying less on random processes [9], [10], [11], [12], [13].

While the strain-phase change mechanism has been proven effective, uncontrolled parameters such as the shape of the exfoliated flakes or defects inserted during fabrication present significant challenges in reproducibility and performance reliability. The distinct geometries of each exfoliated 2D flake increases the complexity when dealing with device performance, since it affects how the strain is distributed. In contrast to our group's original work [10], which primarily focused on validating the strain-induced phase change mechanism in 2D MoTe<sub>2</sub>, here we explore remaining open questions related to device scalability and performance consistency. Parameters such as flake contact area and flake geometry were not considered previously, and thus high performance devices were not reliably achieved. In this work, to obtain predictable memristor behavior, we now focus on understanding which parameters are crucial to achieving consistent high performance. Thus, here we present an optimized fabrication process to obtain consistently high performance in 2D phase-change memristors with high yield, reliable low switching voltage and high on/off ratio.

It is shown in this work that devices achieve their best performance as they are scaled down in size, a beneficial feature to any potential future applications. This is counter to most memristors, which rely on defects to form conductive pathways that facilitate the switching between resistance states leading to poorer performance as devices are scaled down. Since our device operates through a phase-change mechanism, we are not limited by the same issues and in this work it is shown that through defect-free fabrication and control of strain distribution, we may address scalability and device variability challenges present in current 2D memristor technology.

## II. STRAIN-BASED MoTe<sub>2</sub> MEMRISTOR

Process-induced strain engineering techniques have been used in commercial complementary metal-oxide-semiconductor (CMOS) nanofabrication processes since the 90-nm technology node [14]. Uniaxial tensile or compressive strain is used to selectively enhance the mobility of electrons or holes for n-type or p-type metal-oxide-semiconductor field effect transistors. This process was originally done through the deposition of highly stressed thin films that relax, introducing strain in the transistor channels [15]. This approach can also be applied to 2D materials on a device-to-device basis, with control of the magnitude and direction of the strain [16]. To achieve that control, parameters like film force and geometry of the film stressor are important since these factors control strain magnitude and strain distribution. The film force, film stress  $\times$  film thickness, can be used to quantify the strain magnitude applied by the film to the 2D flake [17]. The Stoney equation [18] enables the calculation of the average film stress ( $\sigma$ ). The applied film force ( $F_f$ ) is related to the film stress and the film thickness ( $t_f$ ) by  $F_f = t_f \times \sigma$  [19], [20].

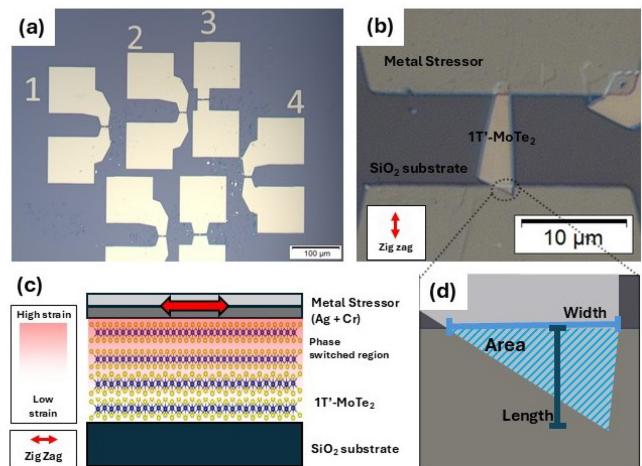

**FIGURE 1.** Optical micrograph of a) multiple devices and b) a single device. c) Schematic of strain transfer from the metal stressor to the 2D material and d) parameters measured to obtain flake contact length, width, and area.

In our memristor design, a stressed metallic thin film applies uniaxial tensile strain to 1T'-MoTe<sub>2</sub> (Fig. 1a,b). The strain is transferred from the metal contact to the 2D material, from the top layers down, through van der Waals interactions [16], [17], [21]. The strain transfer length scale is finite in the out-of-plane direction of MoTe<sub>2</sub>, restricting the phase transition to the uppermost layers, while the layers past  $\sim 7$  nm remain unstrained [10]. A phase-transition from semimetallic (1T') to semiconducting (2H) states is induced by the uniaxial strain, happening underneath the contacts. This both naturally creates a self-aligned vertical transport structure (Fig. 1c), and utilizes the strain to put the material closer to the phase transition point, where small perturbations from an electric field can induce the phase-transition. The electric field is applied out-of-plane from a two-terminal voltage that ranges from  $-1.2$  to  $1.2$  V. The device operates in a high resistance state (HRS) when in the semiconducting 2H phase and a low resistance state (LRS) when it is in the semimetallic 1T' phase, with switching triggered by specific voltage thresholds. It has been shown in our previous work that increasing tensile strain applied along the zigzag direction, alters the material's phase stability, lowers the barrier to phase transition, and enhances device performance. The application of tensile strain along the zigzag direction often also results in compressive strain along the armchair direction, from the positive Poisson ratio of the flake, affecting the phase transition behavior and the strain distribution [22]. Therefore, the strain-induced phase transition mechanism is highly sensitive to the crystallographic orientation of the MoTe<sub>2</sub> flakes and the distribution of the strain applied from the stressed metal contact [10].

Considering the sensitivity of the phase-change to individual process-parameters at the edge of the 2D flake, variations in the geometry of the flakes, the area and the length

of contact, and the quality of the flake edge perimeters are important in determining the full potential of these MoTe<sub>2</sub> memristors. Here, we provide a detailed study of these process parameters that play a large role in achieving consistent high-performance in this class of device, including contact area, contact length, contact angle, and flake edge-perimeter.

### III. DEVICE FABRICATION AND CHARACTERIZATION

1T'-MoTe<sub>2</sub> multilayer flakes were tape exfoliated from the bulk crystal along its identified zigzag direction. The 2D memristors were fabricated on SiO<sub>2</sub> substrates, demonstrating the potential for CMOS compatibility [23] since previously demonstrated results were performed on MgO substrates [10]. The substrates were cleaned in oxygen plasma at 100 W and 200 mTorr for 4 minutes, to ensure surface purity. The plasma cleaner chamber was previously cleaned, under the same conditions, for 20 minutes before placing the substrates. Post-cleaning ( $\leq 1$  min), 1T'-MoTe<sub>2</sub> was exfoliated onto SiO<sub>2</sub> and baked at 100°C for 90 seconds to improve flake adhesion. The tape was slowly removed, and the chip was placed into acetone and taken to an ultrasonic bath for 20 minutes, to delaminate poorly adhered flakes [24]. Direct-write laser photolithography was used to pattern the memristors on the 1T'-MoTe<sub>2</sub> flakes. The metal contact geometries, flake thickness range (7 to 25 nm) and flake angle (aligned along crystal zigzag direction) were the same for all devices, varying only the length of the metal contact on the flake as shown in Fig. 1d. For the metal contacts, 25 nm of silver (Ag) and 25 nm of chromium (Cr) were deposited, using e-beam evaporation at a rate of 1 Ås<sup>-1</sup>, under a chamber pressure below  $5 \times 10^{-6}$  torr. To quantify the strain applied by the deposited film, the film force was measured by placing a clean microscope coverslip with the sample into the e-beam evaporator for the metal contact deposition step. Before and after the deposition, the radius of curvature of the coverslip was measured using contact profilometry and the film force was calculated based on the Stoney equation mentioned previously. Since the transferred film stress primarily depends on the film force (film stress  $\times$  film thickness), rather than deposition area, the film force exerted at the 2D material under the metal contact is consistent with the large-area calibration coverslip [17].

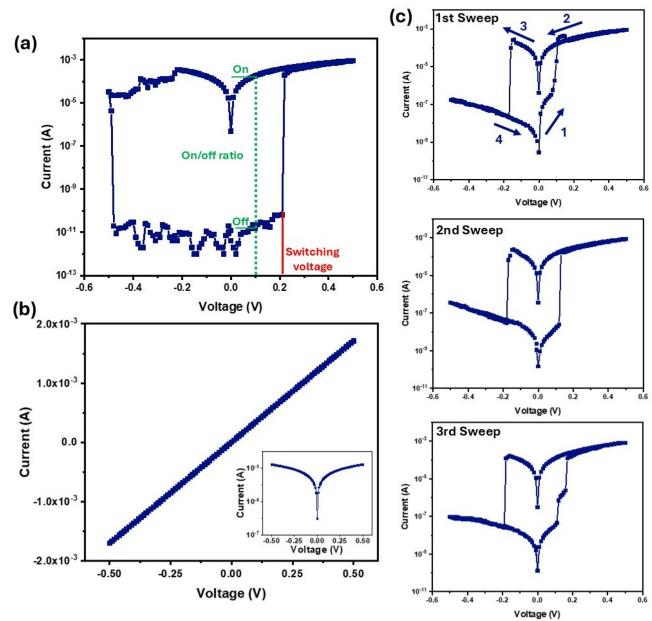

The *I*-*V* characteristics were obtained through a Keysight 2901A Precision Source/Measure Unit (SMU) (Fig. 2). A wire bonder was used to connect the metal contacts to a resistivity puck placed into a sample wiring test station, allowing the devices to be analyzed in the SMU. The voltage at which the device turned on was called switching voltage and the on/off ratio was determined by the ratio between the current in the on and off state at 100 mV (Fig. 2a). The endurance test was performed using 300 full *I*-*V* sweeps of the device, ranging from -0.5 to 0.5V. The current compliance was 100 μA. The current at -100mV was extracted in every cycle, where only curves with successful switching were included. Devices that exhibited resistive

**FIGURE 2.** a) *I*-*V* characteristic of the strain-engineered memristor with labels indicating on/off ratio and switching voltage (switched device) b) *I*-*V* characteristic of a device that did not switch (linear device). Inset: Same plot in log scale. This device has a  $0.742 \mu\text{m}^2$  area, increasing the likelihood of occurring encountering defects that impede the switching behavior. c) *I*-*V* characteristic of a device over a cycle of three sweeps.

switching behavior were classified as ‘switched devices’ (Fig. 2a) and the ones that did not show switching behavior, without the hysteresis loop typically seen in memristors, were classified as ‘linear devices’ (Fig. 2b). Figure 2c shows the device behavior over a cycle of three sweeps.

Initial fabrication process parameters were chosen based on empirically demonstrated ‘best conditions’ for device performance as reported by Hou et al. [10]. These parameters are as follows: film force of 25 N/m from the contacts, with contact/flake overlap designed perpendicular to the zigzag axis to apply tensile strain aligned along the zigzag direction and the contact/flake overlap length being  $\leq 1.1 \mu\text{m}$  (Fig. 1d). This serves as the starting point for our exploration into varying process parameters to increase device yield and reproducibility.

### IV. SCALING EFFECTS ON MEMRISTOR PERFORMANCE

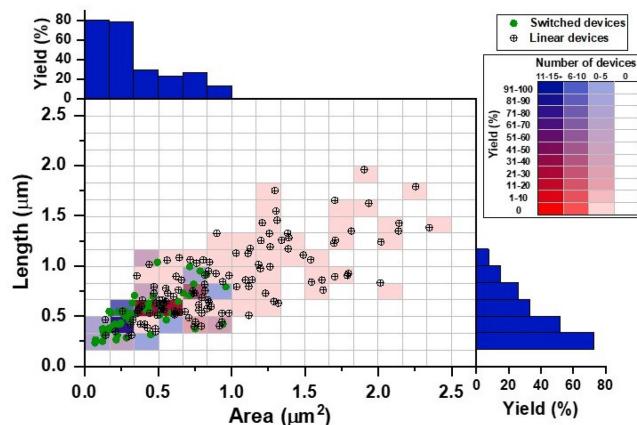

Device scaling was tested by varying the contact length between the metal stressor and the flakes during the fabrication process. The corresponding contact areas and other geometric parameters were measured using optical microscopy images and the software ImageJ. These measurements were confirmed by scanning electron microscopy (SEM). As shown in Figure 3, device yield increases for both shorter contact length, as well as smaller contact area (purple to blue), and decreases for larger contact length and larger contact area (purple to red). This is the opposite behavior of typical filamentary memristors, which rely on defects or grain boundaries to seed switching. In contrast,

**FIGURE 3.** Yield in terms of area, length, and number of devices. Where darker colors indicate a higher number of devices, and the yield is indicated by the red (0%) to blue (100%) color range.

defects in our device impede switching, and smaller contact areas lead to reduced probability of encountering defects that may short out the device. A Poisson defect model estimated density of device shorting defects, introduced during the fabrication process, as approximately 2 per square micrometer (defects/ $\mu\text{m}^2$ ) [25], [26]. For comparison, recent work has shown under Au metal evaporation at  $5 \times 10^{-6}$  torr, an average defect density of  $17.47 \mu\text{m}^{-1}$  [27], measured in cross-sectional transmission electron microscopy (TEM) images. However, these quantified defects vary in size or clustering, such that not all defects reach the threshold to impede switching. Larger defects and clustered regions increase the probability of critical failures, reducing the yield [28], [29]. Plug formation during metal deposition can introduce such defects, due to atom or cluster bombardment and localized heating [30].

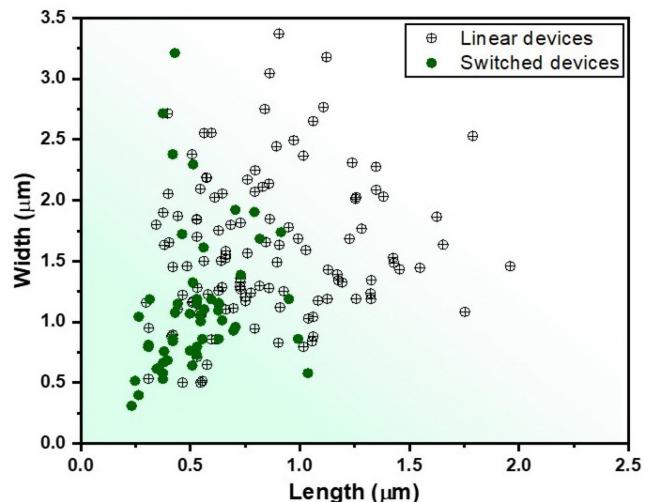

In our experiment, shorter length is also seen to enhance device yield. This may be due to more efficient phase switching because the induced strain is more uniformly localized near the edge, as demonstrated in previous works [10]. Although length and area are intrinsic correlated, their effect on the device performance varies. Figure 4 presents the length vs width distribution of all devices (linear and switched). A significant portion of the switched devices is concentrated in the bottom-left region, where both length and width are smaller. There are several devices with length  $\leq 0.6 \mu\text{m}$ , however, the majority of successfully switched devices exhibits both a length  $\leq 0.6 \mu\text{m}$  and a width  $\leq 1.25 \mu\text{m}$ . Regardless of the shape, with a smaller length and width, the device area will consequently decrease, reinforcing that the contact area is the dominant factor influencing the performance. A small area increases yield, even with variations in length, whereas maintaining a small length alone does not. Thus, smaller contact lengths ensure the device is experiencing adequate strain uniformity for phase switching, but its a small area that minimize defects and increases the yield. These results confirm that our memristor

**FIGURE 4.** Length vs width for all devices, linear and switched.

is improved as it scales down in size, unlike most other memristor implementations where defects are needed to create the conductive bridge.

## V. OPTIMIZATION OF MEMRISTOR PERFORMANCE

To understand the factors that play a role in engineering for deterministic performance and yield in phase-change memristors, we now explore the contact/flake geometry dependence on device performance. While previous work has demonstrated film force, strain directionality, and contact length dependency on device switching characteristics, there are still many contact geometry dependent variables in engineering repeatable device behavior, particularly a high on/off ratio and low switching voltage. When exfoliated, the 2D materials form flakes with a high variability of shapes, even if exfoliated from the same bulk crystal. This remaining variability induced by the flake geometric shape and possible imperfections of the 2D material could lead to the memristors lack of performance reliability. To address this, we conducted additional analysis of other parameters that could influence the device performance. Regarding this analysis, a switching voltage  $\leq 0.5$  V was considered low and an on/off ratio  $\geq 10^5$  was considered high.

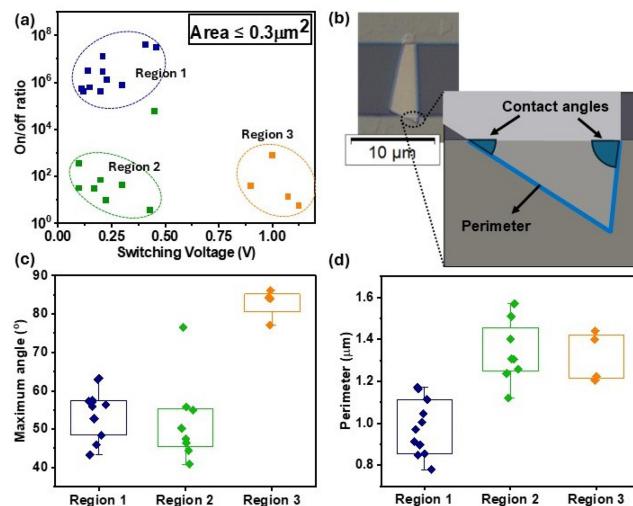

From Fig. 3 it is possible to identify that most switched devices were within the 0 to  $0.3 \mu\text{m}^2$  area range. This observation helps eliminate one confounding variable, allowing the analysis to focus on other factors that affect device performance. By selecting this range and plotting the switching voltage vs on/off ratio graphic (Fig. 5a), the devices end up in three different regions. Region 1 (blue) represents the best condition, where the devices have a high on/off ratio and a low switching voltage. Region 2 (green) has a low switching voltage, but a low on/off ratio and Region 3 (orange) with a high switching voltage and a low on/off ratio. To find potential causes of each behavior, measurements of flake edge perimeter and contact angle were done (Fig. 5b).

**FIGURE 5.** a) Switching voltage vs on/off ratio for the devices with an area  $\leq 0.3 \mu\text{m}^2$ , categorized into regions based on performance. b) Parameters measured to obtain the flake edge perimeter and contact angles. c) Maximum contact angle for the regions described in a) and d) flake edge perimeter for the regions described in a).

Other parameters, like contact flake width, total flake area, length, and width, did not show a strong correlation.

The results of the flake edge perimeter and contact angle are shown in Fig. 5c and d, showing region 1 having low perimeter and region 3 having larger contact angle. This suggests larger contact angles lead to high switching voltages, and larger perimeters lead to lower on/off ratio. The maximum angle between the metal stressor and flake is related to the geometry of the flake portion in contact with the metal stressor. This geometry likely influences the strain distribution [10], [16], [17], [31], which affects the voltage needed to switch the devices between the on and off states. Variations in strain distribution could influence the uniformity of phase-change, consequently affecting the electrical properties obtained, such as the voltage required for phase transitions. Our group has shown how the controlled application of strain via patterned stressors can affect the strain distribution onto the 2D flake [16]. Similarly, here we have observed that the geometry of the 2D flake could also be responsible for strain distribution variations according to the maximum angle formed between the metal contact and the edge of the flake. This suggests that a subset of flake geometries benefit the device performance, likely due to their uniform strain distribution.

On the other hand, the on/off ratio is affected by the flake edge perimeter in contact with the metal stressor. Edge defects could influence the change in resistance between the on and off states. General findings from defect studies in a similar material (2H-MoTe<sub>2</sub>) reported improvement in device performance, such as electrical conductivity and stability, by reducing defect density of the material [32], focusing primarily on bulk materials properties. It is plausible to assume that defects located at the edge may interact

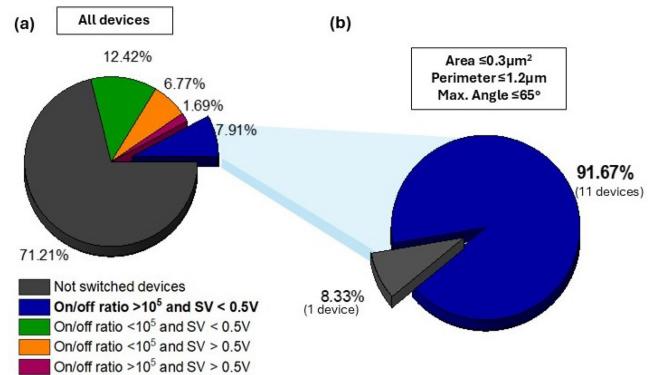

**FIGURE 6.** a) All devices fabricated and b) devices with optimized fabrication parameters distributed according to electrical characteristics, switching voltage (SV) and on/off ratio.

with the metal contact, creating a nonuniform switching. Consequently, smaller perimeters decrease the chance of encountering edge defects, leading to higher on/off ratios.

## VI. PARAMETERS DEPENDENCE

When analyzing all the fabricated devices (177), there is approximately a 30% chance of having a switched device. Within that 30% we have different device behaviors, with a probability of 7.91% of fabricating the ideal case, with a high on/off ratio and a low switching voltage (Fig. 6a).

Considering only the devices with an area  $\leq 0.3 \mu\text{m}^2$ , perimeter  $\leq 1.2 \mu\text{m}$  and a maximum angle  $\leq 65^\circ$ , approximately 91.67% of them exhibited a low switching voltage and high on/off ratio, the ideal operation of a memristor. These parameters represent the optimal design conditions that contribute to achieving the best performance. Thus, among the fabricated devices that met these geometric criteria, the yield within the best case scenario increases from 7.91%, considering all fabricated devices, to 91.67%, when applying the discussed parameters (Fig. 6b). In addition to achieving a high on/off ratio and low switching voltage, the ideal switching devices also exhibit high endurance properties ( $>300$  switching cycles), similar to our previously published results [10]. Variations in the film force and in fabrication from chip-to-chip did not affect the overall device behavior, as we found no significant differences between each measured chip.

## VII. CONCLUSION

We have shown that optimizing the 2D flake-contact area, flake edge perimeter, and the maximum contact angle, significantly enhances the memristor performance, achieving 91.67% yield and a reliable low switching voltage ( $\leq 0.5$  V) and high on/off ratio ( $\geq 10^5$ ). The area and the length play distinct roles in the device performance: smaller areas increase the yield by reducing the likelihood of encountering defects that could impede the phase transition, and shorter lengths ensure more uniform strain profile, preventing non-switched regions from shorting the devices. Most switched

devices had an area  $\leq 0.3\mu\text{m}^2$ , among these devices, those with a flake edge perimeter  $\leq 1.2\mu\text{m}$  exhibited a higher on/off ratio ( $\geq 10^5$ ), likely due to the reduced number of flake-edge defects allowing for a larger change in resistance between LRS and HRS. Additionally, a maximum flake-contact angle of 65° likely represents an optimal flake geometry, where the strain distribution is more uniform, affecting the phase transition occurrence and decreasing the voltage needed to switch between phases. This work identifies parameters that collectively enhance device performance, building on the findings of our previous study, where device behavior was less controlled. Compared to existing memristor technology, that have limited reproducibility and scalability, our optimized fabrication process parameters are not restricted by the same issues. Using our strain-engineered phase-change mechanism, we show a 2D MoTe<sub>2</sub> memristor with consistent low switching voltage and high on/off ratio, high yield, and favorable scalability behavior, significantly improving device performance when geometric factors are accounted for. While this study demonstrates an enhanced fabrication approach, scaling to an industrial level will require the growth of a single-crystalline, wafer-scale, high-quality 1T'-MoTe<sub>2</sub> thin films on silicon, which may support consistent patterning in the optimized flake geometry.

## REFERENCES

- [1] L. Chua, "Memristor-the missing circuit element," *IEEE Trans. Circuit Theory*, vol. 18, no. 5, pp. 507–519, Sep. 1971. [Online]. Available: <http://ieeexplore.ieee.org/document/1083337/>

- [2] D. B. Strukov, G. S. Snider, D. R. Stewart, and R. S. Williams, "The missing memristor found," vol. 453, no. 7191, pp. 80–83, 2008. [Online]. Available: <https://www.nature.com/articles/nature06932>

- [3] J. Shen et al., "Low consumption two-terminal artificial synapse based on transfer-free single-crystal MoS<sub>2</sub> memristor," *Nanotechnology*, vol. 31, no. 26, 2020, Art. no. 265202. [Online]. Available: <https://iopscience.iop.org/article/10.1088/1361-6528/ab82d6>

- [4] Y. Li, Z. Wang, R. Midya, Q. Xia, and J. J. Yang, "Review of memristor devices in neuromorphic computing: Materials sciences and device challenges," *J. Phys. D, Appl. Phys.*, vol. 51, no. 50, 2018, Art. no. 503002. [Online]. Available: <https://iopscience.iop.org/article/10.1088/1361-6463/aae3f>

- [5] R. A. Wells and A. W. Robertson, "Molybdenum disulfide memristors for next generation memory and neuromorphic computing: Progress and prospects," *Adv. Electron. Mater.*, vol. 10, no. 10, 2024, Art. no. 2400121. [Online]. Available: <https://onlinelibrary.wiley.com/doi/10.1002/aem.202400121>

- [6] H. Duan et al., "Low-power memristor based on two-dimensional materials," *J. Phys. Chem. Lett.*, vol. 13, no. 31, pp. 7130–7138, 2022, [Online]. Available: <https://pubs.acs.org/doi/10.1021/acs.jpclett.2c01962>

- [7] J.-H. Kang et al., "Monolithic 3D integration of 2D materials-based electronics towards ultimate edge computing solutions," *Nat. Mater.*, vol. 22, no. 12, pp. 1470–1477, 2023, [Online]. Available: <https://www.nature.com/articles/s41563-023-01704-z>

- [8] M. Lanza, G. Molas, and I. Naveh, "The gap between academia and industry in resistive switching research," *Nat. Electron.*, vol. 6, no. 4, pp. 260–263, Apr. 2023, [Online]. Available: <https://www.nature.com/articles/s41928-023-00954-8>

- [9] F. Zhang et al., "Electric-field induced structural transition in vertical MoTe<sub>2</sub>- and Mo<sub>1-x</sub>W<sub>x</sub>Te<sub>2</sub>-based resistive memories," *Nat Mater.*, vol. 18, no. 1, pp. 55–61, 2019, [Online]. Available: <https://www.nature.com/articles/s41563-018-0234-y>

- [10] W. Hou et al., "Strain engineering of vertical molybdenum ditelluride phase-change memristors," *Nat. Electron.*, vol. 7, no. 1, pp. 8–16, 2024, [Online]. Available: <https://www.nature.com/articles/s41928-023-01071-2>

- [11] S. S. Awate et al., "Strain-induced 2h to 1t' phase transition in suspended MoTe<sub>2</sub> using electric double layer gating," *ACS Nano*, vol. 17, no. 22, pp. 22388–22398, 2023. [Online]. Available: <https://pubs.acs.org/doi/10.1021/acsnano.3c04701>

- [12] Y. Li, K.-A. N. Duerloo, K. Wauson, and E. J. Reed, "Structural semiconductor-to-semimetal phase transition in two-dimensional materials induced by electrostatic gating," *Nat. Commun.*, vol. 7, no. 1, 2016, Art. no. 10671. [Online]. Available: <https://www.nature.com/articles/ncomms10671>

- [13] Y. Wang et al., "Structural phase transition in monolayer MoTe<sub>2</sub> driven by electrostatic doping," *Nature*, vol. 550, no. 7677, pp. 487–491, 2017. [Online]. Available: <https://www.nature.com/articles/nature24043>

- [14] G. Tsutsui, S. Mochizuki, N. Loubet, S. W. Bedell, and D. K. Sadana, "Strain engineering in functional materials," *AIP Adv.*, vol. 9, no. 3, 2019, Art. no. 30701. [Online]. Available: <https://pubs.aip.org/adv/article/9/3/030701/1076453/Strain-engineering-in-functional-materials>

- [15] S. Orain, V. Fiori, D. Villanueva, A. Dray, and C. Ortolland, "Method for managing the stress due to the strained nitride capping layer in MOS transistors," *IEEE Trans. Electron Devices*, vol. 54, no. 4, pp. 814–821, Apr. 2007. [Online]. Available: <http://ieeexplore.ieee.org/document/4142897/>

- [16] A. Azizimanesh, T. Peña, A. Sewaket, W. Hou, and S. M. Wu, "Uniaxial and biaxial strain engineering in 2d MoS<sub>2</sub> with lithographically patterned thin film stressors," *Appl. Phys. Lett.*, vol. 118, no. 21, 2021, Art. no. 213104. [Online]. Available: <https://pubs.aip.org/apl/article/118/21/213104/39969/Uniaxial-and-biaxial-strain-engineering-in-2D-MoS2>

- [17] T. Peña, S. A. Chowdhury, A. Azizimanesh, A. Sewaket, H. Askari, and S. M. Wu, "Strain engineering 2d MoS<sub>2</sub> with thin film stress capping layers," *2D Mater.*, vol. 8, no. 4, 2021, Art. no. 45001. [Online]. Available: <https://iopscience.iop.org/article/10.1088/2053-1583/ac08f2>

- [18] G. G. Stoney, "The tension of metallic films deposited by electrolysis," *Proc. Royal Soc. London. Series A, Containing Papers Math. Phys. Character*, vol. 82, no. 553, pp. 172–175, 1909. [Online]. Available: <https://royalsocietypublishing.org/doi/10.1098/rspa.1909.0021>

- [19] J. S. Kim, K. W. Paik, and S. H. Oh, "The multilayer-modified stoney's formula for laminated polymer composites on a silicon substrate," *J. Appl. Phys.*, vol. 86, no. 10, pp. 5474–5479, 1999. [Online]. Available: <https://pubs.aip.org/jap/article/86/10/5474/490307/The-multilayer-modified-Stoney-s-formula-for>

- [20] G. Janssen, M. Abdalla, F. Van Keulen, B. Pujada, and B. Van Venrooy, "Celebrating the 100th anniversary of the stoney equation for film stress: Developments from polycrystalline steel strips to single crystal silicon wafers," *Thin Solid Films*, vol. 517, no. 6, pp. 1858–1867, 2009. [Online]. Available: <https://linkinghub.elsevier.com/retrieve/pii/S0040609008007669>

- [21] W. Hou et al., "Nonvolatile ferroelastic strain from flexoelectric internal bias engineering," *Phys. Rev. Appl.*, vol. 17, no. 2, 2022, Art. no. 24013. [Online]. Available: <https://link.aps.org/doi/10.1103/PhysRevApplied.17.024013>

- [22] Y.-J. Zhang, R.-N. Wang, G.-Y. Dong, S.-F. Wang, G.-S. Fu, and J.-L. Wang, "Mechanical properties of 1T-, 1T', and 1H-MX<sub>2</sub> monolayers and their 1H/1T'-MX<sub>2</sub> (m = mo, w and x = s, se, te) heterostructures," *AIP Adv.*, vol. 9, no. 12, 2019, Art. no. 125208. [Online]. Available: <https://pubs.aip.org/adv/article/9/12/125208/1076895/Mechanical-properties-of-1T-1T-and-1H-MX2>

- [23] J.-H. Lee et al., "CMOS-compatible catalytic growth of graphene on a silicon dioxide substrate," *Appl. Phys. Lett.*, vol. 109, no. 5, 2016, Art. no. 053102. [Online]. Available: <https://pubs.aip.org/apl/article/109/5/053102/32748/CMOS-compatible-catalytic-growth-of-graphene-on-a>

- [24] T. Peña, J. Holt, A. Sewaket, and S. M. Wu, "Ultrasonic delamination based adhesion testing for high-throughput assembly of van der Waals heterostructures," *J. Appl. Phys.*, vol. 132, no. 22, 2022, Art. no. 225302. [Online]. Available: <https://pubs.aip.org/jap/article/132/22/225302/2838154/Ultrasonic-delamination-based-adhesion-testing-for>

- [25] W. Praepattharapisut, W. Pengchan, T. Phetchakul, and A. Poyai, "Yield analysis by poisson yield model based on the defect analysis with derivative method," in *Proc. ECTI-CON*, 2014, pp. 1–4. [Online]. Available: <http://ieeexplore.ieee.org/document/6839864/>

- [26] M. Raghavachari, A. Srinivasan, and P. Sullo, "Poisson mixture yield models for integrated circuits: A critical review," *Microelectron. Rel.*, vol. 37, no. 4, pp. 565–580, 1997. [Online]. Available: <https://linkinghub.elsevier.com/retrieve/pii/S0026271496000649>

[27] W. Zheng et al., "The origin and mitigation of defects induced by metal evaporation in 2D materials," *Mater. Sci. Eng. R, Rep.*, vol. 160, Sep. 2024, Art. no. 100831. [Online]. Available: <https://linkinghub.elsevier.com/retrieve/pii/S0927796X24000615>

[28] A. V. Ferris-Prabhu, "Role of defect size distribution in yield modeling," *IEEE Trans. Electron Devices*, vol. 32, no. 9, pp. 1727–1736, Sep. 1985. [Online]. Available: <http://ieeexplore.ieee.org/document/1484933/>

[29] C. Hess and L. H. Weiland, "Wafer level defect density distribution using checkerboard test structures," in *Proc. Int. Conf. Microelectron. Test Struct.*, vol. 7, 1998, pp. 101–106. [Online]. Available: <http://ieeexplore.ieee.org/document/688050/>

[30] Y. Liu et al., "Approaching the Schottky–Mott limit in van der Waals metal–semiconductor junctions," *Nature*, vol. 557, no. 7707, pp. 696–700, 2018. [Online]. Available: <https://www.nature.com/articles/s41586-018-0129-8>

[31] Y. Zhang, H. L. Zhao, S. Huang, M. A. Hossain, and A. M. Van Der Zande, "Enhancing carrier mobility in monolayer MoS<sub>2</sub> transistors with process-induced strain," *ACS Nano*, vol. 18, no. 19, pp. 12377–12385, 2024. [Online]. Available: <https://pubs.acs.org/doi/10.1021/acsnano.4c01457>

[32] Y. Zhou, L. Tao, Z. Chen, H. Lai, W. Xie, and J.-B. Xu, "Defect etching of phase-transition-assisted CVD-grown 2h-MoTe<sub>2</sub>," *Small*, vol. 17, no. 32, 2021, Art. no. 2102146. [Online]. Available: <https://onlinelibrary.wiley.com/doi/10.1002/smll.202102146>