LETTER • OPEN ACCESS

## 2 kV Al<sub>0.64</sub>Ga<sub>0.36</sub>N-channel high electron mobility transistors with passivation and field plates

To cite this article: Md Tahmidul Alam *et al* 2025 *Appl. Phys. Express* **18** 016504

View the [article online](#) for updates and enhancements.

### You may also like

- [\$V\_{ox}/E\_{ox}\$ -Driven Breakdown of Ultrathin SiON Gate Dielectrics in p-Type Metal Oxide Semiconductor Field Effect Transistors under Low-Voltage Inversion Stress](#)

Shimpei Tsujikawa, Katsuya Shiga, Hiroshi Umeda *et al.*

- [Investigation of electrical breakdown of polymeric insulating materials using a technique of pre-breakdown current measurements](#)

M Hikita, T Hirose, Y Ito *et al.*

- [Differentiation Between Electric Breakdowns and Dielectric Breakdown in Thin Silicon Oxides](#)

J. C. Jackson, T. Robinson, O. Oralkan *et al.*

**ECS** The Electrochemical Society

Advancing solid state & electrochemical science & technology

**SUSTAINABLE TECHNOLOGIES**

**249th ECS Meeting**

May 24-28, 2026

Seattle, WA, US

Washington State Convention Center

**Spotlight Your Science**

**Submission deadline:**

**December 5, 2025**

**SUBMIT YOUR ABSTRACT**

## 2 kV $\text{Al}_{0.64}\text{Ga}_{0.36}\text{N}$ -channel high electron mobility transistors with passivation and field plates

Md Tahmidul Alam<sup>1\*</sup> , Jiahao Chen<sup>1</sup>, Kenneth Stephenson<sup>2</sup>, Md Abdullah-Al Mamun<sup>2</sup>, Abdullah Al Mamun Mazumder<sup>2</sup>, Shubhra S. Pasayat<sup>1</sup>, Asif Khan<sup>2</sup>, and Chirag Gupta<sup>1</sup>

<sup>1</sup>Department of Electrical and Computer Engineering, University of Wisconsin-Madison, WI 53706, United States of America

<sup>2</sup>Department of Electrical Engineering, University of South Carolina, Columbia, SC 29208, United States of America

\*E-mail: [malam9@wisc.edu](mailto:malam9@wisc.edu)

Received October 25, 2024; revised December 4, 2024; accepted December 11, 2024; published online January 14, 2025

High voltage ( $\sim 2$  kV)  $\text{Al}_{0.64}\text{Ga}_{0.36}\text{N}$ -channel high electron mobility transistors were fabricated with an on-resistance of  $\sim 75 \Omega \cdot \text{mm}$  ( $\sim 21 \text{ m}\Omega \cdot \text{cm}^2$ ). Two field plates of variable dimensions were utilized to optimize the breakdown voltage. The breakdown voltage reached  $> 3$  kV (tool limit) before passivation however it reduced to  $\sim 2$  kV after  $\text{Si}_3\text{N}_4$  surface passivation and field plate deposition. The breakdown voltage and on-resistance demonstrated a strong linear correlation in a scattered plot of  $\sim 50$  measured transistors. The fabricated transistors were electrically characterized and benchmarked against the state-of-the-art high-voltage ( $> 1$  kV) Al-rich ( $> 40\%$ ) AlGaN-channel transistors in breakdown voltage and on-resistance, indicating significant progress. © 2025 The Author(s). Published on behalf of The Japan Society of Applied Physics by IOP Publishing Ltd

**W**ide bandgap results in a high critical field in materials therefore wide bandgap semiconductors such as GaN (bandgap,  $E_G = 3.4$  eV) and SiC ( $E_G = 3.26$  eV) are popular as power electronic materials, having a critical field of  $3.3 \text{ MV cm}^{-1}$  and  $3 \text{ MV cm}^{-1}$ , respectively.<sup>1–3</sup> The bandgap and critical field of GaN can further be increased by alloying it with AlN ( $E_G = 6$  eV, breakdown field =  $11 \sim 15 \text{ MV cm}^{-1}$ ) and making ternary semiconductors such as  $\text{Al}_x\text{G}_{1-x}\text{N}$ .<sup>4–6</sup> Higher Al-composition AlGaN is expected to have a larger critical field and blocking voltage in power high electron mobility transistors (HEMTs) due the larger bandgap.<sup>7,8</sup> However, the fabrication of a high-Al composition AlGaN-channel HEMT is challenging due to difficulty in making good ohmic contacts and low electron mobility leading to poor on-resistance ( $R_{ON}$ ).<sup>9,10</sup> Grading the AlGaN-channel (from-high-to-low Al-composition) can facilitate the implementation of ohmic contacts with a reasonable on-resistance.<sup>11,12</sup> The  $R_{ON}$  can further be improved by doping the barrier that can contribute electrons to the channel and lower the sheet resistance.<sup>13</sup>

Yet, accomplishment of high breakdown voltage ( $> 1$  kV) and low on-resistance simultaneously remains challenging in Al-rich ( $> 40\%$ ) AlGaN-channel transistors and there are limited reports. Previous attempts include: fabrication of 1500 V AlGaN-channel (40% Al) HEMT by D. Khachariya et al. with an on-resistance of  $\sim 420 \Omega \cdot \text{mm}$ , and 1800 V AlGaN-channel (51% Al) HEMT by H. Tokuda et al. with an on-resistance of  $\sim 375 \Omega \cdot \text{mm}$ .<sup>8,14</sup> H. Okumura et al. demonstrated a 2370 V AlN-channel (100% Al composition) MESFET but the on-resistance exceeded 100 k $\Omega \cdot \text{mm}$ .<sup>15</sup> All these works utilized annealed metal stacks for ohmic contact formation. R. Maeda et al. fabricated 1635 V  $\text{Al}_{0.50}\text{Ga}_{0.50}\text{N}$ -channel HEMTs with an  $R_{ON}$  of  $40 \Omega \cdot \text{mm}$  using a more complicated regrown ohmic contact process.<sup>16</sup> However, none of these works included passivation of the top (barrier) surface. The unpassivated barrier surface can potentially have numerous trap states and overstate the breakdown voltage by behaving like field plates and can also impact the dynamic performance of the

transistors.<sup>17</sup> Until now, there has been no demonstration of  $> 1$  kV Al-rich ( $> 40\%$ ) lateral transistors with passivation and field plates. In this work, we fabricated 2 kV  $\text{Al}_{0.64}\text{Ga}_{0.36}\text{N}$ -channel HEMTs on sapphire substrates with passivation and field plates. Annealed ohmic contacts were utilized in these transistors. Prior to passivation the breakdown voltage surpassed 3 kV (tool limit) with an  $R_{ON}$  of  $\sim 85 \Omega \cdot \text{mm}$ . However, after passivation the breakdown voltage was reduced to 2 kV. The reduction of breakdown voltage after passivation was attributed to the field plate effect of charged surface states in the unpassivated HEMT.<sup>17</sup> Electrical characterizations such as output IV curves, transfer characteristics, and preliminary dynamic response were conducted. This work was benchmarked in breakdown voltage and on-resistance against the state-of-the-art high voltage ( $> 1$  kV), high Al-composition ( $> 40\%$  Al) AlGaN-channel lateral transistors and high voltage ( $> 1$  kV)  $\text{Ga}_2\text{O}_3$  lateral transistors well, suggesting that high breakdown voltage and low on-resistance has been achieved simultaneously.

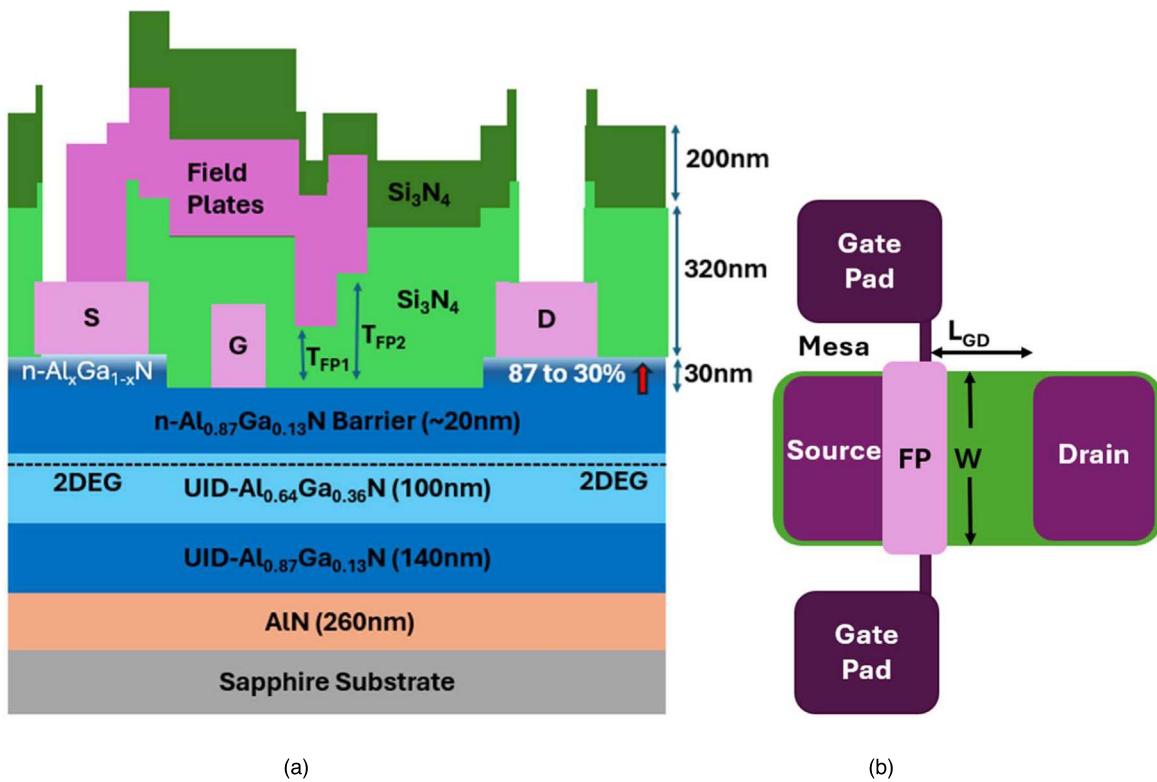

The structure of the fabricated device is shown in Fig. 1. The epitaxial structure consists of graded n- $\text{Al}_x\text{Ga}_{1-x}\text{N}$  ( $30 \text{ nm}$ ,  $x = 0.30 \sim 0.87$ )/n- $\text{Al}_{0.87}\text{Ga}_{0.13}\text{N}$  barrier ( $\sim 20 \text{ nm}$ ,  $N_D = \sim 10^{19} \text{ cm}^{-3}$ )/ $\text{Al}_{0.64}\text{Ga}_{0.36}\text{N}$  channel ( $100 \text{ nm}$ )/ $\text{Al}_{0.87}\text{Ga}_{0.13}\text{N}$  ( $140 \text{ nm}$ )/AlN ( $260 \text{ nm}$ ) grown on sapphire substrate by metal organic chemical vapor deposition (MOCVD). Device fabrication started with solvent cleaning (3 min Acetone, 3 min IPA and 1 min water with ultrasonic power) and subsequent ohmic lithography. Zr/Al/Mo/Au (15/100/40/30) nm was deposited as ohmic metal stacks then was annealed at  $950^\circ\text{C}$  for 30 s in a  $\text{N}_2$  environment. After that, the graded AlGaN layer was etched up to the  $\sim 20 \text{ nm}$  barrier in the source/drain access region in ICP metal plasma etcher using  $\text{Cl}_2$ . Then, the devices were isolated by a Mesa etch. Following that, Ni/Au (100/100) nm gates were deposited in  $30^\circ$  inclination to ensure side-wall metal coverage. Thereafter, 320 nm PECVD  $\text{Si}_3\text{N}_4$  was deposited for surface passivation. After that, two field plate trenches were etched in the  $\text{Si}_3\text{N}_4$  layer with variable field plate lengths (between

Content from this work may be used under the terms of the [Creative Commons Attribution 4.0 license](#). Any further distribution of this work must maintain attribution to the author(s) and the title of the work, journal citation and DOI.

**Fig. 1.** (a) Cross-section of the 64% AlGaN-channel HEMT. (b) Top-view.

1  $\mu\text{m}$  to 3.5  $\mu\text{m}$ ). Then, bond pads were etched at the metal contacts. Thereafter, field plate metal Ni/Au (200/200) nm was deposited by e-beam evaporation to fill up the field plate trenches. Following that, a 200 nm PECVD  $\text{Si}_3\text{N}_4$  was deposited on top to restrict mechanical movement of the field plate metals and subsequently bond pads were etched. The field plates were source-connected. Gate-to-source length ( $L_{GS}$ ) was 2  $\mu\text{m}$ , gate length ( $L_G$ ) was 2  $\mu\text{m}$  with three variations of gate–drain distance ( $L_{GD}$ ) = 8  $\mu\text{m}$ , 15  $\mu\text{m}$  and 20  $\mu\text{m}$ . The dielectric thickness beneath the field plates were constant: 120 nm and 270 nm of  $\text{Si}_3\text{N}_4$  under the first and second field plate, respectively. More detailed dimensions of the transistor are listed in Table I.

DC and pulsed measurements were done in Keysight's B1505A SMU (source-measurement unit). All measurements were done after passivation and field plates deposition. During breakdown voltage measurement the transistors were covered with flourinert FC-40 to prevent air breakdown. The breakdown voltage was also measured prior to passivation to compare the transistors with the state-of-the-art high Al-composition (>40%), >1 kV AlGaN-channel HEMTs.

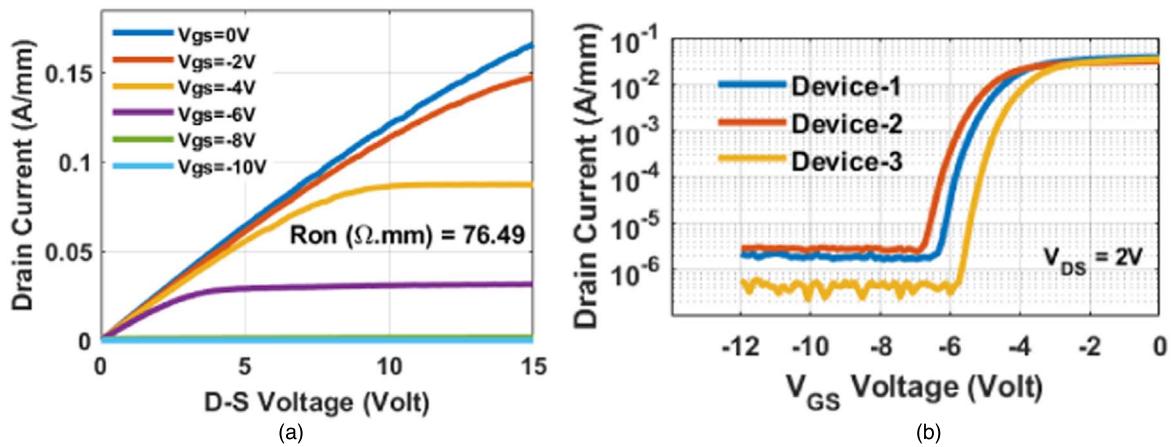

The average  $R_{\text{ON}}$  of transistors with  $L_{GD}$  = 8  $\mu\text{m}$ , 15  $\mu\text{m}$  and 20  $\mu\text{m}$  were 60  $\Omega\text{.mm}$  ( $\sim 9.5 \text{ m}\Omega \text{ cm}^2$ ),  $\sim 68 \Omega\text{.mm}$  ( $\sim 15.5 \text{ m}\Omega \text{ cm}^2$ ) and 75  $\Omega\text{.mm}$  ( $\sim 21 \text{ m}\Omega \text{ cm}^2$ ), respectively, as found from the output  $IV$  curves. The specific on-resistance in  $\text{m}\Omega\text{.cm}^2$  was calculated by multiplying the  $R_{\text{ON}}$  ( $\Omega\text{.mm}$ ) by the total pitch of the channel ( $L_{\text{SD}} + 2L_{\text{T}}$ ). The contact resistance ( $R_c$ ), sheet resistance ( $R_{\text{SH}}$ ) and transfer length ( $2L_{\text{T}}$ ) were 4.7  $\Omega\text{.mm}$ , 2282  $\Omega/\square$  and 4  $\mu\text{m}$ , respectively, as calculated from TLM measurements.<sup>18)</sup> Figure 2(a) shows the  $IV$  curves of a transistor with  $L_{GD}$  = 20  $\mu\text{m}$ .

The transfer curves of some ‘identical’ transistors with  $L_{GD}$  = 20  $\mu\text{m}$  is shown in Fig. 2(b). The figure shows that the threshold voltage ( $V_{\text{TH}}$ ) varies between -8 V to -6.5 V

**Table I.** Description of the transistor dimensions.

| Parameter | Description                         | Value                    |

|-----------|-------------------------------------|--------------------------|

| $L_G$     | Gate length                         | 2 $\mu\text{m}$          |

| $L_{GS}$  | Gate to source distance             | 2 $\mu\text{m}$          |

| $L_{GD}$  | Gate to drain distance              | 8,15 or 20 $\mu\text{m}$ |

| $W$       | Width                               | 100 $\mu\text{m}$        |

| $T_{FP1}$ | Dielectric under first field plate  | 120 nm                   |

| $T_{FP2}$ | Dielectric under second field plate | 270 nm                   |

(assuming 1 mA  $\text{mm}^{-1}$  to be the threshold current) with a variation of  $\sim 1.5$  V. This difference in  $V_{\text{TH}}$  might be due to the non-uniform distribution of Al composition or doping of the graded barrier layer or, due to the non-uniform etch rate of the same layer in  $\text{Cl}_2$ . The on/off ratio was up to  $>10^5$  and was limited by the tool’s noise level. No change was observed in the  $IV$  and transfer characteristics before passivation and after passivation and field plate deposition.

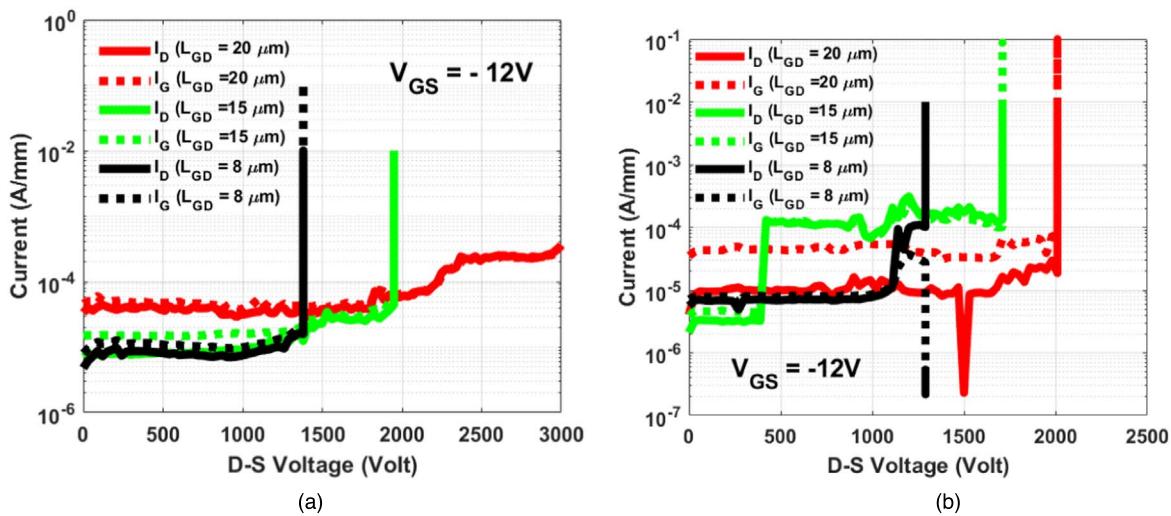

The breakdown voltages of the HEMTs were measured before and after surface passivation and field plates deposition. Figure 3(a) shows the breakdown measurements before passivation, breakdown voltages were  $>3$  kV, 1950 V and 1380 V, respectively, (tool limit = 3 kV) for  $L_{GD}$  = 20  $\mu\text{m}$ , 15  $\mu\text{m}$  and 8  $\mu\text{m}$ . However, it reduced to lower voltages (2 kV or below) for all dimensions after passivation and field plates deposition as shown in Fig. 3(b). For  $L_{GD}$  = 20  $\mu\text{m}$ , 15  $\mu\text{m}$  and 8  $\mu\text{m}$ , the breakdown voltage after passivation was 2010 V, 1710 V and 1290 V respectively at best case. High breakdown voltage before surface passivation can be attributed to the charged surface states acting as field plates.<sup>17)</sup> These charged surface states in unpassivated HEMTs can potentially impact the dynamic or switching behavior of the transistor.<sup>19-21)</sup> Therefore, the breakdown voltage after passivation should be taken as the true breakdown voltage.

Fig. 2. For  $L_{GD} = 20 \mu\text{m}$  (a) IV characteristics. (b) Transfer curves of some ‘identical’ transistors.

Fig. 3. Breakdown measurements (a) before passivation (b) after passivation and field plates deposition.

The breakdown field was  $1.61 \text{ MV cm}^{-1}$ ,  $1.14 \text{ MV cm}^{-1}$  and  $1 \text{ MV cm}^{-1}$  for  $L_{GD} = 8 \mu\text{m}$ ,  $15 \mu\text{m}$  and  $20 \mu\text{m}$  HEMT, respectively. The trend of breakdown field reduction with high breakdown voltage is noticeable in these measurements. This trend was also observed in previous works of AlGaN-channel HEMTs and other lateral wide bandgap materials such as  $\text{Ga}_2\text{O}_3$  as well.<sup>22,23</sup> For example, the breakdown field in earlier works of AlGaN-channel ( $>1 \text{ kV}$ ,  $>40\%$  Al) HEMTs were  $1.2 \text{ MV cm}^{-1}$  for  $L_{GD} = 15 \mu\text{m}$ ,  $1.67 \text{ MV cm}^{-1}$  for  $L_{GD} = 9 \mu\text{m}$  and  $3 \text{ MV cm}^{-1}$  for  $L_{GD} = 5.4 \mu\text{m}$ .<sup>8,14,16</sup> The reason behind this can possibly be attributed to the electric field lowering or punch-through in longer channel lengths.<sup>22</sup> Therefore, efficient electric field management might play a crucial role in achieving high field in high voltage lateral transistors. Electric field might be enhanced in high voltage transistors through optimization of field plates number and geometry.<sup>24–26</sup> Our future studies will focus on the results of these optimizations.

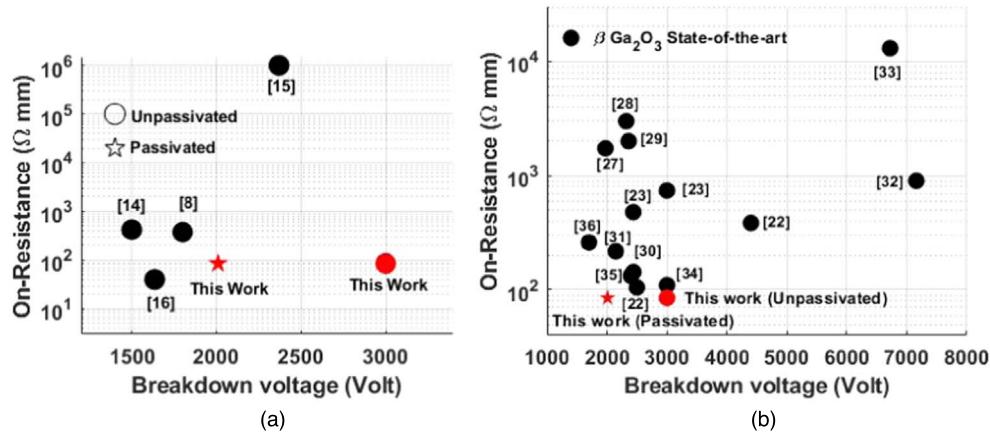

In Fig. 4(a) our fabricated transistors were benchmarked against the state-of-the-art Al-rich ( $>40\%$ ) AlGaN-channel lateral transistors with  $>1 \text{ kV}$  breakdown voltage. Two key performance matrices of power devices, breakdown voltage and on-resistance, were compared in this figure, indicating that both the passivated and unpassivated HEMT of this work outperformed prior works. In Fig. 4(b) this work was

benchmarked against the state-of-the-art lateral transistors of another ultra-wide bandgap power semiconductor material, gallium oxide’s ( $\text{Ga}_2\text{O}_3$ ).<sup>22,23,27–36</sup> This figure suggests that Al-rich AlGaN-channel transistors have the potential to achieve lower on-resistance for the same breakdown voltage compared to  $\text{Ga}_2\text{O}_3$  transistors. However, further study and optimizations are required to draw any strong conclusion.

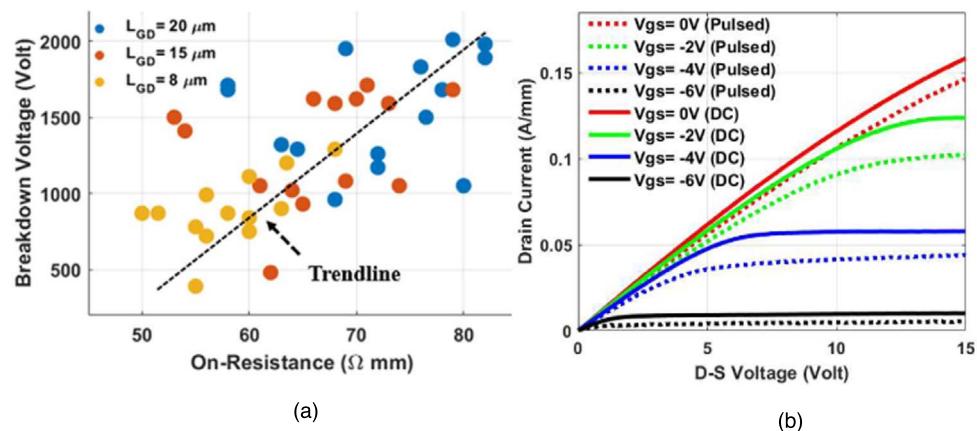

The breakdown voltage and on-resistance were measured in  $\sim 50$  transistors with different field plate lengths as shown in Fig. 5(a). The scatter plot indicates a strong linear correlation between the breakdown voltage and on-resistance. The deviation of the data points from the trendline possibly originated from the variation of field plate dimensions (field plate lengths were between  $1\text{--}3 \mu\text{m}$ ). This suggests that field plate design can play a vital role in optimizing the performance of the HEMTs in  $\text{BV}-R_{ON}$  benchmarks. Our future studies will focus on quantifying the effect of field plate dimensions on the breakdown voltage.

Preliminary dynamic characterization was done by pulsed IV measurements in  $40 \text{ V}$  off-state voltage with  $100 \mu\text{s}$  pulse width.  $40 \text{ V}$  was the maximum off-state voltage allowed by the measurement equipment. The increase in  $R_{ON}$  in pulse IV measurements was  $\sim 5\%$  (at  $V_{GS} = 0 \text{ V}$ ,  $V_{DS} = 1 \text{ V}$ ), and the amount of current collapse was  $<10\%$  [Fig. 5(b)]. These preliminary results suggest that the transistors are promising

**Fig. 4.** Benchmarking this work against the state-of-the-art high voltage (> 1 kV). (a) High Al composition (> 40%) AlGaN-channel transistors. (b)  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> lateral transistors.

**Fig. 5.** (a) Scatter plot of breakdown voltage and  $R_{ON}$  of ~50 measured transistors. (b) Pulsed and DC IV curves with  $L_{GD} = 20 \mu\text{m}$  ( $V_{GSQ} = -12 \text{ V}$ ,  $V_{DSQ} = 40 \text{ V}$ ,  $PW = 100 \mu\text{s}$ ).

for switching applications, however, high-voltage (off-state voltage close to the range of the application class, for example, 650 V) switching characterization should be done for practical applications of these devices in high voltage modules. Our future studies are expected to publish high-voltage (>650 V) switching characteristics with suitable equipment setup.

In conclusion, high aluminum composition (64%) AlGaN-channel HEMTs were grown and fabricated demonstrating high breakdown voltage (3 kV and 2 kV before and after passivation). The breakdown field was 1.61 MV cm<sup>-1</sup>, 1.14 MV cm<sup>-1</sup> and 1 MV cm<sup>-1</sup> for  $L_{GD} = 8 \mu\text{m}$ , 15  $\mu\text{m}$  and 20  $\mu\text{m}$ , respectively. Two field plates with variable dimensions were utilized for optimizing the breakdown voltage or breakdown field. The fabricated transistors had low on resistance of 60 Ω.mm (9.5 mΩ cm<sup>2</sup>), 68 Ω.mm (15.5 mΩ cm<sup>2</sup>), and 75 Ω.mm (21 mΩ cm<sup>2</sup>) for  $L_{GD} = 8 \mu\text{m}$ , 15  $\mu\text{m}$  and 20  $\mu\text{m}$ , respectively. The state-of-the-art high voltage (>1 kV), high-Al composition (>38%) AlGaN-channel transistors and high voltage (>1 kV) Ga<sub>2</sub>O<sub>3</sub> transistors were benchmarked against this work in the two crucial power electronic performance matrices of breakdown voltage and on-resistance, indicating noteworthy advance.

**Acknowledgments** We gratefully acknowledge the partial support by NSF ASCENT (award No. ECCS 2328137), AFOSR under award No. FA9550-23-1-0501 (Program Manager: Dr Kenneth Goretta) and ARPA-E Award DE-AR0001825.

**ORCID iDs** Md Tahmidul Alam <https://orcid.org/0009-0008-6556-839X>

- 1) M. Shur, *Solid-State Electronics* **155**, 65 (2019).

- 2) T. J. Flack, B. N. Pushpakaran, and S. B. Bayne, *J. Electron. Mater.* **45**, 2673 (2016).

- 3) F. Roccaforte, P. Fiorenza, G. Greco, R. Lo Nigro, F. Giannazzo, F. Iucolano, and M. Saggio, *Microelectron. Eng.* **187-188**, 66 (2018).

- 4) R. J. Kaplar, A. A. Allerman, A. M. Armstrong, M. H. Crawford, J. R. Dickerson, A. J. Fischer, A. G. Baca, and E. A. Douglas, *ECS J. Solid State Sci. Technol.* **6**, Q3061 (2016).

- 5) A. A. Shuvo, M. R. Islam, and M. T. Hasan, *J. Comput. Electron.* **19**, 1100 (2020).

- 6) J. Y. Tsao et al., *Adv. Electron. Mater.* **4**, 1600501 (2018).

- 7) T. Nanjo, A. Imai, Y. Suzuki, Y. Abe, T. Oishi, M. Suita, E. Yagyu, and Y. Tokuda, *IEEE Trans. Electron Devices* **60**, 1046 (2013).

- 8) H. Tokuda, M. Hatano, N. Yafune, S. Hashimoto, K. Akita, Y. Yamamoto, and M. Kuzuhara, *Appl. Phys. Express* **3**, 121003 (2010).

- 9) H. Xue et al., *Solid-State Electronics* **164**, 107696 (2020).

- 10) K. Hussain et al., *Appl. Phys. Express* **16**, 014005 (2023).

- 11) M. Gaevski, S. Mollah, K. Hussain, J. Letton, A. Mamun, M. U. Jewel, M. V. S. Chandrashekhar, G. Simin, and A. Khan, *Appl. Phys. Express* **13**, 094002 (2020).

- 12) H. Ye, M. Gaevski, G. Simin, A. Khan, and P. Fay, *Appl. Phys. Lett.* **120**, 103505 (2022).

- 13) H. Xue, K. Hussain, V. Talesara, T. Razzak, M. Gaevski, S. Mollah, S. Rajan, A. Khan, and W. Lu, *Phys. status solidi (RRL)—Rapid Res. Lett.* **15**, 2000576 (2021).

- 14) D. Khachariya et al., *Appl. Phys. Lett.* **120**, 172106 (2022).

- 15) H. Okumura, S. Suihkonen, J. Lemettinen, A. Uedono, Y. Zhang, D. Piedra, and T. Palacios, *Jpn. J. Appl. Phys.* **57**, 04FR11 (2018).

- 16) R. Maeda, K. Ueno, A. Kobayashi, and H. Fujioka, *Appl. Phys. Express* **15**, 031002 (2022).

**17)** H. Xing, Y. Dora, A. Chini, S. Heikman, S. Keller, and U. K. Mishra, *IEEE Electron Device Lett.* **25**, 161 (2004).

**18)** A. Mamun, K. Hussain, R. Floyd, M. D. Alam, M. V. S. Chandrashekhar, G. Simin, and A. Khan, *Appl. Phys. Express* **16**, 061001 (2023).

**19)** V. Tilak, B. Green, H. Kim, R. Dimitrov, J. Smart, W. J. Schaff, J. R. Shealy, and L. F. Eastman, 2000 IEEE Int. Symp. on Compound Semiconductors. Proc. of the IEEE Twenty-Seventh Int. Symp. on Compound Semiconductors (Cat. No.00TH8498), 2000 357.

**20)** X. Li, N. Posthuma, B. Bakeroot, H. Liang, S. You, Z. Wu, M. Zhao, G. Groeseneken, and S. Decoutere, *IEEE Trans. Power Electron.* **36**, 4927 (2021).

**21)** T. Hashizume, K. Nishiguchi, S. Kaneki, J. Kuzmik, and Z. Yatabe, *Mater. Sci. Semicond. Process.* **78**, 85 (2018).

**22)** A. Bhattacharyya, S. Sharma, F. Alema, P. Ranga, S. Roy, C. Peterson, G. Seryogin, A. Osinsky, U. Singisetti, and S. Krishnamoorthy, *Appl. Phys. Express* **15**, 061001 (2022).

**23)** Y. Lv et al., *Phys. status solidi (RRL)—Rapid Res. Lett.* **14**, 1900586 (2020).

**24)** M. Kaddeche, A. Telia, and A. Soltani, Int. Conf. on Microelectronics - ICM, 2009 362.

**25)** N. Shi, K. Wang, B. Zhou, J. Weng, and Z. Cheng, *Micromachines* **13**, 702 (2022).

**26)** M. T. Alam, J. Chen, R. Bai, S. S. Pasayat, and C. Gupta, *IEEE Trans. Electron Devices* **71**, 733 (2024).

**27)** K. Zeng, A. Vaidya, and U. Singisetti, *Appl. Phys. Express* **12**, 081003 (2019).

**28)** J. K. Mun, K. Cho, W. Chang, H-W. Jung, and J. Do, *ECS J. Solid State Sci. Technol.* **8**, Q3079 (2019).

**29)** Y. Lv, X. Zhou, S. Long, S. Liang, X. Song, X. Zhou, H. Dong, Y. Wang, Z. Feng, and S. Cai, *Semicond. Sci. Technol.* **34**, 11LT02 (2019).

**30)** A. Bhattacharyya, P. Ranga, S. Roy, C. Peterson, F. Alema, G. Seryogin, A. Osinsky, and S. Krishnamoorthy, *IEEE Electron Device Lett.* **42**, 1272 (2021).

**31)** C. Peterson, F. Alema, A. Bhattacharyya, Z. Ling, S. Roy, A. Osinsky, and S. Krishnamoorthy, *Appl. Phys. Lett.* **124**, 082104 (2024).

**32)** S. Sharma, L. Meng, A. F. M. A. U. Bhuiyan, Z. Feng, D. Eason, H. Zhao, and U. Singisetti, *IEEE Electron Device Lett.* **43**, 2029 (2022).

**33)** S. Sharma, K. Zeng, S. Saha, and U. Singisetti, *IEEE Electron Device Lett.* **41**, 836 (2020).

**34)** A. Bhattacharyya, S. Roy, P. Ranga, C. Peterson, and S. Krishnamoorthy, *IEEE Electron Device Lett.* **43**, 1637 (2022).

**35)** D. M. Dryden et al., *IEEE Electron Device Lett.* **43**, 1307 (2022).

**36)** Y. Lv et al., *IEEE Electron Device Lett.* **41**, 537 (2020).