LETTER • OPEN ACCESS

## 3 kV monolithic bidirectional GaN HEMT on sapphire

To cite this article: Md Tahmidul Alam *et al* 2025 *Appl. Phys. Express* **18** 016501

View the [article online](#) for updates and enhancements.

### You may also like

- [Breakdown mechanism in hydrogen microdischarges from direct-current to 13.56 MHz](#)

M Klas, L Moravsky, Š Matejík et al.

- [Vertical Buffer Leakage and Temperature Effects on the Breakdown Performance of GaN/AlGaN HEMTs on Si Substrate](#)

Fouad Benkhelifa, Stefan Müller, Vladimir M. Polyakov et al.

- [Breakdown voltage measurements in alkali-metal-seeded rare gases at elevated temperatures and atmospheric pressure](#)

H I Ellington

The image is a promotional graphic for the 249th ECS Meeting. It features the ECS logo and the text "The Electrochemical Society Advancing solid state & electrochemical science & technology". On the left, there is a circular logo for "SUSTAINABLE TECHNOLOGIES" with a stylized globe and leaves. The main text on the right reads "Spotlight Your Science" and "Submission deadline: December 5, 2025". A green button at the bottom right says "SUBMIT YOUR ABSTRACT". The background has a blue and green abstract design.

**249th

ECS Meeting**

May 24-28, 2026

Seattle, WA, US

Washington State

Convention Center

**Submission deadline:**

**December 5, 2025**

**SUBMIT YOUR ABSTRACT**

## 3 kV monolithic bidirectional GaN HEMT on sapphire

Md Tahmidul Alam\*<sup>1</sup>, Swarnav Mukhopadhyay, Md Mobinul Haque, Shubhra S. Pasayat, and Chirag Gupta

Department of Electrical and Computer Engineering, University of Wisconsin-Madison, WI 53706, United States of America

\*E-mail: [malam9@wisc.edu](mailto:malam9@wisc.edu)

Received November 13, 2024; revised December 4, 2024; accepted December 5, 2024; published online January 7, 2025

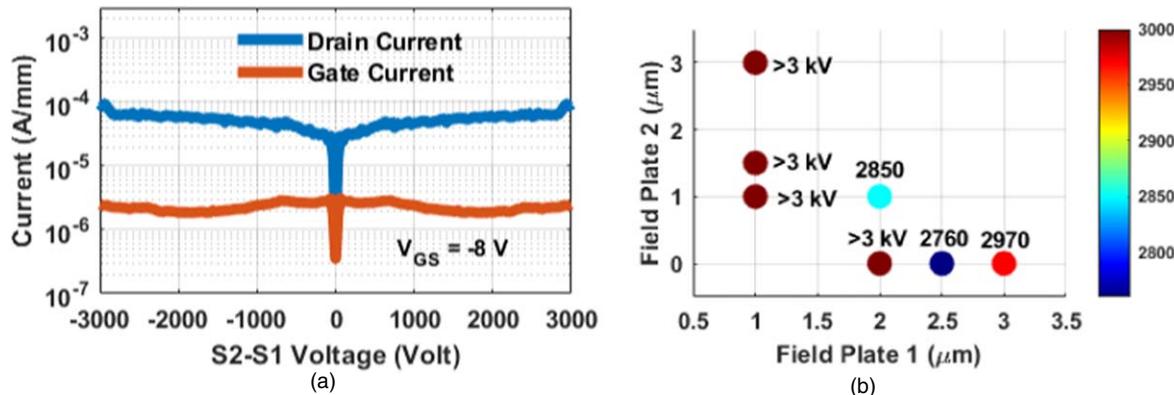

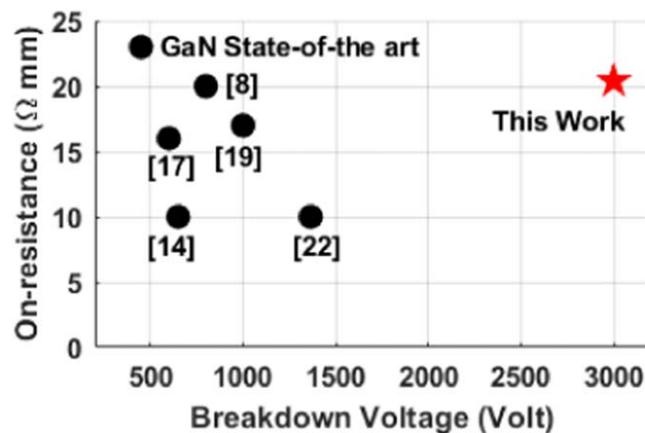

3 kV breakdown voltage was demonstrated in monolithic bidirectional Gallium Nitride (GaN) High Electron Mobility Transistors (HEMTs) having potential applications in 1200 V or 1700 V class power converters. The on-resistance of the fabricated transistors was  $\sim 20 \Omega \cdot \text{mm}$  ( $\sim 11 \text{ m}\Omega \cdot \text{cm}^2$ ). The breakdown voltage was optimized with two field plates on either side of the transistor. Shorter first field plate lengths ( $\leq 2 \mu\text{m}$ ) resulted in higher breakdown voltage and the possible reason was discussed. The transistors had a steep subthreshold swing of  $92 \text{ mV dec}^{-1}$ . The fabricated transistor was benchmarked against the state-of-the-art monolithic bidirectional GaN HEMTs in the performance matrices of breakdown voltage—on resistance, that showed crucial progress. © 2025 The Author(s). Published on behalf of The Japan Society of Applied Physics by IOP Publishing Ltd

**E**fficient and reliable extraction of renewable energy is essential to encounter the anticipated global energy shortage due to the depletion of fossil fuels in a few decades.<sup>1–3</sup> However, the extraction, storage and conversion of energy from renewable sources is still very inefficient compared to theoretical limits because of the lack of high-power, efficient and reliable power converters. Some novel power converters with high power density require bidirectional current and bidirectional blocking capability. Matrix converters, multi-level T-type inverter, current source inverter, solid-state circuit breaker etc. are such examples.<sup>4–8</sup> Typically, bidirectional functionality is achieved by connecting two unidirectional transistors in anti-series or anti-parallel configuration.<sup>9–12</sup> However, these implementations suffer from high on-resistance, high complexity, low reliability and high form-factor due to high device count (four) and internal contacts. Monolithic bidirectional GaN Transistors/Switches (MBDS) can achieve bidirectional current or blocking capability with a single device hence can potentially mitigate these challenges.<sup>13–16</sup>

There are several reports on the structure and operation,<sup>17,18</sup> gate-control schemes<sup>19,20</sup> and substrate termination<sup>21</sup> of monolithic bidirectional GaN HEMTs. One of our previous works demonstrated 1360 V GaN MBDS' with a qualitative design guide for breakdown voltage optimization with field plates.<sup>22</sup> However, there is no demonstration of  $>2$  kV breakdown voltage GaN MBDS—which is essential to make 1200 V class and 1700 V class power converters. In this work, we report 3 kV (measurement limit of the tool = 3 kV) GaN MBDS for the first time with low on-resistance ( $R_{\text{ON}}$ ) of  $\sim 20 \Omega \cdot \text{mm}$  ( $11 \text{ m}\Omega \cdot \text{cm}^2$ ) on sapphire substrate. We utilized and optimized two field plates to maximize the breakdown voltage by electric field management. This work has been benchmarked against the state-of-the-art monolithic bidirectional GaN HEMTs, indicating crucial advance.

Conventionally, normally-off transistors are preferred than normally-on transistors in power converters due to the ability of normally-off transistors to withstand any accidental damage of the gate driving circuitry. Moreover, normally-off transistors need simpler gate drivers.<sup>23,24</sup> However, both normally-on and normally-off transistors have been

commercialized for power electronic applications. Normally-on transistors can be converted to normally-off by cascading a low-voltage silicon transistor.<sup>15,16,25–28</sup> In this work, we fabricated normally-on transistors however similar concepts or designs can be applied to normally-off transistors as well for fabrication of high-voltage devices.

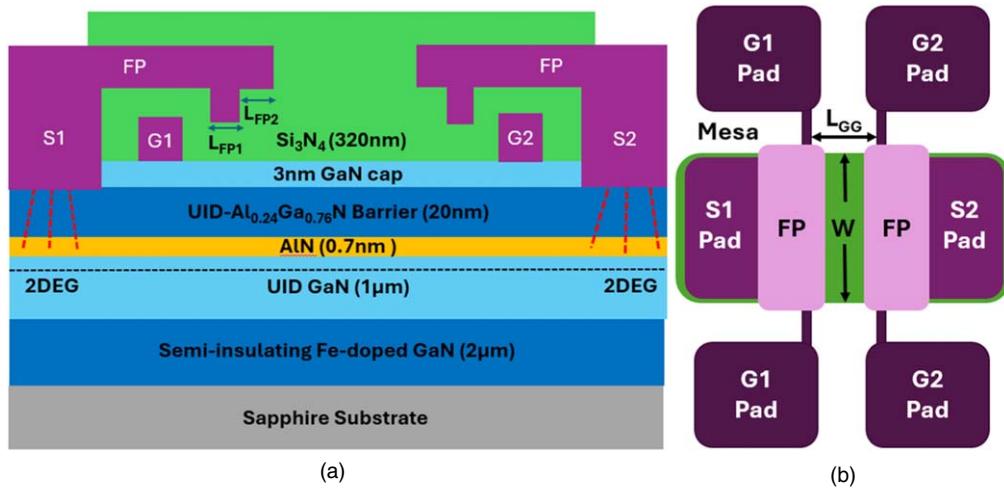

The epitaxial structure- 3 nm GaN (cap)/20 nm Al<sub>0.24</sub>Ga<sub>0.76</sub>N (barrier)/0.7 nm AlN/1  $\mu\text{m}$  UID GaN (channel)/2  $\mu\text{m}$  semi-insulating GaN (Fe doping concentration =  $\sim 5 \times 10^{18} \text{ cm}^{-3}$ )/sapphire substrate was grown in MOCVD (Fig. 1(a)). Sapphire was chosen over silicon as the substrate material to allow higher breakdown voltage beyond 2 kV.<sup>29–32</sup> The fabrication process started with standard solvent cleaning, subsequent ohmic lithography and metal deposition- Ti/Al/Ni/Au (20/120/30/50) nm. The ohmic metal stacks were then annealed at 900 °C for 45 s in N<sub>2</sub> environment. After that, a 750 nm deep mesa etch was performed to isolate the devices. Afterwards, 200 nm thick Ni gates were deposited in a two-phase deposition- in each phase the plane of the sample was inclined at 30° from the horizontal plane to ensure metal coverage in the sidewall. Then, the surface was passivated by a 320 nm thick PECVD Si<sub>3</sub>N<sub>4</sub> layer. Next, two field plate trenches were etched in the Si<sub>3</sub>N<sub>4</sub> layer such that the first and second trench had  $\sim 100$  nm and  $\sim 250$  nm thick Si<sub>3</sub>N<sub>4</sub> left from the AlGaN barrier. Following this, Ni/Au (200/200) nm was deposited as field plate metals on the trenches. Each field plate was connected to the nearest source/ohmic electrode. The field plate lengths ( $L_{\text{FP1}}$  and  $L_{\text{FP2}}$ ) were varied between 1  $\mu\text{m}$  and 3  $\mu\text{m}$  to optimize the breakdown voltage. Gate length ( $L_{\text{G}}$ ), gate-drain distance ( $L_{\text{GD}}$ ), gate-source distance ( $L_{\text{GS}}$ ) and width (distance between Mesa edges (Fig. 1(b))) were 2  $\mu\text{m}$ , 40  $\mu\text{m}$ , 2  $\mu\text{m}$  and 100  $\mu\text{m}$  respectively. Table I contains the detailed structural dimensions of the fabricated transistors.

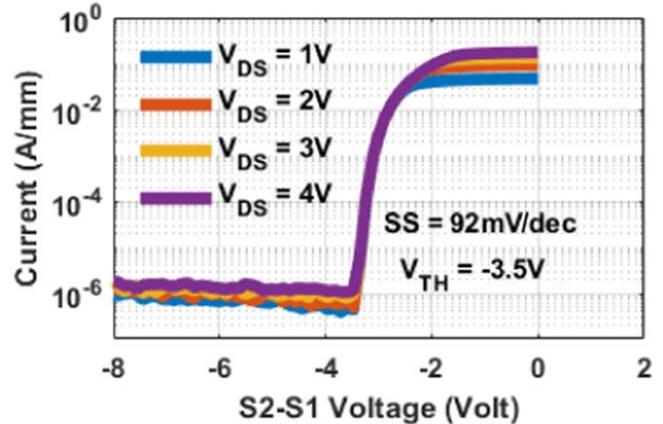

The B1505A (Keysight) source-measurement unit (SMU) was used to perform DC IV, pulsed IV and breakdown voltage measurements. During breakdown measurements the second gate (G<sub>2</sub>) was shorted to the “drain” (S<sub>2</sub>) and the devices were immersed in Fluorinert FC-40 to ensure air does not breakdown before transistor breakdown.

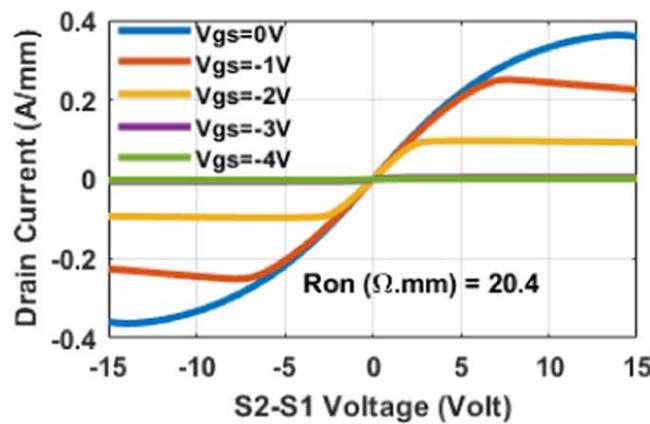

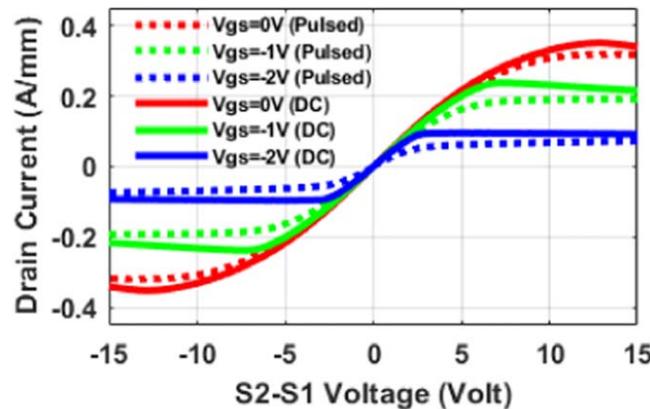

The bidirectional IV characteristics of the MBDS are shown in Fig. 2. For  $L_{\text{GG}} = 40 \mu\text{m}$ , the on-resistance was

Content from this work may be used under the terms of the [Creative Commons Attribution 4.0 license](#). Any further distribution of this work must maintain attribution to the author(s) and the title of the work, journal citation and DOI.

**Fig. 1.** Structure of the monolithic bidirectional GaN HEMT. (a) Cross-section (b) top view. The source pads were 1  $\mu\text{m}$  inside the Mesa edge, the field plates covered 2  $\mu\text{m}$  beyond the Mesa edge.

**Fig. 2.** Bidirectional  $IV$  characteristics of the MBDS with  $L_{\text{GG}} = 40 \mu\text{m}$ ,  $L_G = 2 \mu\text{m}$ ,  $L_{\text{GS}} = 2 \mu\text{m}$ .

**Fig. 3.** Transfer characteristics of the MBDS showing a steep SS of 92 mV dec $^{-1}$  and on/off ratio  $\sim 10^5$ .

**Table I.** Description of the Transistor Dimensions.

| Parameter        | Description                         | Value             |

|------------------|-------------------------------------|-------------------|

| $L_G$            | Gate length                         | 2 $\mu\text{m}$   |

| $L_{\text{GS}}$  | Gate to source distance             | 2 $\mu\text{m}$   |

| $L_{\text{GG}}$  | Gate to gate distance               | 40 $\mu\text{m}$  |

| $L_{\text{FP1}}$ | First field plate length            | 1–3 $\mu\text{m}$ |

| $L_{\text{FP2}}$ | Second field plate length           | 1–3 $\mu\text{m}$ |

| $L_{\text{GF}}$  | Gate to field plate distance        | 1 $\mu\text{m}$   |

| $W$              | Width                               | 100 $\mu\text{m}$ |

| $T_{\text{FP1}}$ | Dielectric under first field plate  | 100 nm            |

| $T_{\text{FP2}}$ | Dielectric under second field plate | 250 nm            |

$\sim 20 \Omega\text{.mm}$  resulting in a specific resistivity of  $\sim 11 \text{ m}\Omega\text{.cm}^2$ . The specific resistivity was found by multiplying the on resistance ( $R_{\text{ON}}$ ) with the total pitch of the channel ( $L_{\text{SD}} + 2L_{\text{T}}$ ). Transfer Length Measurements (TLM) was performed to extract the transfer length ( $2L_{\text{T}} = \sim 7 \mu\text{m}$ ), contact resistance ( $R_c = \sim 0.9 \Omega\text{.mm}$ ) and sheet resistance ( $R_{\text{sheet}} \sim 350 \Omega/\square$ ) of the 2DEG. The extracted value of  $R_{\text{ON}}$  from  $IV$  curves matched closely with the expected  $R_{\text{ON}}$  from  $R_c$  and  $R_{\text{sheet}}$ . The sheet charge density was  $8.35 \times 10^{12} \text{ cm}^{-2}$ , and electron mobility was  $2010 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ , determined by hall measurements.

The threshold voltage ( $V_{\text{TH}}$ ) was stable  $-3.25 \text{ V}$  in multiple measurements (assuming  $1 \text{ mA mm}^{-1}$  to be the cut-off current) as observed from the transfer characteristics in Fig. 3. The subthreshold swing (SS) was steep  $92 \text{ mV dec}^{-1}$  (between  $10^{-4}$  and  $10^{-5} \text{ A mm}^{-1}$ ), on/off ratio was  $>10^5$  and was limited by the tool noise current in the low-current domain. The stable  $V_{\text{TH}}$ , low SS along with high on/off ratio makes this device suitable for high-frequency operations with low conduction and switching losses.

Figure 4(a) depicts the breakdown response of a transistor with 3 kV breakdown voltage. Both the gate-leakage and drain-leakage current was noticeably stable ( $I_D = \sim 90 \mu\text{A mm}^{-1}$  and  $I_G = \sim 2 \mu\text{A mm}^{-1}$ ) and bellow  $1 \text{ mA mm}^{-1}$  (breakdown limit) up to the tool limit of 3 kV.<sup>33–35</sup> The breakdown voltage was 3 kV (tool limit) for most devices with the first field plate length ( $L_{\text{FP1}}$ ) of  $\leq 2 \mu\text{m}$ . However, transistors with  $L_{\text{FP1}} > 2 \mu\text{m}$  exhibited a tendency to have lower breakdown voltage ( $< 3 \text{ kV}$ ) as shown in Fig. 4(b). A possible reason for this trend is that longer total field plate length causes the electric field under the field plates to become stronger. Thus, it results in a high impact ionization rate and causes early transistor breakdown. The detailed mechanism of breakdown is described and justified with TCAD simulations in one of our earlier

**Fig. 4.** (a) Breakdown response of an MBDS with field plate 1 and 2 length of 1  $\mu\text{m}$  and 1.5  $\mu\text{m}$  respectively. (b) Breakdown voltage variation with field plate dimensions, transistors with smaller first field plate length had higher breakdown voltage.

**Fig. 5.** Standing of our fabricated MBDS with state-of-the-art in breakdown voltage-  $R_{\text{ON}}$  benchmark.

**Fig. 6.** Preliminary dynamic characterization with  $V_{\text{DSQ}} = 40$  V,  $V_{\text{GSQ}} = -12$  V, pulse width = 100  $\mu\text{s}$ .

works.<sup>22)</sup> Figure 5 demonstrates the promising stand of our fabricated MBDS' in the breakdown voltage—on-resistance benchmark compared to the state-of-the-art MBDS'. The reasonable stability of the leakage current and the superior stand in the breakdown voltage—on-resistance benchmark of our fabricated transistors makes them an attractive choice for potential 1700 V class or 1200 V class applications. However, the breakdown field ( $\sim 75 \text{ V } \mu\text{m}^{-1}$ ) is still much lower than the theoretical critical field ( $330 \text{ V } \mu\text{m}^{-1}$ ) of GaN. The critical field or breakdown voltage of the transistors may further be increased by optimizing the field plate number and

geometry. We are currently working on this optimization and our future work is expected to publish the relevant studies.

Pulsed *IV* measurements with 40 V off-state switching voltage (limited by tool capacity) was performed, the dynamic  $R_{\text{ON}}$  was  $<10\%$  higher than DC  $R_{\text{ON}}$  at  $V_{\text{DS}} = 1$  V (Fig. 6) with 100  $\mu\text{s}$  pulse width. The amount of current collapse was less than 10% compared to DC measurements. In these measurements the second gate ( $G_2$ ) and “drain” ( $S_2$ ) were shorted together. Even though the preliminary switching results look promising, the off-state switching voltage should be close to the voltage rating of the application class ( $\sim 1200$  V or  $\sim 1700$  V) with  $<10 \mu\text{s}$  pulse width for practical implementations. The 40 V applied bias in this study was due to the tool limit. Our future studies will focus on high voltage switching tests with appropriate tool setup.

Monolithic bidirectional GaN HEMTs with greater than 3 kV (limited by tool capacity) breakdown voltage was demonstrated for the first time for potential applications in 1200 V class or 1700 V class power converters. The breakdown voltage was optimized by utilizing two field plates with varying lengths. The first field plate lengths of  $\leq 2 \mu\text{m}$  resulted in higher breakdown voltage, the possible physics behind this was explained. For 3 kV breakdown voltage the on-resistance was low,  $\sim 20 \Omega \text{ mm}$  ( $11 \text{ m}\Omega \cdot \text{cm}^2$ ). In breakdown voltage—on resistance benchmark against the state-of-the-art monolithic bidirectional GaN HEMTs, this work shows significant progress.

**Acknowledgments** We gratefully acknowledge the support of NSF ASCENT (award number ECCS 2328137).

**ORCID iDs** Md Tahmidul Alam  <https://orcid.org/0009-0008-6556-839X>

- 1) I. Capellán-Pérez, M. Mediavilla, C. de Castro, Ó. Carpintero, and L. J. Miguel, *Energy* **77**, 641 (2014).

- 2) N. Abas, A. Kalair, and N. Khan, *Futures* **69**, 31 (2015).

- 3) S. Shafiee and E. Topal, *Energy Policy* **37**, 181 (2009).

- 4) S. Nagai, Y. Yamada, N. Negoro, H. Handa, Y. Kudoh, H. Ueno, M. Ishida, N. Otuska, and D. Ueda, 2014 IEEE Int. Solid-State Circuits Conf. Digest of Technical Papers (ISSCC) (San Francisco, CA, USA), 2014 p. 494.

- 5) C. Kuring, J. Lenth, J. Boecker, T. Kahl, and S. Dieckerhoff, PCIM Europe 2018; Int. Exhibition and Conf. for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management 2018, (VDE Nuremberg, Germany) p. 1978-3-8007-4646-0.

- 6) M. Guacci, M. Tatic, D. Bortis, J. W. Kolar, Y. Kinoshita, and H. Ishida, 2019 IEEE 10th Int. Symp. on Power Electronics for Distributed Generation Systems (PEDG)2019 (Xi'an, China), p. 674.

- 7) J. Zhu, Q. Zeng, X. Yang, M. Zhou, and T. Wei, *IEEE Trans. Power Electron.* **37**, 11486 (2022).

8) Z. J. Shen, Z. Miao, A. M. Roshandeh, P. Moens, H. Devleeschouwer, A. Salih, B. Padmanabhan, and W. Jeon, 2016 28th Int. Symp. on Power Semiconductor Devices and ICs (ISPSD) 2016 (Prague, Czech Republic), p. 79.

9) J. Waldron and T. P. Chow, 2013 25th Int. Symp. on Power Semiconductor Devices & IC's (ISPSD) 2013 (Kanazawa, Japan), p. 213.

10) H. Wang et al., *IEEE Electron Device Lett.* **42**, 1264 (2021).

11) M. Saadeh, M. S. Chinthavali, B. Ozpineci, and H. A. Mantooh, IEEE Energy Conversion Congress and Exposition2013 (Denver, CO, USA), p. 2892.

12) T. Wei, Z. Yu, Z. Chen, X. Zhang, W. Wen, Y. Huang, and R. Zeng, 2018 IEEE Applied Power Electronics Conf. and Exposition (APEC) 2018 (San Antonio, TX, USA), p. 141.

13) J. Huber and J. W. Kolar, *IEEE Power Electron. Mag.* **10**, 28 (2023).

14) T. Morita, M. Yanagihara, H. Ishida, M. Hikita, K. Kaibara, H. Matsuo, Y. Uemoto, T. Ueda, T. Tanaka, and D. Ueda, 2007 IEEE Int. Electron Devices Meeting2007 (Washington, DC, USA), p. 865.

15) U. Raheja, G. Gohil, K. Han, S. Acharya, B. J. Baliga, S. Bhattacharya, M. Labreque, P. Smith, and R. Lal, 2017 IEEE Energy Conversion Congress and Exposition (ECCE)2017 (Cincinnati, OH, USA), p. 1967.

16) G. Gupta, C. Neufeld, D. Bisi, Y. Huang, B. Cruse, P. Smith, R. Lal, and U. Mishra, 2023 IEEE 10th Workshop on Wide Bandgap Power Devices & Applications (WiPDA)2023 (Charlotte, NC, USA), p. 1.

17) S. Musumeci, M. Panizza, F. Stella, and F. Perraud, 2020 IEEE 29th Int. Symp. on Industrial Electronics (ISIE)2020 (Delft, Netherlands), p. 1045.

18) C. Kuring, O. Hilt, J. Böcker, M. Wolf, S. Dieckerhoff, and J. Würfl, 2018 IEEE Energy Conversion Congress and Exposition (ECCE) 2018 (Portland, OR, USA), p. 876.

19) M. Wolf, O. Hilt, and J. Würfl, *IEEE Trans. Electron Devices* **65**, 3878 (2018).

20) N. Nain, S. Walser, J. Huber, K. K. Leong, and J. W. Kolar, *IEEE Trans. Power Electron.* **37**, 10091 (2022).

21) C. Kuring, N. Wieczorek, O. Hilt, M. Wolf, J. Böcker, J. Würfl, and S. Dieckerhoff, 2019 IEEE Energy Conversion Congress and Exposition (ECCE)2019 (Baltimore, MD, USA), p. 824.

22) M. T. Alam, J. Chen, R. Bai, S. S. Pasayat, and C. Gupta, *IEEE Trans. Electron Devices* **71** [1] 733 - 738 (10 November 2023).

23) G. Greco, F. Iucolano, and F. Roccaforte, *Mater. Sci. Semicond. Process.* **78**, 96 (2018).

24) F. Roccaforte, G. Greco, P. Fiorenza, and F. Iucolano, *Materials* **12**, 1599 (2019).

25) X. Huang, Z. Liu, Q. Li, and F. C. Lee, *IEEE Trans. Power Electron.* **29**, 2453 (2014).

26) T. Hirose, M. Imai, K. Joshin, K. Watanabe, T. Ogino, Y. Miyazaki, K. Shono, T. Hosoda, and Y. Asai, 2014 IEEE Applied Power Electronics Conf. and Exposition—APEC 2014 p. 174 Fort Worth, TX, USA .

27) D. Bisi, B. Cruse, P. Zuk, P. Parikh, U. Mishra, T. Hosoda, M. Kamiyama, and M. Kanamura, 2022 IEEE Int. Reliability Physics Symp. (IRPS) 2022 (Fort Worth, TX, USA), p. 1.

28) D. Bisi et al., IEEE Applied Power Electronics Conf. and Exposition (APEC) 2022 p. 181 Houston, TX, USA .

29) G. Gupta et al., IEEE 34th Int. Symp. on Power Semiconductor Devices and ICs (ISPSD)2022 (Vancouver, BC, Canada), p. 349.

30) G. Gupta, M. Kanamura, B. Swenson, C. Neufeld, T. Hosoda, P. Parikh, R. Lal, and U. Mishra, 2022 Int. Electron Devices Meeting (IEDM) 2022 (Houston, TX, USA), p. 35.2.1.

31) X. Li et al., *IEEE Electron Device Lett.* **45**, 84 (2024).

32) T. P. Chuang, N. Tumilty, C. H. Yu, and R. H. Horng, *Chin. J. Phys.* **90**, 1117 (2024).

33) J-G. Kim, C. Cho, E. Kim, J. S. Hwang, K-H. Park, and J-H. Lee, *IEEE Trans. Electron Devices* **68**, 1513 (2021).

34) C. Yu et al., *ECS J. Solid State Sci. Technol.* **11**, 085009 (2022).

35) B. Duan, L. Yang, Y. Wang, and Y. Yang, *IEEE Trans. Electron Devices* **68**, 2240 (2021).