Received 7 November 2024; accepted 24 November 2024. Date of publication 27 November 2024; date of current version 9 January 2025.

The review of this article was arranged by Editor P.-W. Li.

Digital Object Identifier 10.1109/JEDS.2024.3506922

# Characterization of Silicon Carbide Low-Voltage n/p-Channel MOSFETs at High Temperatures

HUI WANG<sup>1</sup>, PENGYU LAI<sup>1</sup>, AFFAN ABBASI<sup>1</sup>, MD MAKSDUL HOSSAIN<sup>1</sup>, ASIF FARUQUE,

H. ALAN MANTOOT<sup>1</sup> (Fellow, IEEE), AND ZHONG CHEN<sup>1</sup> (Member, IEEE)

Department of Electrical Engineering and Computer Science, University of Arkansas, Fayetteville, AR 72701, USA

CORRESPONDING AUTHOR: Z. CHEN (e-mail: chenz@uark.edu)

This work was supported in part by the National Science Foundation under Award 2131972, and in part by the Army Research Laboratory under Contract W911NF2120231.

**ABSTRACT** SiC-based n-channel and p-channel MOSFETs fabricated by Fraunhofer IISB SiC CMOS technology are characterized from room temperature up to 300°C. The behaviors of these low voltage devices including the short-channel effect (SCE), p-type ohmic contact with high resistivity, and the low channel mobility due to the SiC/SiO<sub>2</sub> interface are presented. A thorough analysis is performed to understand the cause of low channel mobility, with TCAD simulations specifically on p-channel MOSFET, providing an insight into the impact of channel length, interface traps, and contact resistivity on device performance. The analysis in this paper is important in the comprehension of the low-voltage SiC MOSFETs so as to achieve balanced n-channel and p-channel MOSFETs and lead to the monolithic integration of SiC ICs with SiC power devices.

**INDEX TERMS** Silicon carbide, CMOS, high temperature, TCAD, channel mobility, SiC/SiO<sub>2</sub> interface.

## I. INTRODUCTION

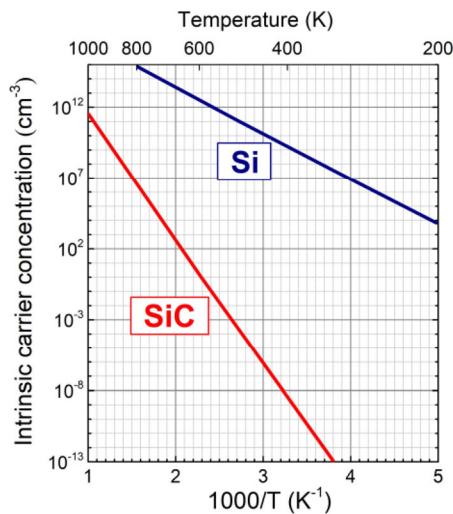

Silicon carbide (SiC) is a candidate material of great interests due to its wide bandgap and ability to grow the native oxide as silicon (Si) [1], [2]. SiC offers several advantages over Si, including high breakdown electric field, high saturation velocity, etc., which are particularly beneficial for applications of high-voltage, fast-switching, low-loss, etc. [3]. Its extremely low intrinsic carrier concentration of SiC as shown in Fig. 1 enables high-temperature operation of SiC devices [4], [5]. Since 1995, SiC-based electronics for high-temperature applications have received extensive attention [6]. As the market of SiC power electronics grow rapidly, the end system using Si-based devices or chips are often constrained by parasitic effects [7]. Si ICs are also inadequate for applications in sectors like aircraft, automotive and aerospace systems where operating temperatures exceed 200°C [8], [9], [10]. Consequently, there is a strong desire to develop a SiC CMOS technology to fully integrate essential functions - such as gate driving, sensing, amplifying, and controlling - with SiC-based power electronics to minimize losses, reduce size and cost, and enable operation in harsher environments [11]. Despite these needs, the monolithic integration of the

control circuitry in SiC or other wide bandgap materials has proven challenging. Among wide bandgap materials, although both SiC and gallium nitride (GaN) have long been proposed for high-temperature applications, SiC is the only material where complementary MOSFET process is not merely a tantalizing possibility, but already an established process platform with some digital circuit demonstrations and extreme-condition reliability studies [12]. Technological advances in SiC, including interconnect metallization and device packaging [13], have enabled SiC ICs to operate at temperatures beyond 450°C. While the development of SiC ICs traces to early 90s led by Cree [14] and Purdue [15], we still lack matured SiC CMOS processes, and the accessible in-house SiC CMOS fabrication processes are scarce.

Among the reported SiC CMOS processes, Raytheon U.K. has set the benchmark for SiC CMOS technology with its 1.2-μm HiTSiC process, achieving a high manufacturing readiness level and enabling the monolithic integration of n-channel and p-channel MOSFETs (nMOS/pMOS) with the capability to operate at 300°C and above [11], [13]. However, it lacks the evaluation of the SiC/SiO<sub>2</sub> interface traps which has always been a major reliability concern for SiC MOSFETs. Ekström from KTH demonstrates a

FIGURE 1. Temperature dependence of the intrinsic carrier concentration for SiC and Si [4].

TABLE 1. Properties of 4H-SiC as compared to Si.

| Parameters                                       | Si   | 4H-SiC              |

|--------------------------------------------------|------|---------------------|

| $E_g(\text{eV})@300\text{K}$                     | 1.12 | 3.26                |

| $E_c(\text{MV/cm})$                              | 0.3  | 2.5-3               |

| $\mu_n(\text{cm}^2/\text{V}\cdot\text{s})^{*1}$  | 1350 | 1020                |

| $\mu_n(\text{cm}^2/\text{V}\cdot\text{s})^{*2}$  |      | 1150                |

| $\mu_p(\text{cm}^2/\text{V}\cdot\text{s})$       | 450  | 120                 |

| $\mu_{le,n}(\text{cm}^2/\text{V}\cdot\text{s})$  | 500  | <sup>*3</sup> 15-35 |

| $\mu_{le,p}(\text{cm}^2/\text{V}\cdot\text{s})$  | 100  | <sup>*3</sup> 7-10  |

| $\sigma_{\text{therm}}(\text{W/m}\cdot\text{K})$ | 150  | 490                 |

<sup>\*1</sup>perpendicular to c-axis, <sup>\*2</sup>parallel to c-axis.

<sup>\*3</sup>values represent the results of conventional oxidation followed by nitrogen annealing.

preliminary SiC CMOS process with devices such as MOSFETs, capacitors as well as ICs, inverters and ring oscillators that operate at 200°C [16]. Recessed channel MOSFETs without using ion implantation are designed for the demonstration. The main benefit of recessed channel design is the immunity to short-channel effect (SCE). Nevertheless, the benefit is not manifested since the designed devices have long channel length. Since 2017, Hitachi has focused on developing radiation-hardened SiC technology for nuclear plant applications, particularly after the Fukushima disaster, and has demonstrated some SiC devices and ICs [17], [18]. The n-channel and p-channel MOSFETs have unsatisfactory mobilities with unbalanced threshold voltages. MOSFETs are fundamental to modern microelectronics due to advantages such as high input impedance, simple gate-driven operation, low static power consumption due to the complementary pair structure, and high device density [19], [20]. They hold substantial promise for the next generation of high-temperature, high-frequency and high-voltage applications [19]. Yet, the performance of SiC MOSFETs is hampered by the low channel mobility largely due to the high interface traps [20], [21], [22]. TABLE 1 gives a comparison of the material with the parameters which

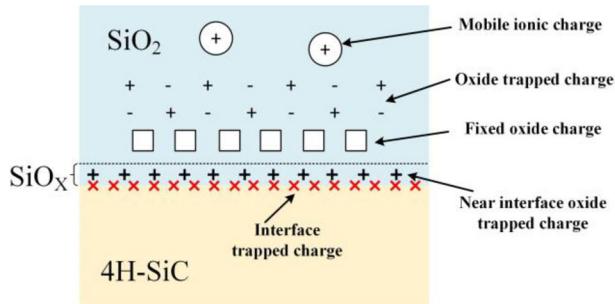

FIGURE 2. Allocation of five types of charges associated with SiC-SiO<sub>2</sub> interface system [24].

are important in MOSFET device design and evaluation. Currently, typical 4H-SiC n-channel MOSFET inversion channel mobility is 15 – 35 cm<sup>2</sup>/V.s, while p-channel is 7 – 10 cm<sup>2</sup>/V.s with nitridation-treated oxides [20], [23], which is far from the channel mobility of Si counterparts. It is noted however that the mobility of pMOS is lower than nMOS by a factor of 2 – 3, which presents a unique balance level compared to Si. The low channel mobility of SiC device is primarily caused by the structural imperfection of the dielectric and the interface defects. The exact causes of trap formation have not been fully understood, but the presence of electrically active traps in the oxide and at the interface have impacts on the device's electrical properties. As shown in Fig. 2, there are mainly five types of charges associated with the SiC-SiO<sub>2</sub> system in general: mobile ionic charges, oxide trapped charges, fixed oxide charges, near interface oxide trapped charges (NIOT) and interface trapped charges [24]. The interface trapped charges are mainly responsible for limiting the channel mobility, while the fixed oxide charges and oxide trapped charges, NIOTs are responsible for the instability of the threshold voltage [25].

Recently, Fraunhofer IISB in Erlangen, Germany, developed a promising SiC CMOS technology, reporting an inverter using the pMOS [26] operating with a 5 V power supply over the temperature range of 25°C to 400°C and op-amp with both nMOS and pMOS [27] measured up to 300°C. Although SiC low-voltage CMOS devices have been developed, their performance across varying temperatures remains under-explored, especially the pMOS. Furthermore, the threshold voltage shift, contact resistance, especially the channel mobility at high temperature needs to be analyzed to serve a purpose to optimize the process.

In this paper, we present the characterizations of 4H-SiC MOSFETs fabricated with the optimized Fraunhofer SiC CMOS process. Both n-channel and p-channel MOSFETs with various channel lengths are evaluated regarding the short-channel effect (SCE), while the scattering effects on channel mobility at high temperature are analyzed. Technology computer-aided design (TCAD) simulations with consideration of effects of numerous physical mechanisms have been conducted with the p-channel MOSFET structure, which gives insights into the device operation.

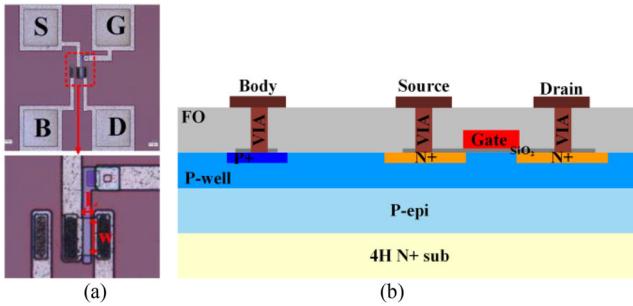

FIGURE 3. (a) Top view of a SiC nMOS layout. (b) Technology cross section of SiC CMOS process for nMOS structure.

## II. EXPERIMENT RESULTS

The structures were fabricated using an optimized SiC CMOS process in collaboration with Fraunhofer IISB. This process has a minimum linewidth of  $1 \mu\text{m}$  with twin wells, a single poly, and a single metal layer (1P1M). The devices are formed in a lightly doped P-epi layer (i.e.,  $1\text{e}15 \text{ cm}^{-3}$ ) on top of a 4H-SiC  $\text{N}^+$  substrate. A series of aluminum (Al) implants are used for the P-well and  $\text{P}^+$  regions while nitrogen (N) implants are applied for N-well and  $\text{N}^+$  regions. No channel counter doping was employed in this process. A 50 nm gate oxide was grown by dry oxidation at  $1300^\circ\text{C}$  and followed by annealing in NO atmosphere at the same temperature. The dielectric layer and doping profiles are designed to allow 20 V operation at temperature beyond  $300^\circ\text{C}$ . P-type gate polysilicon is used for both nMOS and pMOS to help balance the threshold voltage [28]. TABLE 2 lists the parameters of the fabricated devices including the gate oxide thickness, the doping concentrations and junction depth which were extracted from the secondary ion mass spectrometry (SIMS) analysis. It is noteworthy that the ionization energy of Al is significantly higher than that of N; consequently, the electrical activation of Al could be substantially lower than its doping concentration unlike N [29]. This incomplete ionization of dopants is an essential factor to consider in device simulation to ensure accuracy in predicting electrical behavior.

### A. N/P-CHANNEL MOSFETs AT ROOM TEMPERATURE

Fig. 3 shows the nMOS structure used for the characterization with varying channel width ( $W$ ) and channel length ( $L$ ).  $I_D-V_G$ ,  $I_D-V_D$ , and transconductance  $g_m$  of both nMOS and pMOS were obtained at room temperature.

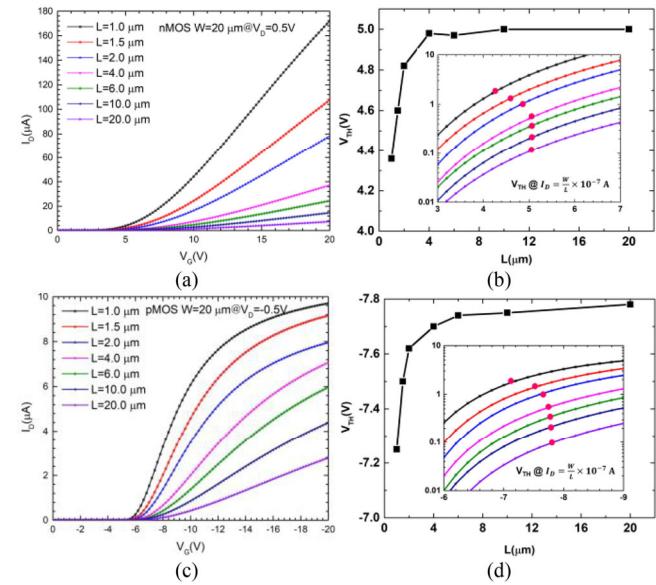

$I_D-V_G$  of n-channel MOSFETs were measured by sweeping  $V_G$  from 0 to 20 V at drain bias  $V_D = 0.5 \text{ V}$ , while  $V_G$  from 0 to  $-20 \text{ V}$  at drain bias  $V_D = -0.5 \text{ V}$  was applied for p-channel MOSFETs. The curves with varying  $L$  are given in Fig. 4(a) and (c), respectively. The threshold voltage  $V_{TH}$  is extracted by the constant current method (CCM) [30] at predefined  $I_D = W/L \times 10^{-1} \text{ A}$ .  $V_{TH}$  extraction results in Fig. 4(b) and (d) indicate the (SCE) occurs with  $L$  less than  $2 \mu\text{m}$  for both nMOS and pMOS. It can be seen in Fig. 4(b) that  $V_{TH}$  for the long-channel nMOS is about 5.0 V while

TABLE 2. Device parameters.

| Parameters                  | Value                         |

|-----------------------------|-------------------------------|

| $t_{ox}$                    | 50 (nm)                       |

| $x_j$                       | 0.3 ( $\mu\text{m}$ )         |

| N+ doping concentration     | $5\text{e}19 \text{ cm}^{-3}$ |

| P+ doping concentration     | $3\text{e}19 \text{ cm}^{-3}$ |

| N-well doping concentration | $2\text{e}16 \text{ cm}^{-3}$ |

| P-well doping concentration | $1\text{e}17 \text{ cm}^{-3}$ |

FIGURE 4. (a)  $I_D-V_G$  of n-channel MOSFETs with varying  $L$  ( $W = 20 \mu\text{m}$ ). (b)  $V_{TH}$  extraction of n-channel MOSFETs. (c)  $I_D-V_G$  of p-channel MOSFETs with varying  $L$  ( $W = 20 \mu\text{m}$ ). (d)  $V_{TH}$  extraction of p-channel MOSFETs.

\* Sign of  $I_D$  of pMOS is transferred to be positive for the convenience of data process especially for the log-scale plot.

for short-channel device with  $L = 1 \mu\text{m}$ ,  $V_{TH} = 4.35 \text{ V}$ . Fig. 4(d) shows  $V_{TH} \approx -7.7 \text{ V}$  and  $-7.25 \text{ V}$  for the long-channel and 1  $\mu\text{m}$  short-channel pMOS, respectively.

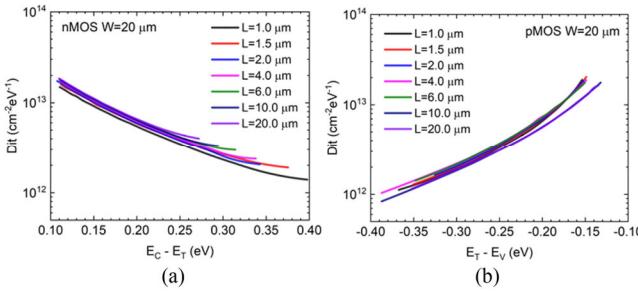

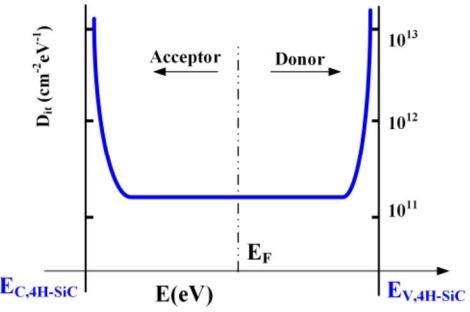

The density of interface trap  $D_{it}$  extraction from the subthreshold characteristics [31] are presented in Fig. 5. The  $D_{it}$  increases exponentially near the conduction band edge for nMOS and valance band for pMOS, which exceeds  $10^{13} \text{ cm}^{-2}\text{eV}^{-1}$ . It drops to  $10^{12} \text{ cm}^{-2}\text{eV}^{-1}$  or below towards the mid-gap. The level of  $D_{it}$  is comparable to that reported in [32] with similar post-oxidation annealing condition.

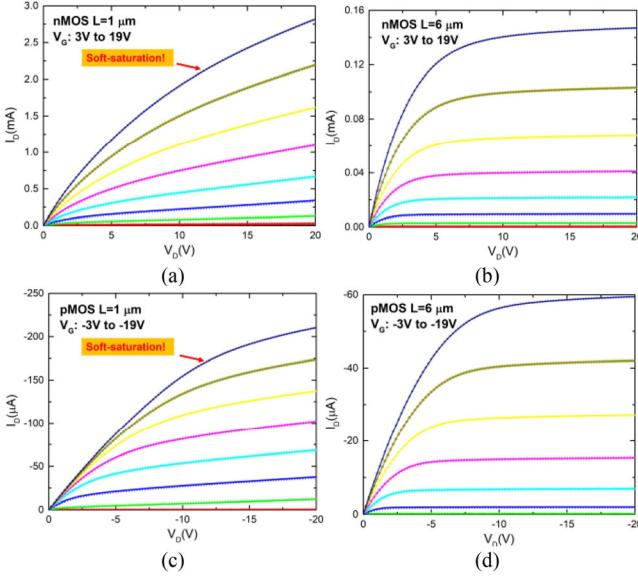

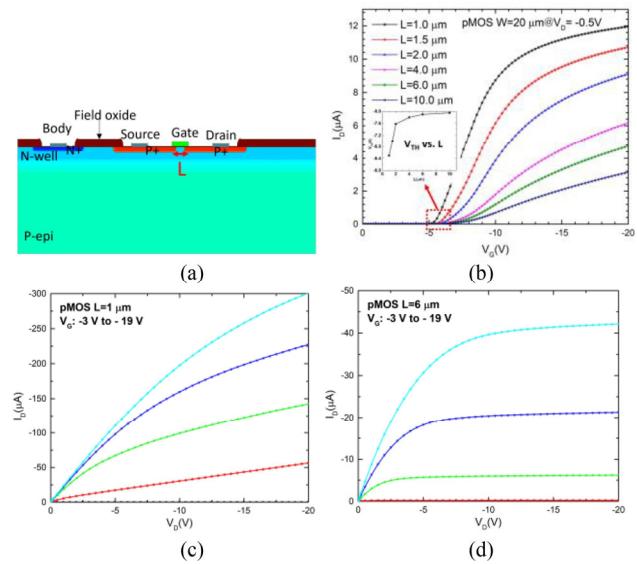

Fig. 6 shows the  $I_D-V_D$  curves with  $L = 1 \mu\text{m}$  and  $L = 6 \mu\text{m}$  for both nMOS and pMOS. Devices were characterized by sweeping  $V_D$  from 0 to 20 V with a biased  $V_G$  from 3 V to 19 V with a 2 V step for nMOS, and  $V_D$  from 0 to  $-20 \text{ V}$  with a biased  $V_G$  from  $-3 \text{ V}$  to  $-19 \text{ V}$  with a  $-2 \text{ V}$  step for pMOS. The SCE can be further confirmed by the soft-saturation characteristics at the large drain bias region. It can be explained by the drain-induced barrier lowering (DIBL) with short channel length, which causes a reduction of  $V_{TH}$ .

FIGURE 5.  $D_{it}$  extraction of (a) N-channel MOSFET; (b) P-channel MOSFETs.

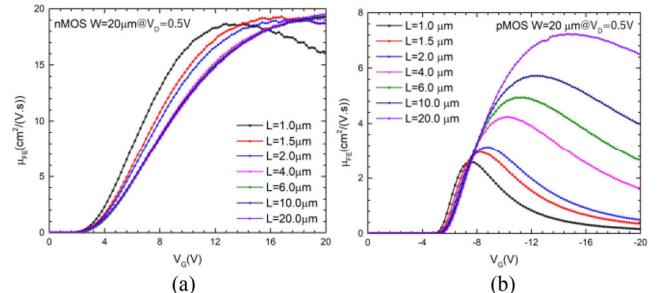

FIGURE 7.  $\mu_{FE}$  curves extracted from  $gm$  data: with (a) n-channel MOSFETs, (b) p-channel MOSFETs.

FIGURE 6.  $I_D$ - $V_D$  of 20  $\mu$ m width: n-channel MOSFETs with (a)  $L = 1 \mu$ m and (b)  $L = 6 \mu$ m; p-channel MOSFETs with (c)  $L = 1 \mu$ m and (d)  $L = 6 \mu$ m.

There are several criteria to determine the boundary between “short-channel” and “long-channel” [33], [34], which is referred in the device scaling study to avoid potential instability. An empirical relation can be applied to estimate the minimum channel length  $L_{min}$  of SiC MOSFET to avoid the short-channel behavior [2], [35]. The  $L_{min}$  is described as

$$L_{min} = A\gamma^B \quad (1)$$

where  $A$  is a proportionality factor and 0.4 is typically adopted,  $B$  is 1/4 in for SiC [2].  $\gamma$  is expressed as

$$\gamma = x_j t_{ox} (w_D + w_S)^2 \times 10^4 \quad (2)$$

where  $x_j$  is the junction depth in the drain and source regions,  $t_{ox}$  is the oxide thickness, and  $w_D$  and  $w_S$  are the depletion layer widths at the drain and source ends, respectively. The depletion widths  $w_D$  and  $w_S$  is given by the one-dimensional abrupt junction formulation

$$w_{D,S} = \frac{2\epsilon_{SiC} V_{bi} + V_{D,S}}{qN_{A(D)}} \quad (3)$$

where  $\epsilon_{SiC}$  is the permittivity of SiC,  $V_{bi}$  is the build-in potential in SiC,  $V_D$  and  $V_S$  in the drain and source voltages,  $q$  is the elementary charge, and  $N_A$  and  $N_D$  are the acceptor and donor concentrations, respectively. Referring to the parameters listed in TABLE 2, the  $L_{min}$  estimation of the fabricated devices is 0.9  $\mu$ m for nMOS and 1.3  $\mu$ m for pMOS.

Field-effect mobility  $\mu_{FE}$  is extracted from the transconductance  $g_m$  by the following equation

$$\mu_{FE} = \frac{1}{WC_{ox}V_D} g_m \quad (4)$$

where  $C_{ox}$  is the oxide capacitance. The mobility curves are presented in Fig. 7. The peak value of nMOS  $\mu_{FE}$  is around 19  $\text{cm}^2/(\text{V} \cdot \text{s})$ , while the peak value of pMOS  $\mu_{FE}$  ranges from 2.5 to 7.5  $\text{cm}^2/(\text{V} \cdot \text{s})$ . As the channel length  $L$  decreases, the peak  $\mu_{FE}$  is getting smaller as it is more obvious in p-channel MOSFETs. This is because p-type (P+) ohmic contact has much higher resistance than n-type (N+) leading to the increasing series contact resistance ( $R_C$ ) effect [36], that the increasing  $R_C/R_{total}$  ratio leads to a decrease in effective  $V_D$  and  $V_G$ . More details of contact resistance results with the characterization of the transfer length method (TLM) are presented in the next section.

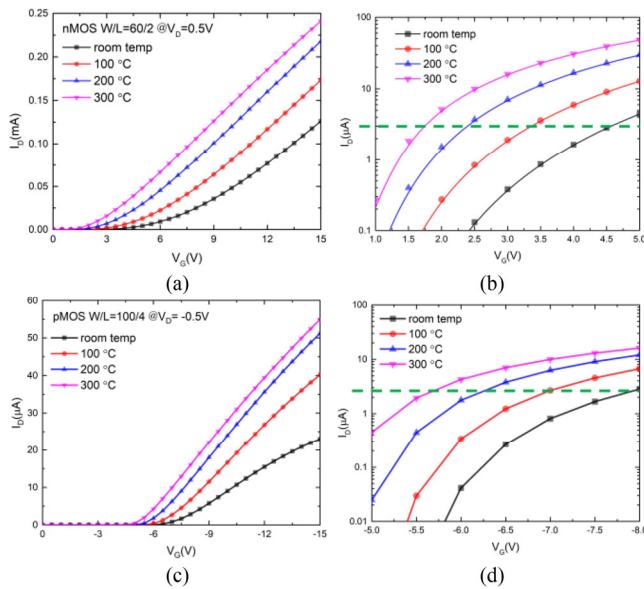

## B. N/P-CHANNEL MOSFET AT HIGH TEMPERATURE

An nMOS ( $W = 60 \mu$ m,  $L = 2 \mu$ m) and a pMOS ( $W = 100 \mu$ m,  $L = 4 \mu$ m) were characterized from room-temperature up to 300°C. Fig. 8 shows  $I_D$ - $V_G$  curves with varying temperatures. It is observed from Fig. 8(a) and (c) that the drain driving current  $I_D$  of both nMOS and pMOS increases with higher temperature. Meanwhile, zoom-in regions near the turn-on point in Fig. 8(b) and (d) show a monolithic reduction in  $V_{TH}$  with elevated temperatures. The dashed green lines are determined by the CCM to extract the  $V_{TH}$ . The increasing  $I_D$  at elevated temperature is primarily due to the decrease of contact resistance along with the reduction of  $V_{TH}$  causing gate overdrive voltage, while the  $V_{TH}$  reduction is due to the increase of intrinsic carrier concentration and lower interface trapped charges at higher temperature, and the channel mobility at low  $V_G$  increases.

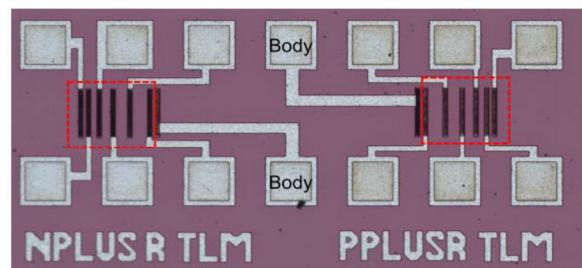

Further DC I-V characterization has been performed on TLM structures to extract the contact resistance. Especially

FIGURE 8. (a)  $I_D$ – $V_G$  of n-channel MOSFET with  $W/L = 60 \mu\text{m}/2 \mu\text{m}$ . (b)  $\log(I_D)$ – $V_G$  of (a) to compare the  $V_{TH}$  within the  $V_G$  range of  $0.5 \sim 3.5$  V. (c)  $I_D$ – $V_G$  of p-channel MOSFET with  $W/L = 100 \mu\text{m}/4 \mu\text{m}$ . (d)  $\log(I_D)$ – $V_G$  of (c) to compare the  $V_{TH}$  within the  $V_G$  range of  $-4 \sim -6.5$  V.

\* Sign of  $I_D$  of pMOS is transferred to be positive for the convenience of data process especially for the log-scale plot.

for p-channel MOSFET, the huge difference among the mobilities in Fig. 7(b) implies  $\text{P}_+$  ohmic contact has much higher resistance than  $\text{N}_+$ . Fig. 9(a) gives the top view of the  $\text{N}_+/\text{P}_+$  TLM with  $100 \mu\text{m}$  width. The total resistance  $R$  versus the resistor length  $L$  is extracted and the linear curving fitting results are shown in Fig. 9(b) and (c). TABLE 3 gives the extraction summary of  $\text{N}_+$  and  $\text{P}_+$  source/drain sheet resistance and  $\text{N}_+/\text{P}_+$  contact resistivity. As expected, the resistances of  $\text{P}_+$  and  $\text{N}_+$  regions decrease with temperature increasing which is related with the ionization at high temperature. It is more obvious when it comes to  $\text{Al}$  since the activation rate of  $\text{Al}$  is not high enough as compared to  $\text{N}$ . As temperature increases, the sheet resistance of  $\text{P}_+$  region decreases more significantly as it is shown in the table that the sheet resistance drops from  $31.6 \text{ kQ}/\text{D}$  at room temperature to  $6.7 \text{ kQ}/\text{D}$  at  $200^\circ\text{C}$ . Moreover, the extracted contact resistivity of  $\text{P}_+$  shows at least three orders higher than  $\text{N}_+$  contact, and it contributes a considerable portion to the on-resistance of the MOSFETs. The higher Schottky barrier height of  $\text{Al}$  than  $\text{N}$  along with incomplete ionization of  $\text{Al}$  significantly hinders the formation of ohmic contacts due to a lower free carrier concentration, which leads to a higher Schottky barrier height at the metal-semiconductor interface. For example, the extracted specific on-resistance ( $R_{ON,sp}$ ) of nMOS at  $|V_G| = 19 \text{ V}$ ,  $|V_D| = 1 \text{ V}$  in Fig. 6(b) and pMOS in Fig. 6(d) are  $0.024 \text{ Q} \cdot \text{cm}^2$  and  $0.15 \text{ Q} \cdot \text{cm}^2$ , respectively. The  $\text{P}_+$  source and drain contact resistivities are approximately 40% of the total  $R_{ON,sp}$ . Though both  $\text{P}_+$  and  $\text{N}_+$  contacts are ohmic which are formed on heavily doped regions, the higher resistivity of  $\text{P}_+$  contacts over

FIGURE 9. (a) Top view of  $\text{N}_+$  and  $\text{P}_+$  TLM structures. (b) Resistance versus resistor length of  $\text{N}_+$  TLM at different temperatures. (c) Resistance versus resistor length of  $\text{P}_+$  TLM at different temperatures.

TABLE 3. Extraction results.

| Parameters                                              | Room temperature      | 100°C                 | 200°C                 |

|---------------------------------------------------------|-----------------------|-----------------------|-----------------------|

| $R_S$ of $\text{N}_+$ [ $\Omega/\text{l}$ ]             | 983                   | 884                   | 815                   |

| $R_S$ of $\text{P}_+$ [ $\text{k}\Omega/\text{l}$ ]     | 31.6                  | 12.4                  | 6.7                   |

| $\rho_c$ of $\text{N}_+$ [ $\Omega \cdot \text{cm}^2$ ] | $1.37 \times 10^{-5}$ | $4.83 \times 10^{-6}$ | $3.43 \times 10^{-6}$ |

| $\rho_c$ of $\text{P}_+$ [ $\Omega \cdot \text{cm}^2$ ] | 0.0297                | 0.01                  | $5.69 \times 10^{-3}$ |

$\text{N}_+$  adversely affect the pMOS performance such as driving current capability and field-effect mobility. The existing methods for creating ohmic contacts to n-type SiC are generally deemed adequate for commercial manufacturing. However, the process of forming p-type contacts still remains a significant challenge, posing limitations to the advancement of highly reliable IC technology [37].

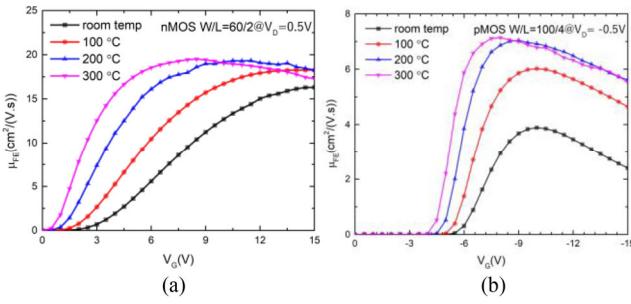

The  $\mu_{FE}$  extraction results of the nMOS and pMOS at high temperature are given in Fig. 10. The peak is shifted to the lower gate electric field as temperature increases, which is consistent with the trend of  $V_{TH}$ , while the peak value increases due ionization and reduction of contact resistance. More analysis of the mobility regarding the scattering mechanisms will be presented in the simulation section.

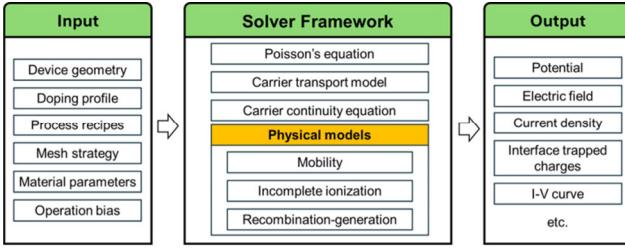

### III. SIMULATIONS AND DISCUSSION

Sentaurus TCAD software from Synopsys was used to perform MOSFET simulation. Structures were created based on the device layout given in Fig. 3. Monte-Carlo ion implantations were adopted to form the N-well, P-well,  $\text{N}_+$  and  $\text{P}_+$  regions. The mesh was made fine near the junctions and surface in order to capture the rapid change in potential and charge concentration and avoid the convergence problem. In the inversion layer, the mesh spacing is kept as low as  $1 \text{ \AA}$  close to the surface while spacing is sufficiently large in

**FIGURE 10.**  $\mu_{FE}$  curves with varying temperature extracted from  $gm$  data: with (a) n-channel MOSFET with  $W = 60 \mu\text{m}$ ,  $L = 2 \mu\text{m}$ , (b) p-channel MOSFET with  $W = 100 \mu\text{m}$ ,  $L = 4 \mu\text{m}$ .

**FIGURE 11.** Framework of TCAD simulator.

regions where there are no abrupt changes in the distribution of charges, electric field and electrostatic potential etc., to improve the simulation speed. Simulations are conducted at room temperature with varying channel dimensions as well as at high temperature up to  $300^\circ\text{C}$ . The framework of simulation including the input, solver, and output is shown in Fig. 11. The key physical models are mobility-related models (scattering mechanism models, fixed charges at the SiC-SiO<sub>2</sub> interface, and interface trap distribution), incomplete ionization, and recombination-generation models (Schockley-Read-Hall (SRH) recombination and Auger recombination model). Among all the models, scattering mechanisms, fixed oxide charge, interface trap distribution are the main models in which the parameters are modified and calibrated according to the characterization results. Simulation on P-channel MOSFET has been conducted. The P-type contact also needs to be calibrated due to the high contact resistance as reported in Fig. 9 compared to N-type that it cannot be neglected. The  $V_{TH}$  estimation of p-channel MOSFET can be obtained by the equations [1]:

$$V_{FB} = \varphi_{Poly} - \varphi_S - \frac{Q_{OX}}{C_{OX}} - \frac{Q_{IT}(\psi_S = 0)}{C_{OX}} \quad (5)$$

$$V_{TH} = \varphi_{Poly} - \varphi_S - \frac{Q_{OX}}{C_{OX}} - \frac{Q_{IT}(\psi_S = 2\psi_F)}{C_{OX}} - 2|\psi_F| - \frac{\sqrt{4\epsilon_{SiC}qN_D|\psi_F|}}{C_{OX}} \quad (6)$$

where  $\varphi_{Poly}$  and  $\varphi_S$  are the work functions of the polysilicon and substrate, respectively.  $\psi_F$  represents the surface potential for inversion.  $Q_{OX}$  is the fixed charges.  $C_{OX}$  is the capacitance of the oxide between the substrate and

**FIGURE 12.** Interface traps density distribution of 4H-SiC.

gate per unit area.  $Q_{IT}(\psi_S = 0)$  is the interface charges at the flat band.  $Q_{IT}(\psi_S = 2\psi_F)$  is the interface charges at the starting point of strong inversion.  $N_D$  is the donor doping concentration of the substrate for the pMOS.  $q$  is the elementary charge, and  $\epsilon_{SiC}$  is the permittivity of silicon carbide. From (5) and (6), the  $V_{TH}$  deviates from the ideal value due to the presence of  $Q_{IT}$  and  $Q_{OX}$ , and the incomplete ionization of donors  $N_D$ . Without considering incomplete ionization, there is an overestimation of  $V_{TH}$  (absolute value). However, the effect is relatively little due to a higher activation rate of nitrogen (>98%). For most SiC processes,  $Q_{OX}$  has a level of  $10^{12} \text{ cm}^{-2}$  [31], which will have more impacts on the switching performance along with interface traps.

The distribution model of the interface trap density for 4H-SiC refers to [39], which has a constant distribution in the midband region and an exponential increase near the edge of the band as shown in Fig. 12. The energy dependent density of trap states is expressed as

$$D_{it}(E) = D_{it,mid} + D_{it,edge} \exp \left( \frac{E - E_C}{\sigma_{it}} \right) \quad (7)$$

$$D_{it}(E) = D_{it,mid} + D_{it,edge} \exp \left( \frac{E_V - E}{\sigma_{it}} \right) \quad (8)$$

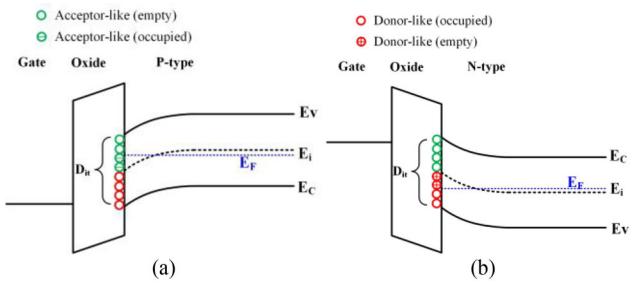

where,  $E_C$  and  $E_V$  are the energy at the conduction band edge and valance band edge respectively,  $D_{it,mid}$  and  $D_{it,edge}$ , represent the densities at the middle and the edge of the bandgap, and  $\sigma_{it}$  defines the curvature of the density of states curve. It is noted that the traps close to the intrinsic Fermi level are the most effective generation-recombination centers. Equation (7) and (8) represent the acceptor-like traps above the midgap and the donor-like traps below the midgap, respectively. They present the different polarities as shown in Fig. 13. The extracted  $D_{it}$  in Fig. 5 is only available over a limited energy range from 0.1eV to 0.4eV. We extrapolate the full bandgap distribution by fitting the extracted  $D_{it}$  to the model as shown in Fig. 12, and we have:  $D_{it,mid} = 2 \times 10^{11} \text{ cm}^{-2} \text{ eV}^{-1}$ ,  $D_{it,edge} = 1 \times 10^{14} \text{ cm}^{-2} \text{ eV}^{-1}$ , and  $\sigma_{it} = 0.067 \text{ eV}$ . The accuracy of the extrapolated  $D_{it}$  distribution is verified and assured by comparing the simulation and characterization results. The results can be improved with further calibration.

**FIGURE 13.** Energy band diagram illustrating interface traps in MOSFETs at inversion for (a) n-channel MOSFET; (b) p-channel MOSFET.

The transfer and output characteristics of p-channel MOSFETs with varying channel geometry were conducted at room temperature. Fig. 14(a) is the cross-section of a p-channel MOSFET created based on the device structure given in Fig. 3. The simulation of pMOS  $I_D-V_G$  was performed by sweeping  $V_G$  from 0 to  $-20$  V at  $V_D = -0.5$  V. Fig. 14(b) shows the simulated curves with varying  $L$  and the  $V_{TH}$  extraction using the same CCM as mentioned above. The  $V_{TH}$  is stabilized at  $-7.8$  V for long-channel device while the short-channel effect is prominent with channel length less than  $2$   $\mu\text{m}$ . With the adopted interface traps distribution model and calibrated contact resistance value from the measurement, both the transfer curves and the extraction results match very well with the characterization results. Fig. 14(c) and (d) show the pMOS  $I_D-V_D$  curves with  $L = 1$   $\mu\text{m}$  and  $L = 6$   $\mu\text{m}$ , respectively. Simulations were conducted by sweeping  $V_D$  from 0 to  $-20$  V with a biased  $V_G$  from  $-3$  V to  $-19$  V with a  $-4$  V step size. The soft-saturation characteristic of the pMOS with  $L = 1$   $\mu\text{m}$  at large drain bias confirms the SCE as illustrated in Fig. 6.

The channel mobility of a pMOS is affected by four scattering mechanisms, which is modelled using Matthiessen's rule as [40]

$$\frac{1}{\mu_{\text{Total}}} = \frac{1}{\mu_B} + \frac{1}{\mu_{SR}} + \frac{1}{\mu_{SP}} + \frac{1}{\mu_C} \quad (9)$$

where  $\mu_B$  represents the bulk mobility [41], [42], [43] that is the ionized impurities scattering in the body,  $\mu_{SR}$  is surface roughness scattering [44],  $\mu_{SP}$  is the surface phonon scattering [45], and  $\mu_C$  is the Coulomb scattering [46], [47] due to the interface traps,. All the four terms in this work are modelled as:

$$\mu_B = \frac{\mu_{\max} \frac{300}{T}^{\alpha} - \mu_{\min}}{1 + \frac{N_D}{N_{REF}} \beta} + \mu_{min} \quad (10)$$

$$\mu_{SR} = \frac{\delta_{SR}}{E^2} \quad (11)$$

$$\mu_{SP} = \frac{A}{E_{\perp}} + \frac{B}{T E_{\perp}^{1/3}} \quad (12)$$

**FIGURE 14.** (a) cross-section of the p-channel MOSFET. (b)  $I_D-V_G$  simulation results with varying  $L$  and the inset of  $V_{TH}$  extraction.  $I_D-V_D$  simulation results of  $20\text{ }\mu\text{m}$  width p-channel MOSFETs with (c)  $L = 1\text{ }\mu\text{m}$  and (d)  $L = 6\text{ }\mu\text{m}$ .

$$\mu_C = \frac{\mu_0 \frac{T}{300}^{\kappa} \frac{N}{1 + \frac{N_{it}}{N_0} \alpha_1 \sigma_0}}{\frac{N_{it}}{N_0} \alpha_2 D(x)f(E_{\perp})} \quad (13)$$

where  $\mu_{max}$  represents the mobility of an undoped sample, while  $\mu_{min}$  is the mobility in the highly doped material,  $N_{REF}$  is the doping concentration at which the mobility is halfway between  $\mu_{max}$  and  $\mu_{min}$ ,  $N_D$  is the donor impurity concentration,  $E_{\perp}$  is the perpendicular electric field,  $c$  is the concentration of the holes near the interface,  $N_{it}$  is the density of the interface traps by integrating the function  $D_{it}(E_{\perp})$ ,  $f(E_{\perp})$  is the probability function for finding charged traps at  $E_{\perp}$ ,  $D(x)$  is a factor of distance from the surface where  $x$  is the distance from the surface,  $\alpha$ ,  $\beta$ ,  $A$ ,  $B$ ,  $\mu_0$ ,  $\alpha_1$ ,  $\alpha_2$ ,  $\kappa$ ,  $N_0$ , and  $\sigma$  are the fitting parameters. The functions  $D(x)$  and  $f(E_{\perp})$  are given by

$$D(x) = e^{-\frac{x}{l_{crit}}} \quad (14)$$

$$f(E_{\perp}) = 1 - e^{-\frac{E_{\perp}}{E_0} \tau} \quad (15)$$

where,  $\tau$ ,  $l_{crit}$  and  $E_0$  are the fitting parameters.

$\mu_{SR}$  is a proportionality constant that accounts for the combined effects of various parameters including the roughness correlation length, oxide permittivity and the wave vector at the Fermi surface. Therefore, surface roughness scattering is highly dependent on the quality of the interface, which varies from process to process. From the equation (11) that surface roughness becomes dominant to affect the channel mobility at the high-field region because of an index of 2, while surface phonon and Coulomb scatterings are dominant in low electric field. The values of the parameters involved in our simulation of scatterings are listed in TABLE 4.

TABLE 4. Parameters for 4H-SiC mobility model.

| Eq.  | Parameters    | Unit                                                                 | Value                 |

|------|---------------|----------------------------------------------------------------------|-----------------------|

| (10) | $\mu_{max}$   | $\text{cm}^2/(\text{V}\cdot\text{s})$                                | 125                   |

|      | $\mu_{min}$   | $\text{cm}^2/(\text{V}\cdot\text{s})$                                | 40                    |

|      | $N_{REF}$     | $\text{cm}^{-3}$                                                     | $2.23 \times 10^{17}$ |

|      | $\alpha$      |                                                                      | -2.4                  |

|      | $\beta$       |                                                                      | 0.76                  |

| (11) | $\delta_{SR}$ | $\text{V}\cdot\text{s}$                                              | $1 \times 10^{13}$    |

| (12) | $A$           | $\text{cm}/\text{s}$                                                 | $8.1 \times 10^5$     |

|      | $B$           | $(\text{V}/\text{cm})^{2/3} \cdot \text{K} \cdot \text{cm}/\text{s}$ | $8.36 \times 10^3$    |

| (13) | $\mu_0$       | $\text{cm}^2/(\text{V}\cdot\text{s})$                                | 40                    |

|      | $\alpha_1$    |                                                                      | 1.0                   |

|      | $\alpha_2$    |                                                                      | 0.5                   |

|      | $\sigma$      |                                                                      | 1.5                   |

|      | $\kappa$      |                                                                      | 1.0                   |

| (14) | $l_{crit}$    | cm                                                                   | $1 \times 10^{-6}$    |

| (15) | $E_0$         | $\text{V}/\text{cm}$                                                 | $2 \times 10^5$       |

|      | $\tau$        |                                                                      | 2.0                   |

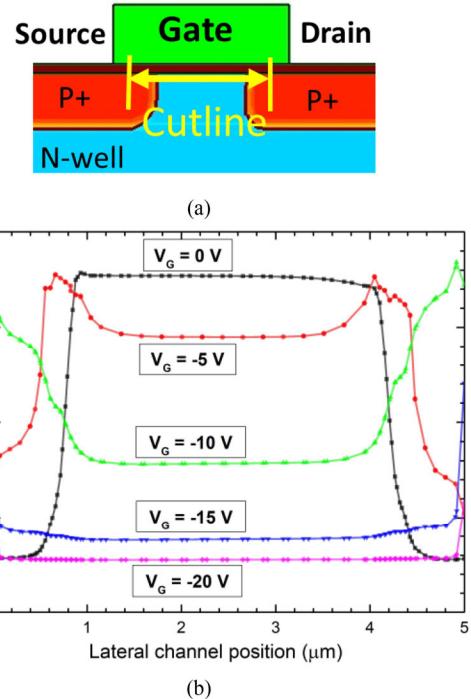

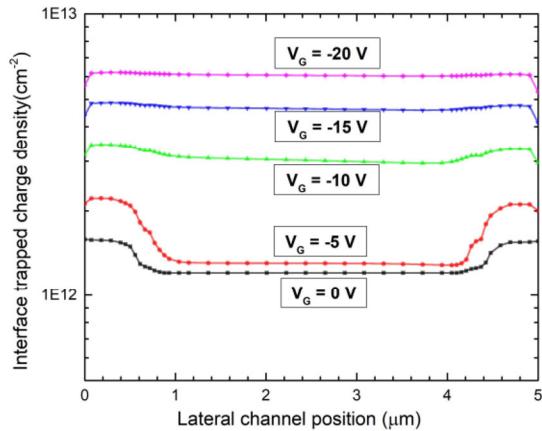

With the completed models, we probe inside the device to gain further details which usually cannot be acquired by direct measurements. The channel mobility close to the surface (surface mobility) as a function of position in the channel of a pMOS with 4  $\mu\text{m}$  channel length is presented in Fig. 15. The simulation was performed at  $V_D = -0.5$  V with varying  $V_G$  at 0 V, -5 V, -10 V, -15 V, and -20 V. A cutline below the surface along the channel region shown in Fig. 15(a) was placed to extract the hole's surface mobility. The total cutline length is 5  $\mu\text{m}$ . The 4  $\mu\text{m}$  channel position along the cutline is from 0.5  $\mu\text{m}$  to 4.5  $\mu\text{m}$ . It is noticed in Fig. 15(b) that the mobility for a given gate voltage across the effective channel length (which is less than the defined channel length due to the diffusion of the drain/source ion implantation regions) is fairly constant in the linear operation region. It shows that at  $V_G$  at -5 V, which is just below threshold, the surface mobility is approximately 30  $\text{cm}^2/(\text{V}\cdot\text{s})$ . As the gate voltage decreases to -20 V, the surface mobility decreases dramatically from 30  $\text{cm}^2/(\text{V}\cdot\text{s})$  at  $V_G = -5$  V to 6  $\text{cm}^2/(\text{V}\cdot\text{s})$  at  $V_G = -20$  V. It is also observed that the surface mobility increases close to the source and drain region when the pMOS is operating at inversion. This is due to the existence of the depletion regions where the vertical field is lower than the channel. This gives rise to less surface scattering given in equations (11) and (12).

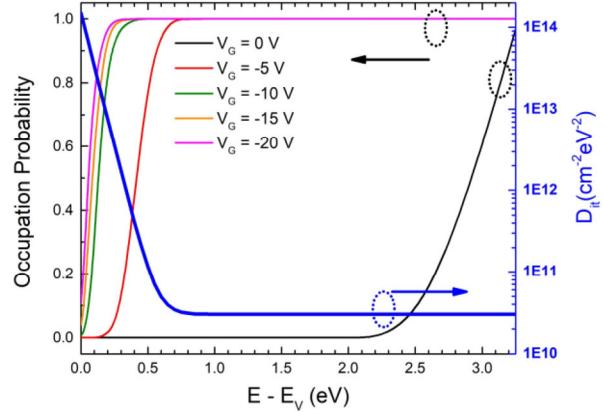

Fig. 16 shows the interface trap density and occupation probability of these traps as a function of energy with different gate bias. When the trap is occupied (the occupation probability = 1), the trap shows the polarity as illustrated in Fig. 12. It is observed that the 100% possibility curve of trap occupation moves toward the valence band edge rapidly as the gate bias decreases. Total occupied interface trap density in the SiC/SiO<sub>2</sub> interface along the cutline range shown in Fig. 15(a) as a function of the gate bias is presented in

FIGURE 15. (a) Cross-section of the channel region, (b) surface hole mobility as a function of position in the channel simulated at  $V_D = -0.5$  V, and  $V_G = 0$  V, -5 V, -10 V, -15 V, and -20 V.

FIGURE 16. Interface trap density (right) and occupation probability (left) as a function of energy for pMOS.

Fig. 17. As expected from Fig. 15, the occupation of the traps increases for lower gate voltage since with the decrease in gate voltage, holes are pulled closer to the interface that increases the hole concentration in the channel. These occupied traps act as a major role in the Coulomb scattering. Regarding the scattering mechanisms in equation (9), at low-field region, surface phonon and Coulomb scattering limit the mobility, while at high-field, surface roughness becomes the dominant scattering mechanism. The simulation results with models calibrated against our experimental results confirm that enhancing oxide quality significantly improves mobility, and this remains a primary area of future work.

FIGURE 17. Interface trapped charge density (occupied interface traps) as a function of energy with different gate bias.

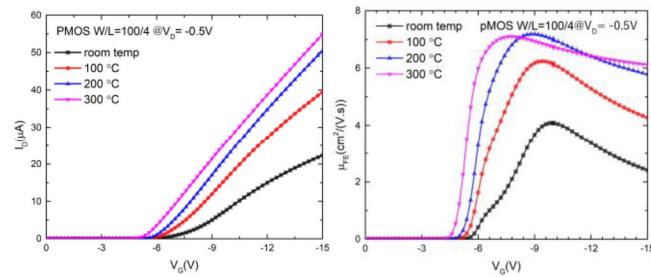

FIGURE 18. (a)  $I_D$ - $V_G$  of p-channel MOSFET with  $W = 100 \mu\text{m}$ ,  $L = 4 \mu\text{m}$ , (b)  $\mu_{FE}$  curves with varying temperature.

Besides the room temperature, the simulation deck also yields good results at high temperature. The  $I_D$ - $V_G$  and  $\mu_{FE}$  of n-channel MOSFET with  $W = 100 \mu\text{m}$  and  $L = 4 \mu\text{m}$  are presented in Fig. 18, which match very well with the experimental results in Fig. 7(c) and 9(b). The calibrated mobility and interface traps models agree with the experiment as moving to the high temperature application since the models have been defined as temperature dependent. The developed simulation deck for SiC pMOS, which specifically accounts for the individual effects of numerous physical mechanisms, is very useful to predict how device performance could be improved.

#### IV. CONCLUSION

Both n-channel and p-channel MOSFETs fabricated with the optimized Fraunhofer IISB SiC CMOS process are characterized from room temperature to 300°C. The SCE arises when the channel length reduces to a certain point which can be estimated by the presented empirical relationship. The low mobility extraction results (the peak  $\mu_{FE}$  for nMOS is less than 20  $\text{cm}^2/(\text{V} \cdot \text{s})$  while the pMOS is below 8  $\text{cm}^2/(\text{V} \cdot \text{s})$ ) lead to thorough SiC/SiO<sub>2</sub> interface studies. The interface trap distribution and scattering models adopted in the TCAD simulation for the p-channel MOSFET yield good simulation results matching well with the characterizations. Meanwhile, the high p-type ohmic contact resistivity is

observed compared to the n-type ohmic contact and this is further verified by the characterization of TLM structures. It still remains a challenge to get a low ohmic p-type contact resistivity for commercial manufacturing. Overall, this research shows a promising potential of SiC low voltage MOSFETs to be monolithically integrated with SiC power devices and operate under harsh environments which Si counterparts cannot achieve.

#### REFERENCES

- [1] T. Kimoto and J. A. Cooper, *Fundamentals of Silicon Carbide Technology: Growth, Characterization, Devices, and Applications*. Singapore: Wiley, 2014.

- [2] K. Tachiki, T. Ono, T. Kobayashi, and T. Kimoto, “Short-channel effects in SiC MOSFETs based on analyses of saturation drain current,” *IEEE Trans. Electron Devices*, vol. 68, no. 3, pp. 1382–1384, Mar. 2021, doi: [10.1109/TED.2021.3053518](https://doi.org/10.1109/TED.2021.3053518).

- [3] H. O’Brien et al., “Review of high voltage silicon carbide device research at the army research laboratory,” in *Proc. Abstracts IEEE Int. Conf. Plasma Sci.*, Chicago, IL, USA, 2011, p. 1, doi: [10.1109/PLASMA.2011.5993032](https://doi.org/10.1109/PLASMA.2011.5993032).

- [4] T. Kimoto, “2-SiC material properties,” in *Wide Bandgap Semiconductor Power Devices*, B. J. Baliga, Ed., Cambridge, U.K.: Woodhead Publ., 2019, pp. 21–42. doi: [10.1016/B978-0-08-102306-8.00002-2](https://doi.org/10.1016/B978-0-08-102306-8.00002-2).

- [5] H. Wang et al., “A review of silicon carbide CMOS technology for harsh environments,” *Mater. Sci. Semicond. Process.*, vol. 178, Aug. 2024, Art. no. 108422, doi: [10.1016/j.mssp.2024.108422](https://doi.org/10.1016/j.mssp.2024.108422).

- [6] M. Treu, R. Rupp, P. Blaschitz, and J. Hilsenbeck, “Commercial SiC device processing: Status and requirements with respect to SiC based power devices,” *Superlattices Microstruct.*, vol. 40, nos. 4–6, pp. 380–387, Oct. 2006, doi: [10.1016/j.spmi.2006.09.005](https://doi.org/10.1016/j.spmi.2006.09.005).

- [7] S. B. Isukapati et al., “Development of isolated CMOS and HV MOSFET on an N-epi/P-epi/4H-SiC N<sup>+</sup> substrate for power IC applications,” in *Proc. IEEE 8th Workshop Wide Bandgap Power Devices Appl. (WiPDA)*, Redondo Beach, CA, USA, 2021, pp. 118–122, doi: [10.1109/WiPDA49284.2021.9645134](https://doi.org/10.1109/WiPDA49284.2021.9645134).

- [8] P. G. Neudeck, R. S. Okojie, and L.-Y. Chen, “High-temperature electronics—A role for wide bandgap semiconductors?” *Proc. IEEE*, vol. 90, no. 6, pp. 1065–1076, Jun. 2002, doi: [10.1109/JPROC.2002.1021571](https://doi.org/10.1109/JPROC.2002.1021571).

- [9] R. W. Johnson, J. L. Evans, P. Jacobsen, J. R. Thompson, and M. Christopher, “The changing automotive environment: High-temperature electronics,” *IEEE Trans. Electron. Packag. Manuf.*, vol. 27, no. 3, pp. 164–176, Jul. 2004, doi: [10.1109/TEPM.2004.843109](https://doi.org/10.1109/TEPM.2004.843109).

- [10] M. H. Weng et al., “Recent advance in high manufacturing readiness level and high temperature CMOS mixed-signal integrated circuits on silicon carbide,” *Semicond. Sci. Technol.*, vol. 32, no. 5, Apr. 2017, Art. no. 54003, doi: [10.1088/1361-6641/aa61de](https://doi.org/10.1088/1361-6641/aa61de).

- [11] S. B. Isukapati et al., “Monolithic integration of lateral HV power MOSFET with LV CMOS for SiC power IC technology,” in *Proc. 33rd Int. Symp. Power Semicond. Devices ICs (ISPSD)*, Nagoya, Japan, 2021, pp. 267–270, doi: [10.23919/ISPSD50666.2021.9452235](https://doi.org/10.23919/ISPSD50666.2021.9452235).

- [12] S. J. Bader et al., “Prospects for wide bandgap and ultrawide bandgap CMOS devices,” *IEEE Trans. Electron Devices*, vol. 67, no. 10, pp. 4010–4020, Oct. 2020, doi: [10.1109/TED.2020.3010471](https://doi.org/10.1109/TED.2020.3010471).

- [13] R. Khazaka, L. Mendizabal, D. Henry, and R. Hanna, “Survey of high-temperature reliability of power electronics packaging components,” *IEEE Trans. Power Electron.*, vol. 30, no. 5, pp. 2456–2464, May 2015, doi: [10.1109/TPEL.2014.2357836](https://doi.org/10.1109/TPEL.2014.2357836).

- [14] D. B. Slater, G. M. Johnson, L. A. Lipkin, A. V. Suvorov, and J. W. Palmour, “Demonstration of a 6H-SiC CMOS technology,” in *Proc. 54th Annu. Device Res. Conf. Dig.*, Santa Barbara, CA, USA, 1996, pp. 162–163, doi: [10.1109/DRC.1996.546421](https://doi.org/10.1109/DRC.1996.546421).

- [15] S. Ryu, “Development of CMOS technology for smart power applications in silicon carbide,” Ph.D. dissertation, Purdue Univ., West Lafayette, IN, USA, May 1997.

[16] R. A. R. Young, D. T. Clark, and J. D. Cormack, "High temperature digital and analogue integrated circuits in silicon carbide," *Mater. Sci. Forum*, vols. 740–742, pp. 1065–1068, Jan. 2013, doi: [10.4028/www.scientific.net/MSF.740-742.1065](https://doi.org/10.4028/www.scientific.net/MSF.740-742.1065).

[17] M. Masunaga, S. Sato, A. Shima, and R. Kuwana, "The performance of operational amplifiers consisting of 4H-SiC CMOS after gamma irradiation," *IEEE Trans. Electron Devices*, vol. 66, no. 1, pp. 343–348, Jan. 2019, doi: [10.1109/TED.2018.2877846](https://doi.org/10.1109/TED.2018.2877846).

[18] M. Masunaga, S. Sato, R. Kuwana, N. Sugii, and A. Shima, "4H-SiC CMOS transimpedance amplifier of gamma-irradiation resistance over 1 MGy," *IEEE Trans. Electron Devices*, vol. 67, no. 1, pp. 224–229, Jan. 2020, doi: [10.1109/TED.2019.2953935](https://doi.org/10.1109/TED.2019.2953935).

[19] K. Tachiki, T. Ono, T. Kobayashi, H. Tanaka, and T. Kimoto, "Estimation of threshold voltage in SiC short-channel MOSFETs," *IEEE Trans. Electron Devices*, vol. 65, no. 7, pp. 3077–3080, Jul. 2018, doi: [10.1109/TED.2018.2837028](https://doi.org/10.1109/TED.2018.2837028).

[20] M. Cabello, V. Soler, G. Rius, J. Montserrat, J. Rebollo, and P. Godignon, "Advanced processing for mobility improvement in 4H-SiC MOSFETs: A review," *Mater. Sci. Semicond. Process.*, vol. 78, pp. 22–31, May 2018, doi: [10.1016/j.mssp.2017.10.030](https://doi.org/10.1016/j.mssp.2017.10.030).

[21] V. Tilak, "Inversion layer electron transport in 4H-SiC metal-oxide-semiconductor field-effect transistors," *Phys. Status Solidi A*, vol. 206, no. 10, pp. 2391–2402, 2009, doi: [10.1002/pssa.200925164](https://doi.org/10.1002/pssa.200925164).

[22] S. Dhar et al., "Inversion layer carrier concentration and mobility in 4H-SiC metal-oxide-semiconductor field-effect transistors," *J. Appl. Phys.*, vol. 108, no. 5, Sep. 2010, Art. no. 54509, doi: [10.1063/1.3484043](https://doi.org/10.1063/1.3484043).

[23] M. Ekström, B. G. Malm, and C.-M. Zetterling, "High-temperature recessed channel SiC CMOS inverters and ring oscillators," *IEEE Electron Device Lett.*, vol. 40, no. 5, pp. 670–673, May 2019, doi: [10.1109/LED.2019.2903184](https://doi.org/10.1109/LED.2019.2903184).

[24] J. Wang and X. Jiang, "Review and analysis of SiC MOSFETs' ruggedness and reliability," *IET Power Electron.*, vol. 13, no. 3, pp. 445–455, Feb. 2020, doi: [10.1049/iet-pel.2019.0587](https://doi.org/10.1049/iet-pel.2019.0587).

[25] P. Fiorenza, F. Giannazzo, and F. Roccaforte, "Characterization of SiO<sub>2</sub>/4H-SiC interfaces in 4H-SiC MOSFETs: A review," *Energies*, vol. 12, no. 12, p. 2310, Jan. 2019, doi: [10.3390/en12122310](https://doi.org/10.3390/en12122310).

[26] M. Albrecht, T. Erlbacher, A. Bauer, and L. Frey, "Improving 5 V digital 4H-SiC CMOS ICs for operating at 400°C using PMOS channel implantation," *Mater. Sci. Forum*, vol. 963, pp. 827–831, Jul. 2019, doi: [10.4028/www.scientific.net/MSF.963.827](https://doi.org/10.4028/www.scientific.net/MSF.963.827).

[27] M. Albrecht, D. Pérez, R. C. Martens, A. J. Bauer, and T. Erlbacher, "Impact of channel implantation on a 4H-SiC CMOS operational amplifier for high temperature applications," *Mater. Sci. Forum*, vol. 1004, pp. 1123–1128, Jul. 2020, doi: [10.4028/www.scientific.net/MSF.1004.1123](https://doi.org/10.4028/www.scientific.net/MSF.1004.1123).

[28] A. May, M. Rommel, A. Abbasi, and T. Erlbacher, "Threshold voltage adjustment on 4H-SiC MOSFETs using P-doped polysilicon as a gate material," *Key Eng. Mater.*, vol. 947, pp. 57–62, May 2023, doi: [10.4028/p-w6bx49](https://doi.org/10.4028/p-w6bx49).

[29] M. Rambach, A. J. Bauer, and H. Ryssel, "Electrical and topographical characterization of aluminum implanted layers in 4H silicon carbide," *Phys. Status Solidi Basic Res.*, vol. 245, no. 7, pp. 1315–1326, 2008, doi: [10.1002/pssb.200743510](https://doi.org/10.1002/pssb.200743510).

[30] A. Ortiz-Conde, F. J. G. Sanchez, J. J. Liou, A. Cerdeira, M. Estrada, and Y. Yue, "A review of recent MOSFET threshold voltage extraction methods," *Microelectron. Reliab.*, vol. 42, pp. 583–596, Apr./May 2002, doi: [10.1016/S0026-2714\(02\)00027-6](https://doi.org/10.1016/S0026-2714(02)00027-6).

[31] S. Yu, M. H. White and A. K. Agarwal, "Experimental determination of interface trap density and fixed positive oxide charge in commercial 4H-SiC power MOSFETs," *IEEE Access*, vol. 9, pp. 149118–149124, 2021, doi: [10.1109/ACCESS.2021.3124706](https://doi.org/10.1109/ACCESS.2021.3124706).

[32] G. Y. Chung et al., "Improved inversion channel mobility for 4H-SiC MOSFETs following high temperature anneals in nitric oxide," *IEEE Electron Device Letters*, vol. 22, no. 4, pp. 176–178, Apr. 2001, doi: [10.1109/55.915604](https://doi.org/10.1109/55.915604).

[33] J. R. Brews, W. Fichtner, E. H. Nicollian, and S. M. Sze, "Generalized guide for MOSFET miniaturization," in *Proc. Int. Electron Devices Meeting*, Washington, DC, USA, 1979, pp. 10–13, doi: [10.1109/IEDM.1979.189526](https://doi.org/10.1109/IEDM.1979.189526).

[34] Y. Taur and T. H. Ning, *Fundamentals of Modern VLSI Devices*. New York, NY, USA: Cambridge Univ., 1998.

[35] K. Moges, T. Hosoi, T. Shimura, and H. Watanabe, "Demonstration of 4H-SiC CMOS circuits consisting of well-balanced n- and p-channel MOSFETs fabricated by ultrahigh-temperature gate oxidation," *Appl. Phys. Exp.*, vol. 14, no. 9, 2021, Art. no. 91006, doi: [10.35848/1882-0786/ac1c43/meta](https://doi.org/10.35848/1882-0786/ac1c43/meta).

[36] S. Lee, Y. Song, H. Park, A. Zaslavsky, and D. C. Paine, "Channel scaling and field-effect mobility extraction in amorphous InZnO thin film transistors," *Solid-State Electron*, vol. 135, 2017, pp. 94–99, doi: [10.1016/j.sse.2017.06.033](https://doi.org/10.1016/j.sse.2017.06.033).

[37] F. Laariedh, M. Lazar, P. Cremillieu, J. Penuelas, J.-L. Leclercq, and D. Planson, "The role of nickel and titanium in the formation of ohmic contacts on p-type 4H-SiC," *Semicond. Sci. Technol.*, vol. 28, no. 4, 2013, Art. no. 45007, doi: [10.1088/0268-1242/28/4/045007](https://doi.org/10.1088/0268-1242/28/4/045007).

[38] S. T. Pantelides, S. Wang, and A. Franceschetti, "Si/SiO<sub>2</sub> and SiC/SiO<sub>2</sub> interfaces for MOSFETs—Challenges and advances," *Mater. Sci. Forum*, vols. 527–529, pp. 935–948, Oct. 2006, doi: [10.4028/www.scientific.net/MSF.527-529.935](https://doi.org/10.4028/www.scientific.net/MSF.527-529.935).

[39] S. Potbhare, N. Goldsman, G. Pennington, J. M. McGarrity, and A. Lelis, "Characterization of 4H-SiC MOSFET interface trap charge density using a first principles coulomb scattering mobility model and device simulation," in *Proc. Int. Conf. Simul. Semicond. Process. Devices*, Tokyo, Japan, 2005, pp. 95–98, doi: [10.1109/SISPAD.2005.201481](https://doi.org/10.1109/SISPAD.2005.201481).

[40] L. Yang et al., "Analysis of mobility for 4H-SiC N/P-channel MOSFETs up to 300 °C," *IEEE Trans. Electron Devices*, vol. 68, no. 8, pp. 3936–3941, Aug. 2021, doi: [10.1109/TED.2021.3084908](https://doi.org/10.1109/TED.2021.3084908).

[41] M. Roschke and F. Schwierz, "Electron mobility models for 4H, 6H, and 3C SiC [MESFETs]," *IEEE Trans. Electron Devices*, vol. 48, no. 7, pp. 1442–1447, Jul. 2001, doi: [10.1109/16.930664](https://doi.org/10.1109/16.930664).

[42] M. Ruff, H. Mitlehner, and R. Helbig, "SiC devices: physics and numerical simulation," *IEEE Trans. Electron Devices*, vol. 41, no. 6, pp. 1040–1054, Jun. 1994, doi: [10.1109/16.293319](https://doi.org/10.1109/16.293319).

[43] H. Linewih, S. Dimitrijev, and K. Y. Cheong, "Channel-carrier mobility parameters for 4H SiC MOSFETs," *Microelectron. Rel.*, vol. 43, no. 3, pp. 405–411, 2003, doi: [10.1016/S0026-2714\(02\)00313-X](https://doi.org/10.1016/S0026-2714(02)00313-X).

[44] S. K. Powell, N. Goldsman, J. M. McGarrity, J. Bernstein, C. J. Scozzie, and A. Lelis, "Physics-based numerical modeling and characterization of 6H-silicon-carbide metal-oxide-semiconductor field-effect transistors," *J. Appl. Phys.*, vol. 92, no. 7, pp. 4053–4061, Oct. 2007, doi: [10.1063/1.1499523](https://doi.org/10.1063/1.1499523).

[45] S. Potbhare, *Modeling and Characterization of 4H-SiC MOSFETs: High Field, High Temperature, and Transient Effects*, Univ. Maryland, College Park, MD, USA, 2008.

[46] V. Uhnevionak et al., "Comprehensive study of the electron scattering mechanisms in 4H-SiC MOSFETs," *IEEE Trans. Electron Devices*, vol. 62, no. 8, pp. 2562–2570, Aug. 2015, doi: [10.1109/TED.2015.2447216](https://doi.org/10.1109/TED.2015.2447216).

[47] M.G. Jaikumar, S. Karmalkar, "Calibration of mobility and interface trap parameters for high temperature TCAD simulation of 4H-SiC VDMOSFETs," *Mater. Sci. Forum*, vol. 717, pp. 1101–1104, May 2012, doi: [10.3390/mi11020223](https://doi.org/10.3390/mi11020223).