## PdSe<sub>2</sub>/WSe<sub>2</sub> Nanosheet-Based Heterostructures for n-Type Field-Effect Transistors with Enhanced Performance

Arthur Bowman, Kraig Andrews, Mohan De Silva, Amanda V. Haglund, David Mandrus, Pai-Yen Chen, and Zhixian Zhou\*

Cite This: *ACS Appl. Nano Mater.* 2025, 8, 23130–23140

Read Online

ACCESS |

Metrics & More

Article Recommendations

Supporting Information

Downloaded via WAYNE STATE UNIV on January 22, 2026 at 21:41:41 (UTC).

See https://pubs.acs.org/sharingguidelines for options on how to legitimately share published articles.

**ABSTRACT:** Two-dimensional (2D) semiconductors are promising candidates for next-generation flexible electronics, but their performance is often limited by low electron mobility and substantial Schottky barriers (SBs) at metal contacts. Here, we demonstrate that PdSe<sub>2</sub>/WSe<sub>2</sub> nanosheet-based van der Waals heterostructures outperform PdSe<sub>2</sub> or WSe<sub>2</sub> nanosheets alone as channel materials for n-type field-effect transistors. Here, the WSe<sub>2</sub> nanosheet serves as a buffer layer, mitigating Fermi-level pinning and reducing SBs between Ti metal and PdSe<sub>2</sub> nanosheets. These heterostructures achieve two-terminal effective mobility exceeding 200 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> at room temperature and nearing 680 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> at 77 K. Additionally, the increased bandgap in thinner PdSe<sub>2</sub> nanosheets enables high on/off ratios ( $\sim 10^7$ ) in PdSe<sub>2</sub>/WSe<sub>2</sub>. These results underscore the potential of PdSe<sub>2</sub>/WSe<sub>2</sub> nanosheet-based heterostructures and the importance of interfacial engineering in advancing 2D electronic devices.

**KEYWORDS:** *PdSe<sub>2</sub>, WSe<sub>2</sub>, heterostructure, field-effect transistor, Schottky barrier, contact resistance*

### 1. INTRODUCTION

Atomically thin and uniform two-dimensional (2D) semiconductors, offering exceptional mechanical strength and flexibility, are promising channel materials for next-generation flexible electronics and optoelectronics, enabling performance beyond the scaling limits of Si-based metal-oxide-semiconductor field-effect transistors (MOSFETs).<sup>1–15</sup> Among 2D semiconductors, group 6 transition metal dichalcogenides (TMDs), such as MoS<sub>2</sub>, MoSe<sub>2</sub>, and WSe<sub>2</sub>, have been extensively studied. While high hole mobility exceeding 1000 cm<sup>2</sup>/V s at room temperature has been reported in WSe<sub>2</sub>,<sup>16</sup> its relatively low electron mobility at room temperature restricts its potential for complementary electronic applications.<sup>17,18</sup> Furthermore, group 6 TMDs often form significant energy barriers with commonly used metals for electrical contacts, further hindering their performance in electronic and optoelectronic devices.<sup>19–23</sup>

Recently, group 10 TMDs such as PtSe<sub>2</sub> and PdSe<sub>2</sub> have emerged as high-mobility 2D electronic materials with a theoretically predicted high electron mobility exceeding 1000 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> at room temperature,<sup>24,25</sup> significantly higher than those of group 6 TMDs like MoS<sub>2</sub> and WSe<sub>2</sub>. Experimentally, a four-terminal field-effect mobility as high as  $\sim 700$  cm<sup>2</sup>/V s at room temperature, excluding contact resistance, has been observed in hBN-encapsulated few-layer PdSe<sub>2</sub> field-effect transistors with gated graphene contacts. This mobility increases to  $\sim 10,000$  cm<sup>2</sup>/V s at cryogenic temperatures.<sup>26</sup> Moreover, group 10 TMDs exhibit greater chemical stability

compared to other high-mobility 2D semiconductors, such as black phosphorus and indium selenide (InSe).<sup>27–29</sup> Furthermore, electronic properties of some group 10 TMDs are predicted to change qualitatively with the layer number, which may open up novel applications in nanoelectronics and optoelectronics.<sup>30</sup> However, the experimentally observed two-terminal field-effect mobility of group 10 TMDs, which is pertinent to practical electronic device applications, is significantly lower, particularly in thinner samples. This discrepancy may be partially attributed to the presence of a non-negligible Schottky barrier (SB) at the drain and source contacts.<sup>27,31</sup>

In this article, we demonstrate that PdSe<sub>2</sub>/WSe<sub>2</sub> nanosheet-based van der Waals heterostructures exhibit superior performance as channel materials for n-type field-effect transistors (FETs) compared to PdSe<sub>2</sub> or WSe<sub>2</sub> alone. In these heterostructures, the WSe<sub>2</sub> nanosheet functions both as a passivation layer, protecting the underlying PdSe<sub>2</sub> nanosheet from contamination and damage during fabrication, and as a buffer layer between PdSe<sub>2</sub> and Ti metal at the source and drain contacts, mitigating the Fermi-level pinning effect and

Received: September 15, 2025

Revised: November 10, 2025

Accepted: November 12, 2025

Published: November 20, 2025

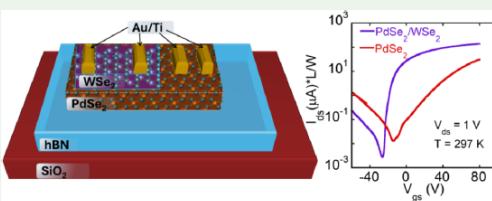

**Figure 1.** (a) Device structure of WSe<sub>2</sub> and PdSe<sub>2</sub>/WSe<sub>2</sub> FETs. Optical micrograph of FETs consisting of (i) an ~4.0 nm-thick PdSe<sub>2</sub> channel with a channel length  $L = 2.3 \mu\text{m}$  and channel width  $W = 0.4 \mu\text{m}$ , (ii) a PdSe<sub>2</sub>/WSe<sub>2</sub> heterostructure channel of an ~4.0 nm-thick PdSe<sub>2</sub> and an ~2 nm-thick WSe<sub>2</sub> with a channel length  $L = 10.7 \mu\text{m}$  and channel width  $W = 5.8 \mu\text{m}$ , and (iii) schematic of the PdSe<sub>2</sub> and PdSe<sub>2</sub>/WSe<sub>2</sub> devices. (b, c) Output characteristics of (b) the PdSe<sub>2</sub> and (c) the PdSe<sub>2</sub>/WSe<sub>2</sub> FET. (d) Transfer characteristics of the PdSe<sub>2</sub> and PdSe<sub>2</sub>/WSe<sub>2</sub> FETs plotted on a semilog scale. (e) Two-terminal 2D conductivity of the PdSe<sub>2</sub> and PdSe<sub>2</sub>/WSe<sub>2</sub> FETs as a function of gate voltage plotted on a linear scale. Field-effect mobility ( $\mu_{\text{FE}}$ ) is calculated from the average slope in the linear region of the 2D conductivity versus gate voltage curves. (f) Effective mobility of the PdSe<sub>2</sub> and PdSe<sub>2</sub>/WSe<sub>2</sub> FETs as a function of gate voltage. All the data are taken at room temperature.

significantly reduces the Schottky barrier height (SBH) between Ti metal and PdSe<sub>2</sub>.

As a result, our FETs based on WSe<sub>2</sub>/PdSe<sub>2</sub> heterostructures, composed of a few-nanometer-thick PdSe<sub>2</sub> nanosheet and a bilayer or trilayer WSe<sub>2</sub>, demonstrate high two-terminal effective electron mobility. Specifically, these devices achieve electron mobility values exceeding  $200 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  at room temperature and nearing  $680 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  at 77 K, consistent with phonon-limited electron transport mechanisms.

In contrast, FETs based solely on few-layer PdSe<sub>2</sub> (without the inclusion of WSe<sub>2</sub>) exhibit substantially lower two-terminal effective mobility. Moreover, the electron mobility achieved in FETs based on PdSe<sub>2</sub>/WSe<sub>2</sub> heterostructures significantly surpasses that of WSe<sub>2</sub> alone.<sup>18,32,33</sup> These findings suggest that electron transport in these PdSe<sub>2</sub> devices is primarily hindered by the Ti/PdSe<sub>2</sub> contacts, emphasizing the critical role of contact engineering, the importance of material selection, and the synergistic benefits of heterostructure and interfacial engineering in optimizing next-generation 2D electronic device performance.

Furthermore, the increase in bandgap with decreasing PdSe<sub>2</sub> thickness results in a higher on/off ratio for FETs based on PdSe<sub>2</sub>/WSe<sub>2</sub> heterostructures with thinner PdSe<sub>2</sub> nanosheets. Specifically, our PdSe<sub>2</sub>/WSe<sub>2</sub> heterostructure-based FET, comprising an ~2 nm (~3 layers) PdSe<sub>2</sub> nanosheet and a 2-to-3-layer WSe<sub>2</sub> nanosheet, achieves an impressive on/off ratio of  $\sim 10^7$  while simultaneously demonstrating significantly higher two-terminal electron mobility compared to FETs based solely on the constituent PdSe<sub>2</sub> or WSe<sub>2</sub>.

## 2. EXPERIMENTAL SECTION

To fabricate PdSe<sub>2</sub>/WSe<sub>2</sub> FETs, 10–30 nm-thick hBN flakes were first exfoliated on degenerately doped Si with 280 nm of thermal oxide by a mechanical exfoliation method. Next, trilayer to few-layer PdSe<sub>2</sub> and bilayer/trilayer WSe<sub>2</sub> nanosheets were also mechanically exfoliated on SiO<sub>2</sub>/Si substrates and then sequentially picked up from SiO<sub>2</sub>/Si substrates and placed on the hBN substrates by a dry transfer method using a polycarbonate (PC)/polydimethylsiloxane (PDMS) stamp on a glass microscope slide. Finally, metal electrodes, consisting of 10 nm Ti and 40 nm Au, were fabricated on top of the drain/source regions of the PdSe<sub>2</sub>/WSe<sub>2</sub> heterostructure by electron beam lithography and electron beam-assisted metal deposition. For comparison, PdSe<sub>2</sub> FETs were also fabricated by dry transfer of mechanically exfoliated PdSe<sub>2</sub> onto hBN substrates, followed by e-beam lithography and metal deposition of 10 nm Ti and 40 nm Au.

Optical microscopy and Park-Systems XE-70 noncontact mode atomic microscopy (AFM) were used to identify and characterize thin PdSe<sub>2</sub> and WSe<sub>2</sub> flakes. Electrical properties of the devices were measured by a Keithley 4200 semiconductor parameter analyzer in a Lakeshore Cryogenic probe station under high vacuum ( $1 \times 10^{-6}$  Torr).

## 3. RESULTS AND DISCUSSION

Figure 1a presents optical micrographs (panels i and ii) and a schematic (panel iii) of two FET devices, one with a PdSe<sub>2</sub> nanosheet as the channel material (panel i) and the other with a PdSe<sub>2</sub>/WSe<sub>2</sub> nanosheet-based heterostructure as the channel material (panel ii). The PdSe<sub>2</sub> in both devices is approximately 4 nm thick, while the WSe<sub>2</sub> nanosheet in the PdSe<sub>2</sub>/WSe<sub>2</sub> heterostructure is about 3 layers. To fabricate the FET devices, hBN flakes exfoliated onto degenerately doped Si with 280 nm of thermal oxide were used as ultraflat, smooth substrates to minimize dangling bonds and charge traps. Next, ultrathin WSe<sub>2</sub> nanosheets were stacked on top of the PdSe<sub>2</sub> nanosheets

exfoliated onto Si wafers with 280 nm of  $\text{SiO}_2$  using a dry transfer method to form the  $\text{PdSe}_2/\text{WSe}_2$  heterostructure, which was then picked up and transferred onto the hBN substrates.<sup>7,33,34</sup> Finally, metal electrodes consisting of 10 nm Ti and 40 nm Au were fabricated on the drain/source regions of the  $\text{PdSe}_2$  or  $\text{PdSe}_2/\text{WSe}_2$  heterostructure devices using electron beam lithography followed by electron beam-assisted metal deposition.

To measure the electrical properties of the FET devices, back-gate biases were applied through the  $\text{SiO}_2/\text{hBN}$  dielectric stack to modulate the carrier density in the channel. To allow for a fair and quantitative comparison between devices with different channel widths and lengths, the currents plotted in Figure 1b–d are normalized by the respective channel dimensions. Figure 1b,c displays the output characteristics of the two devices shown in Figure 1a. The  $\text{PdSe}_2/\text{WSe}_2$  device exhibits highly symmetric and linear  $I$ – $V$  characteristics (Figure 1c), whereas the  $I$ – $V$  curves of the  $\text{PdSe}_2$  device, with nominally identical Ti/Au contacts (Figure 1b), are significantly more nonlinear and asymmetric. This suggests a more substantial SB in the  $\text{PdSe}_2$  device compared to the  $\text{WSe}_2/\text{PdSe}_2$  heterostructure.

Figure 1d shows semilogarithmic plots of the room-temperature transfer characteristics of the two FETs at a drain/source voltage of  $V_{ds} = 1$  V. Both the on/off ratio and normalized on-current of the  $\text{PdSe}_2/\text{WSe}_2$  device are significantly higher than those of the  $\text{PdSe}_2$  device, which can be partially attributed to the enhanced on-current enabled by lower contact resistance.<sup>33</sup> Additionally, the subthreshold swing of the  $\text{PdSe}_2/\text{WSe}_2$  device is much smaller (steeper) than that of the  $\text{PdSe}_2$  device. However, the reduced switching steepness of the  $\text{PdSe}_2$  device compared to the  $\text{PdSe}_2/\text{WSe}_2$  device cannot be attributed to charge traps at the channel/gate-dielectric interface, as both devices are fabricated on the same hBN substrate and have nominally identical gate capacitance and gate-dielectric/channel (hBN/PdSe<sub>2</sub>) interface.<sup>35</sup> This suggests that the difference is likely a contact effect, arising from thermally assisted tunneling through a SB at the Ti/PdSe<sub>2</sub> contacts.<sup>36</sup> In contrast, the near absence of such a thermally assisted tunneling region in the  $\text{PdSe}_2/\text{WSe}_2$  device strongly suggests a significantly reduced SB height (SBH).

Figure 1e shows the linear plots of the two-terminal 2D conductivity (defined as  $\sigma_{2D} = \frac{L}{W} \frac{I_{ds}}{V_{ds}}$ , where  $L$  and  $W$  are the channel length and width, respectively) versus gate voltage to quantitatively compare the transfer characteristics of the two devices. While both devices exhibit n-type behavior, the threshold voltage of the  $\text{PdSe}_2$  device is approximately 40 V higher (more positive) than that of the  $\text{PdSe}_2/\text{WSe}_2$  device. This difference in threshold voltage suggests that the current in the  $\text{PdSe}_2$  device is strongly suppressed by a substantial SB in the low-carrier-density region ( $-20 < V_{gs} < 20$  V), in contrast to the  $\text{PdSe}_2/\text{WSe}_2$  device. The region of suppressed drain current on the linear plot coincides with the broadened subthreshold region (thermally assisted tunneling region) on the semilog plot shown in Figure 1d, providing further evidence of a significant SBH at the Ti/PdSe<sub>2</sub> contacts. The  $\text{WSe}_2$  layer between the Ti metal and PdSe<sub>2</sub> in the  $\text{PdSe}_2/\text{WSe}_2$  device plays a key role in significantly reducing the SBH.

Interestingly, while the 2D conductivity of the  $\text{PdSe}_2/\text{WSe}_2$  device is approximately four times higher than that of the  $\text{PdSe}_2$  device at a back-gate voltage of 80 V, the field-effect mobility in the linear region of transfer characteristics for the

former ( $148 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ ) is less than twice that of the latter ( $87 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ ). Here, the field-effect mobility is defined as

$$\mu_{FE} = \frac{1}{C_{gs}} \frac{d\sigma_{2D}}{dV_{gs}} \quad (1)$$

where  $C_{gs}$  is gate capacitance and  $\sigma_{2D}$  is the 2D conductivity. Here,  $C_{gs}$  is calculated as the equivalent series capacitance of the  $\text{SiO}_2/\text{hBN}$  dielectric stack, using the parallel-plate capacitor model and a dielectric constant of 3.5 for hBN.<sup>33</sup> The strong discrepancy between the differences in 2D conductivity and field-effect mobility of the two devices can also be attributed to the presence of a pronounced gate voltage-tunable SB at the contacts of the  $\text{PdSe}_2$  device.<sup>37</sup> The drain current in the  $\text{PdSe}_2$  device is significantly suppressed by a large SBH at low gate voltages (carrier densities). However, at higher  $V_{gs}$ , the current increases rapidly as the SB width is reduced by the gate voltage, resulting in an artificially enhanced slope in its transfer characteristics and, consequently, an overestimation of the two-terminal field-effect mobility.<sup>38</sup> Another potential artifact in extracting field-effect mobility may arise from the carrier density dependence of the intrinsic mobility (Drude mobility) of channel material. If the intrinsic mobility increases (or decreases) with carrier density, then the extracted field-effect mobility will contain an additional positive (or negative) term proportional to the first derivative of mobility with respect to gate voltage (or carrier density).<sup>39</sup> However, this is unlikely to contribute to the artificially enhanced field-effect mobility in our  $\text{PdSe}_2$  devices, as their actual mobility slightly decreases with increasing carrier density (as discussed in detail below). On the contrary, this results in a small additional negative term in the extracted field-effect mobility at high gate voltages.

In addition to field-effect mobility, we also extracted the effective mobility of the two devices. According to the Drude model, the effective mobility is defined as the ratio of 2D conductivity to carrier density:

$$\mu_{eff} = \frac{\sigma_{2D}}{n} \quad (2)$$

Here, the carrier density is defined as

$$n = C_{gs}(V_{gs} - V_{th}) \quad (3)$$

where  $V_{th}$  is the threshold voltage. To accurately derive effective mobility, it is crucial to precisely determine the threshold voltage ( $V_{th}$ ) corresponding to zero carrier density. In ideal transistors with low-resistance ohmic contacts, the effective mobility should match the actual mobility. However, the presence of a significant SB not only shifts the threshold voltage but also reduces the two-terminal 2D conductivity. As a result, effective mobility may deviate substantially from the actual channel mobility. Therefore, it is essential to extract and compare both field-effect and effective mobilities. In devices with low-resistance ohmic contacts and nearly carrier-density (gate voltage)-independent channel mobility, these values should be consistent. A discrepancy between the field-effect and effective mobility values from the same device indicates the presence of a non-negligible SB and/or carrier-density-dependent channel mobility.

The threshold voltage is influenced not only by the carrier density but also by the SBH at the source and drain contacts. In devices with ohmic contacts, the threshold voltage corresponds to the condition where the density of mobile

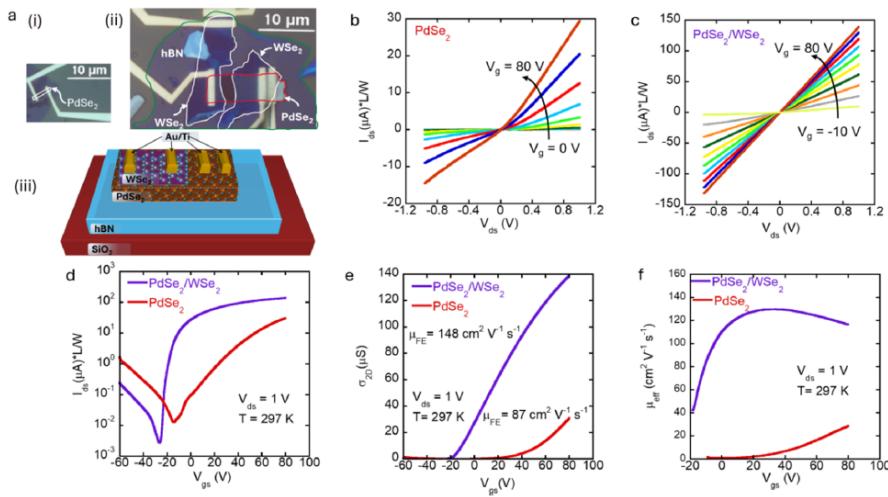

**Figure 2.** Temperature-dependent transfer characteristics and mobility comparison for two FETs with Au/Ti/WSe<sub>2</sub>/PdSe<sub>2</sub> (a, c, and e) and Au/Ti/PdSe<sub>2</sub> contacts (b, d, and f). Both devices consist of an ~6.7 nm-thick PdSe<sub>2</sub> in the channel, and the thickness of WSe<sub>2</sub> at the contacts is a trilayer. The channel length and width are  $L = 11.2 \mu\text{m}$  and  $W = 3.7 \mu\text{m}$  for the device in (a) and  $L = 7.8 \mu\text{m}$  and  $W = 3.7 \mu\text{m}$  for the device in (b). (a, b) 2D conductivity measured down to 77 K at  $V_{\text{ds}} = 1 \text{ V}$ . The insets in (a) and (b) display optical micrographs of the respective devices. (c, d) Effective mobility defined as  $\mu_{\text{eff}} = \sigma_{2\text{D}}/C_{\text{gs}}(V_{\text{gs}} - V_{\text{th}})$ . (e, f) Temperature dependence of the peak and maximum effective mobility ( $\mu_{\text{eff}}$ ) of the two devices in (c) and (d). The insets in (e) and (f) show the corresponding log-log plots. The equivalent capacitance ( $C_{\text{gs}}$ ) is 11.8 nF/cm<sup>2</sup> for both devices, based on the dielectric stack of 12 nm hBN and 280 nm SiO<sub>2</sub>.

carriers is zero. However, the presence of a substantial SBH can significantly shift the threshold voltage. Given that a much larger SBH is likely present in the PdSe<sub>2</sub> device than in the PdSe<sub>2</sub>/WSe<sub>2</sub> device, as indicated by the substantial positive threshold voltage shift in the former, we used the threshold voltage of the PdSe<sub>2</sub>/WSe<sub>2</sub> device to estimate the electron density for both devices. Since both devices are based on 4 nm-thick PdSe<sub>2</sub> nanosheets exfoliated from the same PdSe<sub>2</sub> crystal and fabricated on the same SiO<sub>2</sub>/hBN dielectric stack, we expected them to exhibit nearly identical carrier densities at a given gate voltage. This approach helps avoid underestimating the electron density in the PdSe<sub>2</sub> device due to the threshold shift.

As shown in Figure 1f, the effective mobility of the PdSe<sub>2</sub>/WSe<sub>2</sub> device closely matches its field-effect mobility, suggesting that the device performance is primarily governed by the channel rather than contact effects. In contrast, the effective mobility of the PdSe<sub>2</sub> device is several times lower than its field-effect mobility. This discrepancy indicates the presence of a gate-tunable, non-negligible SB in the PdSe<sub>2</sub> device. The rapid increase in drain current as the SB thickness decreases with gate voltage results in an artificially enhanced slope of the transfer characteristics. The effective mobilities of both PdSe<sub>2</sub> and PdSe<sub>2</sub>/WSe<sub>2</sub> devices also exhibit qualitatively different gate dependencies. While the effective mobility of the PdSe<sub>2</sub> device increases monotonically with gate voltage, reaching  $\sim 35 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  at  $\sim 80 \text{ V}$ , the effective mobility of the PdSe<sub>2</sub>/WSe<sub>2</sub> device initially rises quickly with gate voltage and then slightly decreases after reaching a maximum value of  $\sim 130 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  at  $\sim 30 \text{ V}$ . The monotonic increase in effective mobility in the

PdSe<sub>2</sub> device can be attributed to the thinning of the SB as the gate voltage becomes more positive. In contrast, the slight decrease in effective mobility with gate voltage in the PdSe<sub>2</sub>/WSe<sub>2</sub> device cannot be explained by SB tuning. We attribute this decrease to increased channel/dielectric interfacial scattering, as electrons are pulled closer to the channel/dielectric interface by the increasingly positive gate voltage. This interface scattering is likely caused by impurities introduced during the fabrication process, as the devices were fabricated in ambient conditions. We anticipate that fabricating the devices in an inert environment, such as a glovebox, will yield a cleaner channel/dielectric interface and reduce interfacial scattering, an effect that may be explored in future studies. In particular, PdSe<sub>2</sub>/WSe<sub>2</sub> devices fabricated under inert conditions are expected to exhibit higher mobility and a weaker carrier density dependence of mobility, owing to suppressed interface scattering resulting from a substantial reduction in impurities at the channel/dielectric interface.

Notably, a crack in the WSe<sub>2</sub> layer results in incomplete coverage of the channel region in the PdSe<sub>2</sub>/WSe<sub>2</sub> device shown in Figure 1. Consequently, the drain-source current flows primarily through the PdSe<sub>2</sub> layer in the PdSe<sub>2</sub>/WSe<sub>2</sub> device depicted in Figure 1a. Similar behavior, both qualitatively and quantitatively, is observed in PdSe<sub>2</sub>/WSe<sub>2</sub> devices where the WSe<sub>2</sub> layer fully covers the channel as well as the drain and source regions (see Figure S1 in the Supporting Information). This observation suggests that PdSe<sub>2</sub> serves as the active current-carrying layer in PdSe<sub>2</sub>/WSe<sub>2</sub> heterostructure devices. To confirm that the current contribution from the WSe<sub>2</sub> layer is negligible in these heterostructures, we measured

the transfer characteristics of a  $\text{WSe}_2$  FET fabricated from the same piece of  $\text{WSe}_2$  used to form the  $\text{PdSe}_2/\text{WSe}_2$  heterostructure in Figure S1. The electron current in the  $\text{WSe}_2$ -only device is approximately 5 orders of magnitude smaller than that in the  $\text{PdSe}_2/\text{WSe}_2$  heterostructure device (see Figure S2 in the Supporting Information), indicating that the current flow in the  $\text{WSe}_2$  layer is negligible and that the primary role of the  $\text{WSe}_2$  layer is to reduce the SBH and contact resistance in  $\text{PdSe}_2/\text{WSe}_2$  devices. Using a  $\text{PdSe}_2/\text{WSe}_2$  heterostructure as the channel material instead of  $\text{PdSe}_2$  significantly reduces the SBH at the drain/source contacts, leading to improved device performance.

To eliminate possible alternative current pathways—for instance, lateral carrier transport within the  $\text{WSe}_2$  layer followed by injection into  $\text{PdSe}_2$  in the gap regions—and to further evaluate the influence of the  $\text{WSe}_2$  layer on the electrical characteristics of  $\text{PdSe}_2/\text{WSe}_2$  FETs, we measured the temperature-dependent transfer characteristics of two FETs sharing the same channel material, differing primarily in that one employed  $\text{PdSe}_2/\text{WSe}_2$  and the other  $\text{PdSe}_2$  in the drain and source regions. In one, Ti metal is in direct contact with  $\text{PdSe}_2$ , while in the other, Ti metal contacts a  $\text{PdSe}_2/\text{WSe}_2$  heterostructure in the drain and source regions. To fabricate the devices, a trilayer  $\text{WSe}_2$  with a gap in between was dry-transferred onto a few-layer  $\text{PdSe}_2$ , creating a structure where the drain and source regions consist of a  $\text{PdSe}_2/\text{WSe}_2$  heterostructure, while the channel is composed solely of  $\text{PdSe}_2$  (inset of Figure 2a). To ensure that the effective channel width and length are chiefly determined by the geometry of the  $\text{PdSe}_2$  nanosheet and to exclude the possibility of lateral carrier transport within the  $\text{WSe}_2$  layer prior to entering the  $\text{PdSe}_2$  channel, we fabricated metal contacts positioned near the inner edges of the gap in the  $\text{WSe}_2$  layer. This device configuration ensures that the active channel consists predominantly of  $\text{PdSe}_2$ , while  $\text{WSe}_2$  functions solely as a buffer layer in the contact regions. After completing all measurements, we fabricated a second device by extending the metal electrodes slightly into the  $\text{PdSe}_2$  channel region using additional e-beam lithography and e-beam deposition of Ti and Au, thereby creating direct Ti/ $\text{PdSe}_2$  contacts in the drain and source regions (inset of Figure 2b). The channel length of the  $\text{PdSe}_2$  device is slightly shorter than that of the  $\text{PdSe}_2/\text{WSe}_2$  device. Figure 2a,b shows the transfer characteristics of these two devices measured at different temperatures, down to 77 K. Since both devices share essentially the same  $\text{PdSe}_2$  channel, any variations in doping or gating effects within the channel material can be disregarded.

As the electron concentration increases, the device with only  $\text{PdSe}_2$  at drain and source contacts appears to exhibit a transition from an insulating regime for  $V_{\text{gs}} < \sim 60$  V, where the current increases with temperature, to a metallic regime for  $V_{\text{gs}} > \sim 60$  V, where the current decreases with temperature as shown in Figure 2b.<sup>40</sup> In contrast, the device with  $\text{PdSe}_2/\text{WSe}_2$  at drain and source contacts exhibits a vanishingly small insulating regime as shown in Figure 2a. Because the two devices essentially share the same  $\text{PdSe}_2$  nanosheet in the channel region, except that the  $\text{PdSe}_2$  device has a slightly shorter channel due to inward electrode extensions, the observed differences in the temperature-dependent transfer characteristics can be primarily attributed to the stronger suppression of drain current by a larger SBH at the Ti/ $\text{PdSe}_2$  contacts, especially at lower carrier concentrations. As the temperature decreases, the thermionic and thermally assisted

current over the SB of the device with Ti/ $\text{PdSe}_2$  contacts becomes increasingly suppressed, especially at relatively low carrier concentrations. Consequently, a higher gate voltage is required to turn on the device at lower temperatures, as the larger SBH at the drain and source contacts shifts the threshold voltage increasingly positively. Therefore, the observed cross-over from an apparently insulating regime at low gate voltages to an apparently metallic regime at high gate voltages in the device shown in Figure 2b is most likely a contact effect rather than a true metal–insulator transition of the channel.<sup>41</sup>

On the other hand, the threshold voltage of the device with a  $\text{PdSe}_2/\text{WSe}_2$  heterostructure in the drain and source regions is nearly temperature-independent, indicating a negligibly small SBH that does not limit current flow in the on state of the device (Figure 2a). The smaller SBH also results in higher 2D conductivity with a more pronounced temperature dependence, consistent with phonon-scattering-limited electron transport in the channel. Notably, the  $\text{PdSe}_2$  device exhibits a significant positive shift in threshold voltage compared to the  $\text{PdSe}_2/\text{WSe}_2$  device, indicating that the SB plays a significant role in modulating the threshold voltage.

Next, we compare the effective mobility of the two devices as a function of gate voltage at different temperatures. Figure 2c shows that the effective mobility of the device with  $\text{PdSe}_2/\text{WSe}_2$  at drain and source contacts first rapidly increases to a maximum value with gate voltage and then gradually decreases as the gate voltage further increases. On the other hand, the effective mobility in the device with  $\text{PdSe}_2$  at drain and source contacts keeps increasing with gate voltage until  $V_{\text{gs}} = 80$  V as shown in Figure 2d. This qualitative difference between the gate dependences of the effective mobilities of the two devices suggests that the intrinsic channel mobility may slightly decrease at higher gate voltages (due to increased scattering at the dielectric/channel interface) and that the monotonous increase in the effective mobility in the device with Ti/ $\text{PdSe}_2$  contacts as shown in Figure 2d is likely an artifact caused by the gate modulation of a substantial SB at the contacts.

Another key difference between the two devices lies in the temperature dependence of their effective mobility. For the device with  $\text{PdSe}_2$  at drain and source contacts, the effective mobility increases with temperature at gate voltages below  $\sim 60$  V but decreases with temperature at higher gate voltages. In contrast, the device with  $\text{PdSe}_2/\text{WSe}_2$  at drain and source contacts exhibits a monotonic decrease in effective mobility with temperature across the entire on-state gate voltage range. The increase in effective mobility with temperature at lower gate voltages in the  $\text{PdSe}_2$  device in Figure 2d suggests that its two-terminal mobility is limited by the SB, which is nearly negligible in the  $\text{PdSe}_2/\text{WSe}_2$  device in Figure 2c. Furthermore, at 77 K, the peak effective mobility of the  $\text{PdSe}_2/\text{WSe}_2$  device in Figure 2c reaches  $\sim 680 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ , which is more than five times higher than the maximum effective mobility of the  $\text{PdSe}_2$  device in Figure 2d ( $\sim 115 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  at  $V_{\text{gs}} = 80$  V), further underscoring the influence of the SBH on two-terminal effective mobility.

The temperature dependence of the peak (maximum) two-terminal effective mobility for both devices is shown in Figure 2e,f. In the device with  $\text{PdSe}_2/\text{WSe}_2$  at drain and source contacts, the peak effective mobility increases from  $\sim 200 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  at room temperature to  $\sim 680 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  at 77 K, following a  $\mu \sim T^{-1.1}$  dependence in the temperature range between 160 K and room temperature. The maximum two-terminal effective mobility of the device with  $\text{PdSe}_2$  at drain

and source contacts is significantly lower and exhibits a much weaker temperature dependence, following  $\mu \sim T^{-0.4}$ . The stronger temperature dependence of two-terminal effective mobility of the former suggests that phonon scattering in the channel is the dominant limiting factor. By contrast, the lower two-terminal effective mobility and weaker temperature dependence of the latter can be attributed to a relatively large SBH, which increasingly limits current flow as temperature decreases.

Next, we quantitatively compare the SBH of the FET devices consisting of  $\text{PdSe}_2$  and  $\text{PdSe}_2/\text{WSe}_2$  at the drain-source regions shown in Figure 2. The FETs are modeled as two back-to-back Schottky diodes connected by a  $\text{PdSe}_2$  channel. Our SBH extraction method is based on the thermionic emission current through a reverse-bias Schottky diode at the flat-band voltage.<sup>42</sup> The thermionic emission current density is given by

$$I_{\text{ds}} = A_{2\text{D}}^* T^{3/2} e^{(-q\Phi_{\text{B}}/k_{\text{B}}T)} [1 - e^{(-qV/k_{\text{B}}T)}] \quad (4)$$

where  $A_{2\text{D}}^*$  is the 2D equivalent of Richardson's constant,  $T$  is the temperature,  $q$  is the electron charge,  $V$  is the applied voltage at the junction, and  $\Phi_{\text{B}}$  is the effective barrier height.<sup>43</sup> To extract the SBH, the drain voltage is biased such that  $|qV| \gg k_{\text{B}}T$ , which makes the term in brackets in eq 4 approximately 1 for the reverse-bias Schottky contact. Rearranging eq 4 and taking the natural log of  $I_{\text{ds}}/T^{3/2}$  yields

$$\ln\left(\frac{I_{\text{ds}}}{T^{3/2}}\right) = \ln(A_{2\text{D}}^*) - \Phi_{\text{B}}\left(\frac{q}{k_{\text{B}}T}\right) \quad (5)$$

From eq 5, the slope of  $\ln\left(\frac{I_{\text{ds}}}{T^{3/2}}\right)$  vs  $1/T$  is proportional to  $\Phi_{\text{B}}$  for a given gate voltage. Since the gate voltage effectively tunes the charge doping at the contacts, thermally assisted tunneling and tunneling current through the SB may become significant at high positive gate voltages (i.e., higher carrier densities) for an electron SB. In this regime, the extracted  $\Phi_{\text{B}}$  based on the thermionic emission model is expected to be smaller than the actual SBH. Conversely, as the gate voltage becomes increasingly negative, the channel barrier height rises, leading to a higher extracted  $\Phi_{\text{B}}$ . Consequently, a transition in slope occurs at the flat-band voltage, reflecting a change in the transport mechanism across the SB. At the flat-band voltage, the extracted  $\Phi_{\text{B}}$  approaches the actual SBH.

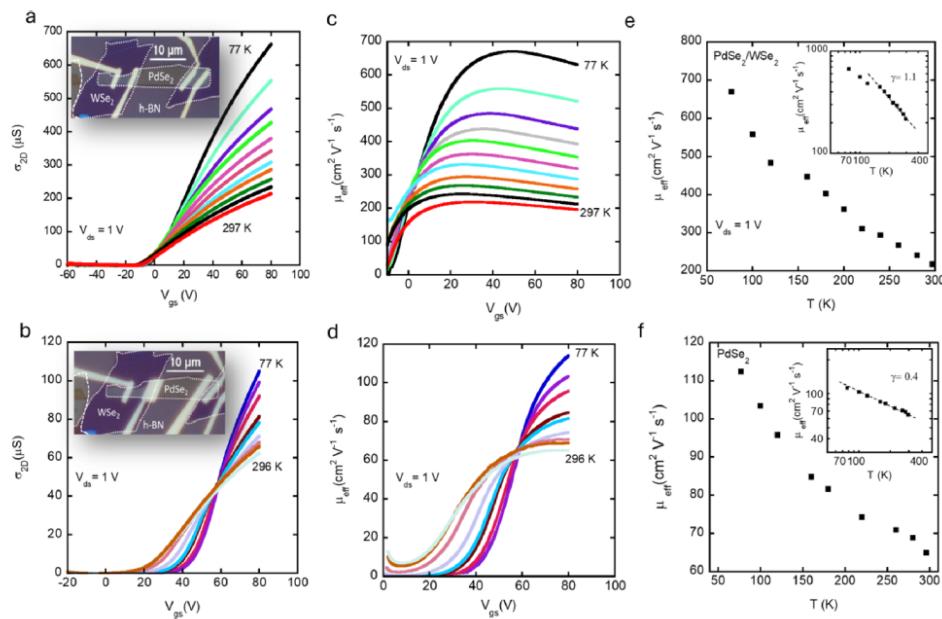

Figure 3a,c shows Arrhenius plots for FETs with  $\text{PdSe}_2$  and  $\text{PdSe}_2/\text{WSe}_2$  at the contact regions as shown in Figure 2. In the  $\text{PdSe}_2$  device, the Arrhenius plots exhibit negative slopes across the entire temperature range (Figure 3a). In contrast, for the  $\text{PdSe}_2/\text{WSe}_2$  device, the slopes are negative at temperatures below 140 K but become positive at higher temperatures (Figure 3c).

The observed positive slopes in Figure 3c cannot be explained by thermionic emission or thermally assisted tunneling over an SB and is likely limited by the phonon scattering in the channel, which is consistent with larger 2D conductivity, higher two-terminal effective mobility, and more pronounced temperature dependence of two-terminal effective mobility observed in  $\text{PdSe}_2/\text{WSe}_2$  devices. When the total resistance of an FET device is dominated by the channel instead of contacts, its current decreases with temperature due to increased phonon scattering at higher temperatures giving rise to a positive slope of the Arrhenius plots. As the temperature decreases, the reduction of channel resistance

Figure 3. Flat-band Schottky barrier height extraction. (a, c) Arrhenius plots of (a)  $\text{PdSe}_2$  and (c)  $\text{WSe}_2/\text{PdSe}_2$  FETs contacted by Ti/Au metal for various gate voltages. (b, d) Extracted n-type effective barrier height at various gate voltages, where the flat-band SBH is measured to be (b) 184 meV and (d) 22 meV in the  $\text{PdSe}_2$  and  $\text{WSe}_2/\text{PdSe}_2$  FETs, respectively.

causes contact resistance to dominate, resulting in activation behavior with negative slopes. Therefore, we extracted the  $\Phi_{\text{B}}$  of the  $\text{PdSe}_2/\text{WSe}_2$  device from the temperature region below 140 K. By contrast, the current of the  $\text{PdSe}_2$  device is contact-limited in the entire temperature region as signified by negative slopes of the Arrhenius plots (Figure 3a). The absolute value of the slope for the  $\text{PdSe}_2$  device decreases below 180 K, which corresponds to a transition from thermionic emission at higher temperatures to tunneling and/or thermally assisted tunneling at lower temperatures. Therefore, we extracted the  $\Phi_{\text{B}}$  of the  $\text{PdSe}_2$  from the temperature region above 180 K.

Figure 3b,d shows the extracted  $\Phi_{\text{B}}$  as a function of gate voltage for the  $\text{PdSe}_2$  and  $\text{PdSe}_2/\text{WSe}_2$  devices. The SBH is defined as  $\Phi_{\text{B}}$  at the flat-band voltage. For gate voltages above (i.e., more positive than) the flat-band voltage, thermally assisted tunneling current across the SB becomes significant, weakening the dependence of the extracted  $\Phi_{\text{B}}$  on the gate voltage. Using this technique, SBHs of 184 and 22 meV are determined for  $\text{PdSe}_2$  and  $\text{PdSe}_2/\text{WSe}_2$  devices at the point where the slope changes in Figure 3b,d. Consistently larger SBH values were obtained in  $\text{PdSe}_2$  devices than in  $\text{PdSe}_2/\text{WSe}_2$  devices (see Figure S3 of the Supporting Information). The drain/source contacts of our  $\text{PdSe}_2/\text{WSe}_2$  devices can be modeled as metal–semiconductor–semiconductor (MSS) or metal–insulator–semiconductor (MIS) contacts. Several different mechanisms have been proposed to explain the reduction of SBH in MIS contacts including attenuation of metal-induced gap states (MIGS), formation of electronic dipole at the insulator–semiconductor interface, passivation of interfacial defects, and interfacial doping.<sup>44–48</sup> Alternatively, the drastic reduction of SBH in our  $\text{PdSe}_2/\text{WSe}_2$  devices can be attributed to the synergy of Fermi-level pinning to  $\text{WSe}_2$  and the favorable conduction-band offset between the  $\text{WSe}_2$  and  $\text{PdSe}_2$  layers.<sup>38</sup> Among these possible mechanisms, the

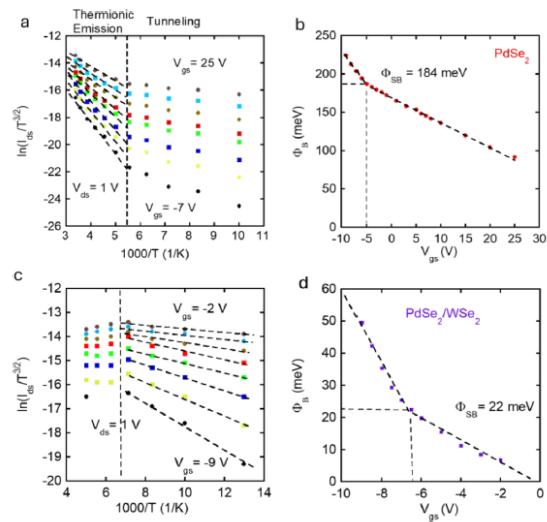

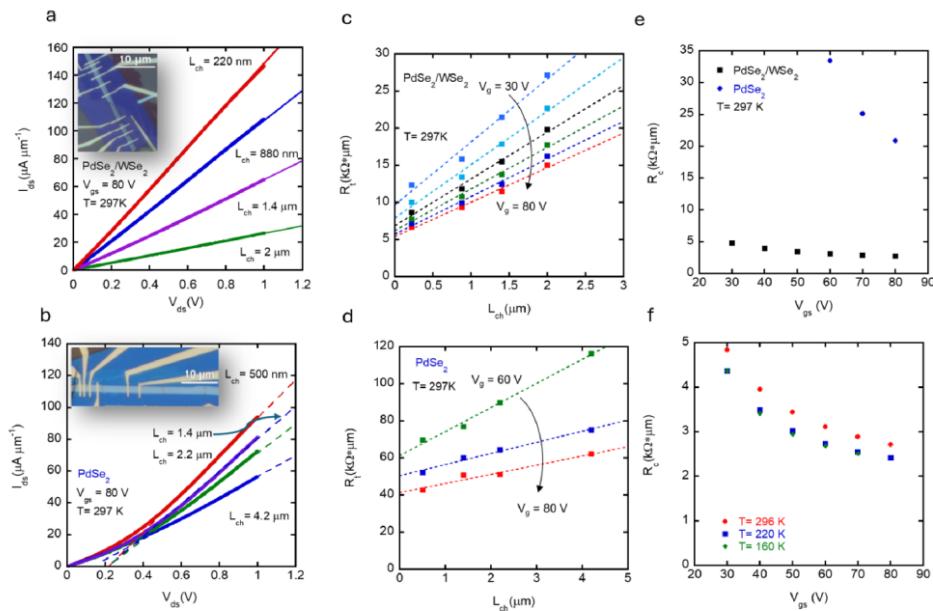

**Figure 4.** Contact resistance of  $\text{WSe}_2/\text{PdSe}_2$  and  $\text{PdSe}_2$  FETs with Ti/Au metal contacts. (a, b) Room-temperature  $I_{ds}-V_{ds}$  output curves for different channel lengths at  $V_{gs} = 80$  V for (a)  $\text{WSe}_2/\text{PdSe}_2$  and (b)  $\text{PdSe}_2$  FETs. The thicknesses of  $\text{PdSe}_2$  in the  $\text{WSe}_2/\text{PdSe}_2$  and  $\text{PdSe}_2$  devices are 8.1 and 9.0 nm, respectively. (c, d) Total resistance normalized by width ( $R_t$ ) as a function of channel length for each type determined by the slopes from (a, b) at different gate voltages for the (c)  $\text{WSe}_2/\text{PdSe}_2$  and (d)  $\text{PdSe}_2$  FETs. The  $y$ -intercept yields twice the contact resistance ( $2R_C$ ). (e) Comparison of extracted contact resistance for the  $\text{WSe}_2/\text{PdSe}_2$  and  $\text{PdSe}_2$  devices as a function of carrier density (gate voltage bias). (f) Contact resistance of the  $\text{WSe}_2/\text{PdSe}_2$  devices as a function of carrier density measured at different temperatures. The equivalent capacitance is 11.0 nF/cm<sup>2</sup> for both devices, based on the dielectric stack of 30 nm hBN and 280 nm  $\text{SiO}_2$ .

synergistic effect of Fermi-level pinning to  $\text{WSe}_2$  and the favorable conduction-band offset between the  $\text{WSe}_2$  and  $\text{PdSe}_2$  layers appears to be most consistent with the present data. Other mechanisms, such as the formation of an interfacial dipole or interfacial doping, are less likely since the threshold voltages of devices with  $\text{WSe}_2$  only at the drain and source contacts are comparable to those of devices in which  $\text{WSe}_2$  fully covers the  $\text{PdSe}_2$  channel. Furthermore, Fermi-level pinning is commonly observed between deposited metals such as Ti and TMDs like  $\text{WSe}_2$ . The relatively low electron affinity of  $\text{WSe}_2$  compared to  $\text{PdSe}_2$  favors a band alignment that reduces the SBH between the Ti contact and  $\text{PdSe}_2$ , as schematically illustrated in the band alignment diagrams (see Figure S3 of the Supporting Information). However, it is beyond the scope of this work to pinpoint the exact mechanism behind the significantly reduced SBH in our  $\text{PdSe}_2/\text{WSe}_2$  devices, as the main goal of this study is to demonstrate the superior performance of  $\text{PdSe}_2/\text{WSe}_2$  compared to  $\text{PdSe}_2$  and  $\text{WSe}_2$  as a channel material in n-type FETs. Future experiments that systematically investigate devices based on heterostructures composed of  $\text{PdSe}_2$  and various TMD nanosheets with different band alignments, as well as contact metals with different work functions, may help elucidate the underlying mechanism.

To quantify the impact of reduced SBH on contact resistance, the transfer length method (TLM) was used to extract the contact resistance of FET devices with  $\text{PdSe}_2/\text{WSe}_2$  and  $\text{PdSe}_2$  channels. Figure 4a,b shows the output characteristics of the  $\text{PdSe}_2/\text{WSe}_2$  and  $\text{PdSe}_2$  devices for different channel lengths at  $V_{gs} = 80$  V. Optical micrographs of the

devices used for TLM measurements are shown in the insets of Figure 4a,b. Because the electron current in the  $\text{WSe}_2$  layer is approximately 5 orders of magnitude lower than that in the  $\text{PdSe}_2$  layer (see Figure S2 in the Supporting Information), the channel length and width of the  $\text{PdSe}_2/\text{WSe}_2$  device are effectively defined by the geometry of the  $\text{PdSe}_2$  nanosheet, where electron transport predominantly occurs. The slight super linear behavior observed in the output characteristics of the  $\text{PdSe}_2$  device can be attributed to the substantial SBH at the drain and source contacts. Figure 4c,d shows the total resistance normalized by width ( $R_t$ ) for the  $\text{PdSe}_2/\text{WSe}_2$  and  $\text{PdSe}_2$  devices, which was derived from the slope of the  $I-V$  characteristics in Figure 4a,b and plotted as a function of channel length at various gate voltages. The reasonably good linear fit to the data across different gate voltages suggests minimal variability among the contacts and channels in each device. Since all devices with different channel lengths exhibit nearly identical threshold voltages in each TLM structure (see Figure S6 of the Supporting Information), they are expected to have the same carrier density at a given gate voltage. The  $y$ -intercept of the linear fit yields the total contact resistance  $2R_C$ . It is important to ensure that the total resistance of the device with the shortest channel is not significantly larger than  $2R_C$  in order to minimize errors in contact resistance extraction.<sup>49,50</sup> As shown in Figure 4c,d, the total resistance of the shortest channel device is dominated by the total contact resistance, suggesting that the error in the extracted contact resistance is relatively small. The TLM measurements at  $V_{gs} = 80$  V yield a contact resistance of 2.8 k $\Omega$   $\mu\text{m}$  for  $\text{PdSe}_2/\text{WSe}_2$  and 20 k $\Omega$   $\mu\text{m}$  for  $\text{PdSe}_2$  per contact, which is qualitatively consistent with

the corresponding disparities in their SBH. The difference in the contact resistance between  $\text{PdSe}_2/\text{WSe}_2$  and  $\text{PdSe}_2$  increases as the electron concentration (gate bias voltage) decreases, as shown in Figure 4e. This trend is expected due to their SBH difference: the larger SBH at the contacts of  $\text{PdSe}_2$  leads to progressively higher contact resistance at lower carrier densities. In contrast, the contact resistance in  $\text{WSe}_2/\text{PdSe}_2$  devices is significantly less sensitive to the carrier density, owing to the substantially smaller SBH at the contacts. In addition, the relatively small SBH at the contacts in  $\text{PdSe}_2/\text{WSe}_2$  devices results in a relatively weak temperature dependence of the contact resistance, as shown in Figure 4f. The TLM structure comprising FETs with different channel lengths also enables extraction of the intrinsic channel mobility, independent of contact resistance. A channel mobility of  $195 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  is obtained from the inverse of the slope in Figure 4c as a function of gate voltage (see Figure S7 in the Supporting Information). This value is consistent with the two-terminal mobility observed in similar devices in this study, confirming that carrier transport in  $\text{PdSe}_2/\text{WSe}_2$  devices is limited primarily by the channel rather than by the contacts. We anticipate that further improvements in  $\text{PdSe}_2$  material quality and fabrication processes—such as device assembly in an inert glovebox environment—will yield even higher two-terminal mobilities.

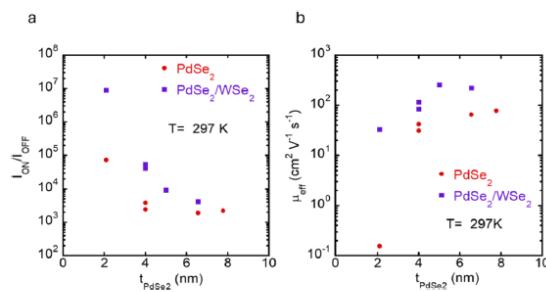

To further emphasize the advantages of the  $\text{PdSe}_2/\text{WSe}_2$  heterostructure over pure  $\text{PdSe}_2$  as a channel material in FET performance, we systematically investigated multiple  $\text{PdSe}_2$  and  $\text{PdSe}_2/\text{WSe}_2$  devices with varying  $\text{PdSe}_2$  thicknesses. These devices were fabricated using  $\text{PdSe}_2$  nanosheets of different thicknesses combined with bilayer or trilayer  $\text{WSe}_2$  nanosheets to form the  $\text{PdSe}_2/\text{WSe}_2$  heterostructures. Because the  $\text{WSe}_2$  buffer layer also functions as a tunneling barrier for carrier injection, the current transmitted through it decreases exponentially with both the tunneling barrier thickness and the square root of the barrier height.<sup>31</sup> To minimize contact resistance and improve device performance, it is therefore essential to minimize both the barrier height and thickness. However, the  $\text{WSe}_2$  layer must also be sufficiently thick to suppress Fermi-level pinning between the metal contact and the  $\text{PdSe}_2$  active layer. A monolayer  $\text{WSe}_2$  is often too thin to effectively decouple the metal– $\text{PdSe}_2$  interactions and, in addition, exhibits a lower electron affinity than its bilayer or trilayer counterparts, resulting in a higher tunneling barrier height. Consequently, bilayer or trilayer  $\text{WSe}_2$  nanosheets were selected as the buffer layer to construct the  $\text{PdSe}_2/\text{WSe}_2$  heterostructures. Figure 5 summarizes the room-temperature on/off ratio and two-terminal effective mobility as a function of  $\text{PdSe}_2$  thickness in these devices. As the  $\text{PdSe}_2$  thickness decreases, the on/off ratios of both  $\text{PdSe}_2$  and  $\text{PdSe}_2/\text{WSe}_2$  devices increase, which is expected due to the corresponding increase in the  $\text{PdSe}_2$  bandgap.<sup>27,31,52</sup> However, as shown in Figure 5a, the on/off ratio in  $\text{PdSe}_2/\text{WSe}_2$  devices is consistently higher and increases more rapidly with decreasing  $\text{PdSe}_2$  thickness compared to  $\text{PdSe}_2$  devices. As the thickness of  $\text{PdSe}_2$  decreases to approximately 2 nm, the  $\text{PdSe}_2/\text{WSe}_2$  device achieves a high on/off ratio of  $10^7$ , which is about 2 orders of magnitude higher than that of the  $\text{PdSe}_2$  device fabricated from the same  $\sim 2$  nm-thick  $\text{PdSe}_2$ , but without  $\text{WSe}_2$  (see Figure S4 of the Supporting Information). In addition, the two-terminal effective mobility of the  $\text{PdSe}_2/\text{WSe}_2$  devices is consistently higher than that of the  $\text{PdSe}_2$  devices across all  $\text{PdSe}_2$  thicknesses as shown in Figure 5b. The

Figure 5. (a) On/off ratios of the  $\text{PdSe}_2/\text{WSe}_2$  and  $\text{PdSe}_2$  FETs as a function of  $\text{PdSe}_2$  thickness. (b) Effective mobility of  $\text{PdSe}_2/\text{WSe}_2$  and  $\text{PdSe}_2$  FETs with varying  $\text{PdSe}_2$  thicknesses. The thickness of  $\text{WSe}_2$  in  $\text{PdSe}_2/\text{WSe}_2$  FETs is 2–3 layers.

mobility of our  $\text{PdSe}_2/\text{WSe}_2$  device, incorporating an  $\sim 2$  nm-thick ( $\sim 3$  layers)  $\text{PdSe}_2$ , is 2 orders of magnitude higher than that of the  $\text{PdSe}_2$  device without  $\text{WSe}_2$  (see Figure S5 of the Supporting Information) and nearly an order of a magnitude higher than that of a trilayer  $\text{PdSe}_2$  FET reported in the literature.<sup>53</sup> A high two-terminal effective mobility of  $\sim 250 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ , along with an on/off ratio approaching 4 orders of magnitude, is concurrently observed in a  $\text{PdSe}_2/\text{WSe}_2$  heterostructure FET consisting of an  $\sim 5$  nm-thick  $\text{PdSe}_2$ . These results are consistent with the lower SBH and, consequently, the reduced contact resistance in the  $\text{PdSe}_2/\text{WSe}_2$  devices.

The  $\text{PdSe}_2/\text{WSe}_2$  devices developed in this work exhibit two-terminal mobility values substantially higher than the average field-effect mobility reported for  $\text{PdSe}_2$  FETs and are comparable to or even exceed the maximum mobilities achieved in optimized  $\text{PdSe}_2$  devices (see Table S6 in the Supporting Information for details).<sup>27,31,53</sup> Moreover, the on/off current ratios of the  $\text{PdSe}_2/\text{WSe}_2$  heterostructure FETs reach  $10^4$ – $10^7$ , surpassing those of previously reported  $\text{PdSe}_2$  devices, which typically exhibit much lower ratios ( $\approx 10^2$ – $10^3$ ). It is worth noting that most literature reports only field-effect mobilities, which can be significantly overestimated due to gate-induced modulation of the SB and thus may not accurately reflect the intrinsic device performance. In our  $\text{PdSe}_2$  devices with Ti/Au contacts, a clear discrepancy is observed between  $\mu_{\text{FE}}$  and the effective mobility ( $\mu_{\text{eff}}$ ), with  $\mu_{\text{FE}}$  being substantially higher. In contrast, the  $\text{PdSe}_2/\text{WSe}_2$  heterostructures exhibit close agreement between  $\mu_{\text{FE}}$  and  $\mu_{\text{eff}}$  together with markedly higher overall mobility values than the  $\text{PdSe}_2$ -only devices. This consistency indicates that the high two-terminal mobility observed in  $\text{PdSe}_2/\text{WSe}_2$  FETs is reliably achieved. Furthermore, the contact resistance of  $\text{PdSe}_2/\text{WSe}_2$  devices is among the lowest reported for  $\text{PdSe}_2$ -based FETs, highlighting efficient charge injection across the  $\text{PdSe}_2/\text{WSe}_2$  heterostructure relative to bare  $\text{PdSe}_2$ .

Stacking two different 2D semiconductors as the channel material of FETs is a simple yet effective approach to enhancing device performance. This technique significantly reduces contact resistance by reducing SBH at the metal–semiconductor interface, leading to improved device performance. Moreover, this method is broadly applicable to a wide range of 2D semiconductors and their heterostructures, where the top layer acts as a buffer that modifies the energy alignment between the metal Fermi level and the conduction (or valence) band edge of the active layer. As a result, the electron (or hole)

SBH can be reduced for n-type (or p-type) transistors. Additionally, the top 2D semiconductor layer acts as a protective barrier, enhancing the chemical and environmental stability of the active bottom layer while shielding it from damage or contamination during the fabrication process. Compared to other interface engineering techniques, this method offers a straightforward and practical way to achieve superior electrical performance and reliability in next-generation nanoelectronic devices.

#### 4. CONCLUSIONS

In conclusion, we report the fabrication of high-performance n-type FETs by using a PdSe<sub>2</sub>/WSe<sub>2</sub> nanosheet-based heterostructure as a channel material to overcome the high SBH at the metal/PdSe<sub>2</sub> contacts and the relatively low intrinsic electron mobility of WSe<sub>2</sub>. The addition of a bilayer or trilayer WSe<sub>2</sub> nanosheet to a few-layer PdSe<sub>2</sub> nanosheet significantly lowers the SBH at the contacts and contact resistance. The improvement in drain/source contacts leads to enhanced device performance including higher on-current, higher on/off ratio, and enhanced two-terminal mobility. This contact engineering strategy of using the PdSe<sub>2</sub>/WSe<sub>2</sub> nanosheet-based heterostructure in place of the individual PdSe<sub>2</sub> or WSe<sub>2</sub> nanosheet is air-stable and thermally stable and compatible with conventional semiconductor processes. It may be implemented in the production of flexible electronics by incorporating large-scale PdSe<sub>2</sub>/WSe<sub>2</sub> nanosheet-based heterostructures.

#### ■ ASSOCIATED CONTENT

##### Supporting Information

The Supporting Information is available free of charge at <https://pubs.acs.org/doi/10.1021/acsanm.5c04263>.

Electrical properties of additional PdSe<sub>2</sub>/WSe<sub>2</sub> heterostructure, PdSe<sub>2</sub>, and WSe<sub>2</sub> devices; methods used to extract the effective capacitance of the SiO<sub>2</sub>/hBN dielectric stack; comparison of PdSe<sub>2</sub>/WSe<sub>2</sub> FETs with PdSe<sub>2</sub> devices reported in the literature (PDF)

#### ■ AUTHOR INFORMATION

##### Corresponding Author

Zhixian Zhou – Physics and Astronomy Department, Wayne State University, Detroit, Michigan 48201, United States; [orcid.org/0000-0002-9228-4260](https://orcid.org/0000-0002-9228-4260); Email: [zxzhou@wayne.edu](mailto:zxzhou@wayne.edu)

##### Authors

Arthur Bowman – Physics and Astronomy Department, Wayne State University, Detroit, Michigan 48201, United States

Kraig Andrews – Physics and Astronomy Department, Wayne State University, Detroit, Michigan 48201, United States

Mohan De Silva – Physics and Astronomy Department, Wayne State University, Detroit, Michigan 48201, United States

Amanda V. Haglund – Department of Materials Science and Engineering, The University of Tennessee, Knoxville, Tennessee 37996, United States

David Mandrus – Department of Materials Science and Engineering, The University of Tennessee, Knoxville, Tennessee 37996, United States; Materials Science and Technology Division, Oak Ridge National Laboratory, Oak

Ridge, Tennessee 37831, United States; [orcid.org/0003-3616-7104](https://orcid.org/0003-3616-7104)

Pai-Yen Chen – Department of Electrical & Computer Engineering, University of Illinois Chicago, Chicago, Illinois 60607, United States; [orcid.org/0000-0002-8112-8457](https://orcid.org/0000-0002-8112-8457)

Complete contact information is available at: <https://pubs.acs.org/10.1021/acsanm.5c04263>

#### Notes

The authors declare no competing financial interest.

#### ■ ACKNOWLEDGMENTS

This work was partially supported by NSF grant nos. 2004445, 2210861, and 2210977. D.M. and A.V.H. acknowledge support from the Gordon and Betty Moore Foundation's EPiQS Initiative, Grant GBMF9069.

#### ■ REFERENCES

- (1) Radisavljevic, B.; Radenovic, A.; Brivio, J.; Giacometti, V.; Kis, A. Single-layer MoS<sub>2</sub> transistors. *Nat. Nanotechnol.* 2011, 6 (3), 147–150.

- (2) Wang, Q. H.; Kalantazadeh, K.; Kis, A.; Coleman, J. N.; Strano, M. S. Electronics and optoelectronics of two-dimensional transition metal dichalcogenides. *Nat. Nano* 2012, 7 (11), 699–712.

- (3) Liu, H.; Neal, A. T.; Zhu, Z.; Luo, Z.; Xu, X.; Tománek, D.; Ye, P. D. Phosphorene: An Unexplored 2D Semiconductor with a High Hole Mobility. *ACS Nano* 2014, 8 (4), 4033–4041.

- (4) Li, L.; Yu, Y.; Ye, G. J.; Ge, Q.; Ou, X.; Wu, H.; Feng, D.; Chen, X. H.; Zhang, Y. Black phosphorus field-effect transistors. *Nat. Nano* 2014, 9, 372–377.

- (5) Jones, A. M.; Yu, H.; Ghimire, N. J.; Wu, S.; Aivazian, G.; Ross, J. S.; Zhao, B.; Yan, J.; Mandrus, D. G.; Xiao, D.; Yao, W.; Xu, X. Optical generation of excitonic valley coherence in monolayer WSe<sub>2</sub>. *Nat. Nano* 2013, 8 (9), 634–638.

- (6) Yin, Z.; Li, H.; Li, H.; Jiang, L.; Shi, Y.; Sun, Y.; Lu, G.; Zhang, Q.; Chen, X.; Zhang, H. Single-Layer MoS<sub>2</sub> Phototransistors. *ACS Nano* 2012, 6 (1), 74–80.

- (7) Hong, T.; Chamlagain, B.; Wang, T.; Chuang, H.-J.; Zhou, Z.; Xu, Y. Q. Anisotropic Photocurrent Response at Black Phosphorous-MoS<sub>2</sub> p-n Heterojunctions. *Nanoscale* 2015, 7, 18537.

- (8) Chang, H.-Y.; Yang, S.; Lee, J.; Tao, L.; Hwang, W.-S.; Jena, D.; Lu, N.; Akinwande, D. High-Performance, Highly Bendable MoS<sub>2</sub> Transistors with High-K Dielectrics for Flexible Low-Power Systems. *ACS Nano* 2013, 7 (6), 5446–5452.

- (9) Yoon, J.; Park, W.; Bae, G.-Y.; Kim, Y.; Jang, H. S.; Hyun, Y.; Lim, S. K.; Kahng, Y. H.; Hong, W.-K.; Lee, B. H.; Ko, H. C. Highly Flexible and Transparent Multilayer MoS<sub>2</sub> Transistors with Graphene Electrodes. *Small* 2013, 9 (19), 3295–3300.

- (10) Akinwande, D.; Petrone, N.; Hone, J. Two-dimensional flexible nanoelectronics. *Nat. Commun.* 2014, 5, 5678.

- (11) Das, S.; Gulotty, R.; Sumant, A. V.; Roelofs, A. All Two-Dimensional, Flexible, Transparent, and Thinnest Thin Film Transistor. *Nano Lett.* 2014, 14 (5), 2861–2866.

- (12) Liu, H.; Neal, A. T.; Ye, P. D. Channel Length Scaling of MoS<sub>2</sub>MOSFETs. *ACS Nano* 2012, 6 (10), 8563–8569.

- (13) Desai, S. B.; Madhvapathy, S. R.; Sachid, A. B.; Llinas, J. P.; Wang, Q.; Ahn, G. H.; Pitner, G.; Kim, M. J.; Bokor, J.; Hu, C.; Wong, H.-S. P.; Javey, A. MoSSub/2 sub transistors with 1-nanometer gate lengths. *Science* 2016, 354 (6308), 99–102.

- (14) Liu, Y.; Guo, J.; Wu, Y.; Zhu, E.; Weiss, N. O.; He, Q.; Wu, H.; Cheng, H.-C.; Xu, Y.; Shakir, I.; Huang, Y.; Duan, X. Pushing the Performance Limit of Sub-100 nm Molybdenum Disulfide Transistors. *Nano Lett.* 2016, 16 (10), 6337–6342.

- (15) Nourbakhsh, A.; Zubair, A.; Sajjad, R. N.; Tavakkoli KG, A.; Chen, W.; Fang, S.; Ling, X.; Kong, J.; Dresselhaus, M. S.; Kaxiras, E.; Berggren, K. K.; Antoniatis, D.; Palacios, T. MoS<sub>2</sub> Field-Effect

Transistor with Sub-10 nm Channel Length. *Nano Lett.* 2016, **16** (12), 7798–7806.

(16) Pack, J.; Guo, Y.; Liu, Z.; Jessen, B. S.; Holtzman, L.; Liu, S.; Cothrine, M.; Watanabe, K.; Taniguchi, T.; Mandrus, D. G.; Barmak, K.; Hone, J.; Dean, C. R. Charge-transfer contacts for the measurement of correlated states in high-mobility WSe<sub>2</sub>. *Nat. Nano* 2024, **19** (7), 948–954.

(17) Cui, X.; Lee, G.-H.; Kim, Y. D.; Arefe, G.; Huang, P. Y.; Lee, C.-H.; Chenet, D. A.; Zhang, X.; Wang, L.; Ye, F.; Pizzocchero, F.; Jessen, B. S.; Watanabe, K.; Taniguchi, T.; Muller, D. A.; Low, T.; Kim, P.; Hone, J. Multi-terminal transport measurements of MoS<sub>2</sub> using a van der Waals heterostructure device platform. *Nat. Nano* 2015, **10** (6), 534–540.

(18) Xu, S.; Wu, Z.; Lu, H.; Han, Y.; Long, G.; Chen, X.; Han, T.; Ye, W.; Wu, Y.; Lin, J.; Shen, J.; Cai, Y.; He, Y.; Zhang, F.; Lortz, R.; Cheng, C.; Wang, N. Universal low-temperature Ohmic contacts for quantum transport in transition metal dichalcogenides. *2D Mater.* 2016, **3** (2), No. 021007.

(19) Fang, H.; Chuang, S.; Chang, T. C.; Takei, K.; Takahashi, T.; Javey, A. High-Performance Single Layered WSe<sub>2</sub> p-FETs with Chemically Doped Contacts. *Nano Lett.* 2012, **12**, 3788–3792.

(20) Das, S.; Appenzeller, J. WSe<sub>2</sub> field effect transistors with enhanced ambipolar characteristics. *Appl. Phys. Lett.* 2013, **103** (10), 103501.

(21) Allain, A.; Kang, J.; Banerjee, K.; Kis, A. Electrical contacts to two-dimensional semiconductors. *Nat. Mater.* 2015, **14** (12), 1195–1205.

(22) Das, S.; Chen, H.-Y.; Penumatcha, A. V.; Appenzeller, J. High Performance Multilayer MoS<sub>2</sub> Transistors with Scandium Contacts. *Nano Lett.* 2013, **13**, 100–105.

(23) Liu, H.; Si, M.; Deng, Y.; Neal, A. T.; Du, Y.; Najmaei, S.; Ajayan, P. M.; Lou, J.; Ye, P. D. Switching Mechanism in Single-Layer Molybdenum Disulfide Transistors: An Insight into Current Flow across Schottky Barriers. *ACS Nano* 2014, **8** (1), 1031–1038.

(24) Huang, Z.; Zhang, W.; Zhang, W. Computational Search for Two-Dimensional MX<sub>2</sub> Semiconductors with Possible High Electron Mobility at Room Temperature. *Materials* 2016, **9** (9), 716.

(25) Zhang, W.; Huang, Z.; Zhang, W.; Li, Y. Two-dimensional semiconductors with possible high room temperature mobility. *Nano Res.* 2014, **7**, 1731.

(26) Zhang, Y.; Tian, H.; Li, H.; Yoon, C.; Nelson, R. A.; Li, Z.; Watanabe, K.; Taniguchi, T.; Smirnov, D.; Kawakami, R. K.; Goldberger, J. E.; Zhang, F.; Lau, C. N. Quantum octets in high mobility pentagonal two-dimensional PdSe<sub>2</sub>. *Nat. Commun.* 2024, **15** (1), 761.

(27) Oyedele, A. D.; Yang, S.; Liang, L.; Puretzky, A. A.; Wang, K.; Zhang, J.; Yu, P.; Pudasaini, P. R.; Ghosh, A. W.; Liu, Z.; Rouleau, C. M.; Sumpter, B. G.; Chisholm, M. F.; Zhou, W.; Rack, P. D.; Geoghegan, D. B.; Xiao, K. PdSe<sub>2</sub>: Pentagonal Two-Dimensional Layers with High Air Stability for Electronics. *J. Am. Chem. Soc.* 2017, **139** (40), 14090–14097.

(28) Sucharitkul, S.; Goble, N. J.; Kumar, U. R.; Sankar, R.; Bogorad, Z. A.; Chou, F.-C.; Chen, Y.-T.; Gao, X. P. A. Intrinsic Electron Mobility Exceeding 103 cm<sup>2</sup>/(V s) in Multilayer InSe FETs. *Nano Lett.* 2015, **15** (6), 3815–3819.

(29) Long, G.; Maryenko, D.; Shen, J.; Xu, S.; Hou, J.; Wu, Z.; Wong, W. K.; Han, T.; Lin, J.; Cai, Y.; Lortz, R.; Wang, N. Achieving Ultrahigh Carrier Mobility in Two-Dimensional Hole Gas of Black Phosphorus. *Nano Lett.* 2016, **16** (12), 7768–7773.

(30) Ciarrocchi, A.; Avsar, A.; Ovchinnikov, D.; Kis, A. Thickness-modulated metal-to-semiconductor transformation in a transition metal dichalcogenide. *Nat. Commun.* 2018, **9** (1), 919.

(31) Chow, W. L.; Yu, P.; Liu, F.; Hong, J.; Wang, X.; Zeng, Q.; Hsu, C.; Zhu, C.; Zhou, J.; Wang, X.; Xia, J.; Yan, J.; Chen, Y.; Wu, D.; Yu, T.; Shen, Z.; Lin, H.; Jin, C.; Tay, B. K.; Liu, Z. High Mobility 2D Palladium Diselenide Field-Effect Transistors with Tunable Ambipolar Characteristics. *Adv. Mater.* 2017, **29** (21), No. 1602969.

(32) Chuang, H.-J.; Tan, X.; Ghimire, N. J.; Perera, M. M.; Chamlagain, B.; Cheng, M. M.-C.; Yan, J.; Mandrus, D.; Tománek, D.; Zhou, Z. High Mobility WSe<sub>2</sub> p- and n-Type Field-Effect Transistors Contacted by Highly Doped Graphene for Low-Resistance Contacts. *Nano Lett.* 2014, **14** (6), 3594–3601.

(33) Chuang, H.-J.; Chamlagain, B.; Koehler, M.; Perera, M. M.; Yan, J.; Mandrus, D.; Tománek, D.; Zhou, Z. Low-Resistance 2D/2D Ohmic Contacts: A Universal Approach to High-Performance WSe<sub>2</sub>, MoS<sub>2</sub>, and MoSe<sub>2</sub> Transistors. *Nano Lett.* 2016, **16** (3), 1896–1902.

(34) Wang, T.; Andrews, K.; Bowman, A.; Hong, T.; Koehler, M.; Yan, J.; Mandrus, D.; Zhou, Z.; Xu, Y.-Q. High-Performance WSe<sub>2</sub> Phototransistors with 2D/2D Ohmic Contacts. *Nano Lett.* 2018, **18** (5), 2766–2771.

(35) Chan, M. Y.; Komatsu, K.; Li, S.-L.; Xu, Y.; Darmawan, P.; Kuramochi, H.; Nakahara, S.; Aparecido-Ferreira, A.; Watanabe, K.; Taniguchi, T.; Tsukagoshi, K. Suppression of thermally activated carrier transport in atomically thin MoS<sub>2</sub> on crystalline hexagonal boron nitride substrates. *Nanoscale* 2013, **5** (20), 9572–9576.

(36) Schulman, D. S.; Arnold, A. J.; Das, S. Contact engineering for 2D materials and devices. *Chem. Soc. Rev.* 2018, **47** (9), 3037–3058.

(37) Choi, H. H.; Cho, K.; Frisbie, C. D.; Sirringhaus, H.; Podzorov, V. Critical assessment of charge mobility extraction in FETs. *Nat. Mater.* 2018, **17**, 2.

(38) Andrews, K.; Bowman, A.; Rijal, U.; Chen, P.-Y.; Zhou, Z. Improved Contacts and Device Performance in MoS<sub>2</sub> Transistors Using a 2D Semiconductor Interlayer. *ACS Nano* 2020, **14** (5), 6232–6241.

(39) Baugher, B. W. H.; Churchill, H. O. H.; Yang, Y.; Jarillo-Herrero, P. Intrinsic Electronic Transport Properties of High-Quality Monolayer and Bilayer MoS<sub>2</sub>. *Nano Lett.* 2013, **13** (9), 4212–4216.

(40) Radisavljevic, B.; Kis, A. Mobility engineering and a metal–insulator transition in monolayer MoS<sub>2</sub>. *Nat. Mater.* 2013, **12** (9), 815–820.

(41) Stanley, L. J.; Chuang, H.-J.; Zhou, Z.; Koehler, M. R.; Yan, J.; Mandrus, D. G.; Popović, D. Low-Temperature 2D/2D Ohmic Contacts in WSe<sub>2</sub> Field-Effect Transistors as a Platform for the 2D Metal-Insulator Transition. *ACS Appl. Mater. Interfaces* 2021, **13** (8), 10594–10602.

(42) Liu, Y.; Guo, J.; Zhu, E.; Liao, L.; Lee, S.-J.; Ding, M.; Shakir, I.; Gambin, V.; Huang, Y.; Duan, X. Approaching the Schottky-Mott limit in van der Waals metal–semiconductor junctions. *Nature* 2018, **557** (7707), 696–700.

(43) Schroder, D. K. *Semiconductor Material and Device Characterization*; Wiley-Interscience: 2006.

(44) Wang, J.; Yao, Q.; Huang, C.-W.; Zou, X.; Liao, L.; Chen, S.; Fan, Z.; Zhang, K.; Wu, W.; Xiao, X.; Jiang, C.; Wu, W.-W. High Mobility MoS<sub>2</sub> Transistor with Low Schottky Barrier Contact by Using Atomic Thick h-BN as a Tunneling Layer. *Adv. Mater.* 2016, **28** (37), 8302–8308.

(45) Lee, S.; Tang, A.; Aloni, S.; Philip Wong, H. S. Statistical Study on the Schottky Barrier Reduction of Tunneling Contacts to CVD Synthesized MoS<sub>2</sub>. *Nano Lett.* 2016, **16** (1), 276–281.

(46) Kaushik, N.; Karmakar, D.; Nipane, A.; Karande, S.; Lodha, S. Interfacial n-Doping Using an Ultrathin TiO<sub>2</sub> Layer for Contact Resistance Reduction in MoS<sub>2</sub>. *ACS Appl. Mater. Interfaces* 2016, **8** (1), 256–263.

(47) Kim, C.; Moon, I.; Lee, D.; Choi, M. S.; Ahmed, F.; Nam, S.; Cho, Y.; Shin, H.-J.; Park, S.; Yoo, W. J. Fermi Level Pinning at Electrical Metal Contacts of Monolayer Molybdenum Dichalcogenides. *ACS Nano* 2017, **11** (2), 1588–1596.

(48) Jang, J.; Kim, Y.; Chee, S.-S.; Kim, H.; Whang, D.; Kim, G.-H.; Yun, S. J. Clean Interface Contact Using a ZnO Interlayer for Low-Contact-Resistance MoS<sub>2</sub> Transistors. *ACS Appl. Mater. Interfaces* 2020, **12** (4), 5031–5039.

(49) Kappera, R.; Voiry, D.; Yalcin, S. E.; Branch, B.; Gupta, G.; Mohite, A. D.; Chhowalla, M. Phase-engineered low-resistance contacts for ultrathin MoS<sub>2</sub> transistors. *Nat. Mater.* 2014, **13** (12), 1128–1134.

(50) English, C. D.; Shine, G.; Dorgan, V. E.; Saraswat, K. C.; Pop, E. Improved Contacts to MoS<sub>2</sub> Transistors by Ultra-High Vacuum Metal Deposition. *Nano Lett.* 2016, **16** (6), 3824–3830.

(51) Cui, Q.; Sakhidari, M.; Chamlagain, B.; Chuang, H.-J.; Liu, Y.; Cheng, M. M.-C.; Zhou, Z.; Chen, P.-Y. Ultrathin and Atomically Flat Transition-Metal Oxide: Promising Building Blocks for Metal–Insulator Electronics. *ACS Appl. Mater. Interfaces* 2016, **8**, 34552.

(52) Walmsley, T. S.; Andrews, K.; Wang, T.; Haglund, A.; Rijal, U.; Bowman, A.; Mandrus, D.; Zhou, Z.; Xu, Y.-Q. Near-infrared optical transitions in PdSe<sub>2</sub> phototransistors. *Nanoscale* 2019, **11** (30), 14410–14416.

(53) Lu, L.-S.; Chen, G.-H.; Cheng, H.-Y.; Chuu, C.-P.; Lu, K.-C.; Chen, C.-H.; Lu, M.-Y.; Chuang, T.-H.; Wei, D.-H.; Chueh, W.-C.; Jian, W.-B.; Li, M.-Y.; Chang, Y.-M.; Li, L.-J.; Chang, W.-H. Layer-Dependent and In-Plane Anisotropic Properties of Low-Temperature Synthesized Few-Layer PdSe<sub>2</sub> Single Crystals. *ACS Nano* 2020, **14** (4), 4963–4972.

CAS BIOFINDER DISCOVERY PLATFORM™

**ELIMINATE DATA SILOS. FIND WHAT YOU NEED, WHEN YOU NEED IT.**

A single platform for relevant, high-quality biological and toxicology research

**Streamline your R&D**

**CAS**

A division of the

American Chemical Society